Fターム[5F083JA38]の内容

半導体メモリ (164,393) | 材料 (39,186) | 電極材料、配線材料、バリア材料 (24,756) | 白金族元素、Au、及び、その合金 (2,740)

Fターム[5F083JA38]に分類される特許

101 - 120 / 2,740

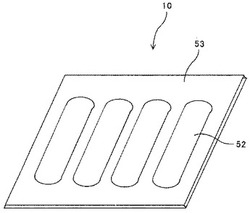

パターン形成用基板、圧電アクチュエータ製造方法、圧電アクチュエータ、液滴吐出ヘッド、および、液滴吐出装置

【課題】流動体を付着させて熱処理を行う工程を繰り返し行うことにより微細パターンの膜を所望の膜厚で精密に作製可能とするパターン形成用基板と、パターン形成用基板を用いた圧電アクチュエータの製造方法を提供する。

【解決手段】所定の流動体を特定領域に付着させて熱処理を行うことによりパターン化された膜を形成するためのパターン形成用基板10で、特定領域を親和性とし、それ以外の領域を非親和性とする表面改質をおこなう。パターン形成用基板10の表面改質処理対象となる金属膜はPt膜53を積層し、基体として、Ti,Ta,Zr,V,Nb,Mo,Wから選ばれる少なくとも1つの金属元素、酸素元素および炭素元素から構成されるMOC膜52を用いる。

(もっと読む)

記憶素子およびその製造方法ならびに記憶装置

【課題】低電流動作に優れると共に良好な保持特性を有する記憶素子および記憶装置を提供する。

【解決手段】本開示の記憶素子は、第1電極、記憶層および第2電極をこの順に有し、記憶層は、酸化物を含むと共に、第1電極側に設けられた抵抗変化層と、テルル(Te),硫黄(S)およびセレン(Se)のうちの少なくとも1種のカルコゲン元素および記憶層内の移動が容易な移動容易元素を含み、第1電極から第2電極に向かって移動容易元素の濃度分布を有する第1層と、記憶層内を移動しにくい移動困難元素を含む第2層とからなる単位イオン源層が少なくとも2層積層され、第2電極側に設けられたイオン源層とを備える。

(もっと読む)

メモリストリングにダイオードを有する3次元アレイのメモリアーキテクチャ

【課題】信頼でき、非常に小型の3次元集積回路メモリ用の構造を低い製造コストで提供する。

【解決手段】3次元アレイは第1の端部と第2の端部を含む2つの端部を有し、第1の端部と第2の端部の一方はビット線BLに接続され、第1の端部と第2の端部の他方はソース線CSLに接続される不揮発性メモリセルのNANDストリングのスタック1412、1413、1414と、ビット線BL及びソース線SLの一方をメモリセルのストリング1412、1413、1414に接続させるダイオード1492を有する。

(もっと読む)

強誘電体素子、インクジェット式記録ヘッド及びインクジェット式画像形成装置

【課題】エッチング残渣が少なく信頼性が良好であり、かつリーク電流を抑制することができる強誘電体素子を提供する。

【解決手段】シリコン基板10の上に順に、振動板11、下部電極20、強誘電体層30、上部電極40を形成し、強誘電体層30の側面の傾斜角はθ2=30°、上部電極40の側面の傾斜角はθ1=30°としている。これにより、エッチングガスやプラズマ粒子の衝突角度が平面に近づき、傾斜面でのエッチング残渣の除去率が向上する。

(もっと読む)

半導体装置

【課題】オフ状態のソース、ドレイン間のリーク電流の低いトランジスタを書き込みトランジスタに用いて、データを保存する半導体メモリ装置を提供する。

【解決手段】書き込みトランジスタのドレインと読み出しトランジスタのゲート、および、前記ドレインとキャパシタの一方の電極を接続した記憶セルを複数用いて形成されたマトリクスにおいて、書き込みトランジスタのゲートを書き込みワード線に、書き込みトランジスタのソースおよび読み出しトランジスタのソースをビット線に、読み出しトランジスタのドレインを読み出しワード線に接続する。ここで、書き込みトランジスタと読み出しトランジスタの導電型を異なるものとする。集積度を高めるために、バイアス線を他行の読み出しワード線で代用したり、記憶セルを直列に接続し、NAND構造とし、読み出しワード線と書き込みワード線を共用してもよい。

(もっと読む)

半導体装置

【課題】緻密で高耐圧な絶縁膜を提供することを目的とする。

【解決手段】基板上に半導体膜を有し、半導体膜上に第1の絶縁膜を有し、第1の絶縁膜上に導電膜を有し、導電膜上に第2の絶縁膜を有し、第1の絶縁膜は、第2の絶縁膜よりも緻密であり、第1の絶縁膜は、珪素と、酸素と、窒素とを有する。第1の絶縁膜は、希ガスを有し、その膜厚は、1nm以上100nm以下である。このような第1の絶縁膜はゲート絶縁膜として機能させる。

(もっと読む)

表示装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装

置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び

有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電

層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあ

わせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

半導体装置および半導体装置の制御方法

【課題】信頼性を確保しつつ、高速動作を実現することができる半導体装置を提供する。

【解決手段】抵抗変化素子10を有するメモリセル11と、メモリセル11に印加する電圧を制御する制御部80と、を備え、抵抗変化素子10は、第1の金属材料を含有する下部電極14と、第2の金属材料を含有する上部電極16と、酸素を含有する絶縁膜12と、を有しており、第1の金属材料は、第2の金属材料よりも規格化酸化物生成エネルギーが大きく、制御部80は、絶縁膜12の抵抗値を高抵抗化させる動作時および低抵抗化させる動作時において上部電極16に正電圧を印加し、絶縁膜12の抵抗値を読み出す動作時において下部電極14に正電圧を印加する。

(もっと読む)

半導体装置

【課題】電力供給がない状況で記憶保持が可能で、書き込み回数に制限が無い、新たな半導体装置を提供する。

【解決手段】チャネル領域と第1のゲート絶縁層と第1のゲート電極と第1のソース及びドレイン電極とを有する第1のトランジスタと、酸化物半導体層140と第2のソース電極142a及び第2のドレイン電極142bと第2のゲート絶縁層146と第2のゲート電極148aとを有する第2のトランジスタ162と、第2のソース電極142aまたは第2のドレイン電極142bの一方と第2のゲート絶縁層146と第2のゲート絶縁層146上に第2のソース電極142a又は第2のドレイン電極142bの一方と重なるように設けられた第3の電極148bとを有する容量素子164と、を有し、第1のゲート電極と第2のソース電極142a又は第2のドレイン電極142bの一方とは接続され、第3の電極148bは酸化物半導体層140と重なる領域を有する。

(もっと読む)

誘電体膜及びその製造方法、並びにキャパシタ

【課題】結晶粒のサイズを制御し、誘電体膜を貫通する結晶粒界やクラックの発生を抑制することによって、リーク電流の少ない高性能のキャパシタを提供する。

【解決手段】電極3,5の間に誘電体膜4が挟持されてなるキャパシタであって、誘電体膜4は、アルカリ土類金属と遷移金属との酸化物に、アルカリ土類金属の炭酸塩を0.1〜10mol%の範囲で含む。

(もっと読む)

信号処理回路及びその駆動方法

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる信号処理回路の提供する。

【解決手段】入力された信号の位相を反転させて出力する論理素子を2つ(第1の位相反転素子及び第2の位相反転素子)と、第1の選択トランジスタと、第2の選択トランジスタと、を有する記憶素子であって、酸化物半導体層にチャネルが形成されるトランジスタと容量素子との組を2つ(第1のトランジスタと第1の容量素子との組、及び第2のトランジスタと第2の容量素子との組)有する。そして、信号処理回路が有する記憶装置に上記記憶素子を用いる。例えば、信号処理回路が有するレジスタ、キャッシュメモリ等の記憶装置に上記記憶素子を用いる。

(もっと読む)

GeリッチなGST−212相変化材料

【課題】本発明の主な目的は、GeリッチなGST−212相変化材料を提供することにより、従来のGST−225の相変化メモリよりも高い結晶化温度、低いリセット電流要件及び優れた保持率を有することができる。

【解決手段】相変化材料は、Ge原子濃度xは、30%〜65%の範囲内にあり、Sb原子濃度yは、13%〜27%の範囲内にあり、Te原子濃度zは、20%〜45%の範囲内にある。このような材料のGeリッチな族も記載されている。そのような材料を含む集積回路に適したメモリデバイスは記載されている。

(もっと読む)

抵抗変化型不揮発性メモリ素子

【課題】遷移金属酸化物を用いた不揮発性メモリにおいて、メモリ抵抗の可逆的な変化を化学的変質によらない、メモリ抵抗変化の繰り返しに材料の劣化が起きにくい、メモリ抵抗変化の繰り返し特性に優れ、メモリ抵抗状態の安定した保持特性を有する抵抗変化型不揮発性メモリ素子を提供する。

【解決手段】抵抗変化型不揮発性メモリ素子として、第一電極2の金属Ptに、欠損があり導電性を有する強誘電酸化物Bi1-xFeO33を整流性接合し、さらに第二電極4にオーミック接合して、第一電極と第二電極の間に電圧を印加して、Bi1-xFeO3層に電気分極反転を起こして安定したメモリ抵抗変化を実現した。

(もっと読む)

半導体装置

【課題】酸化物半導体層を含むトランジスタを有する不揮発性メモリにおいて、保持された情報を容易に消去できる不揮発性メモリを提供する。

【解決手段】第1のトランジスタ及び第2のトランジスタを有するメモリセルを有し、第1のトランジスタは第1のチャネル、第1のゲート電極、第1のソース電極及び第1のドレイン電極を有し、第2のトランジスタは酸化物半導体からなる第2のチャネル、第2のゲート電極、第2のソース電極及び第2のドレイン電極を有し、第2のソース電極及び第2のドレイン電極の一方は第1のゲート電極と電気的に接続され、メモリセルへの情報の書き込み及び消去は、第2のソース電極及び第2のドレイン電極の一方と、第1のゲート電極との間のノードの電位を高くすることにより情報が書き込まれ、第2のチャネルに紫外線を照射して、ノードの電位を低くすることにより情報が消去される不揮発性メモリによって解決する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いたトランジスタ(より広義には、十分にオフ電流が小さいトランジスタ)を用いた記憶回路と、酸化物半導体以外の材料を用いたトランジスタ(換言すると、十分な高速動作が可能なトランジスタ)を用いた駆動回路などの周辺回路と、を一体に備える半導体装置とする。また、周辺回路を下部に設け、記憶回路を上部に設けることで、半導体装置の面積の縮小化及び小型化を実現することができる。

(もっと読む)

半導体装置の製造方法

【課題】非晶質炭素膜を用いて形成する電極のアスペクト比を増大させる。

【解決手段】半導体装置の製造方法は、半導体基板上に第1非晶質炭素膜を形成し、周辺回路領域の第1非晶質炭素膜を除去してメモリセル領域の第1非晶質炭素膜を第2非晶質炭素膜とし、第2非晶質炭素膜を覆う第1シリコン酸化膜を基板全面に形成し、第2非晶質炭素膜上の第1シリコン酸化膜を除去して周辺回路領域の第1シリコン酸化膜を第2シリコン酸化膜とし、第2非晶質炭素膜と第2シリコン酸化膜を覆う第1絶縁膜を形成し、第1絶縁膜に第1開口を形成し、第1開口を埋め込む第2絶縁膜を形成し、第2絶縁膜に第2開口を形成し、第2開口と第1開口が重なる位置に露出する第2非晶質炭素膜にホールを形成し、ホール内に下部電極を形成し、第2絶縁膜を除去して第1開口内に第2非晶質炭素膜を露出させ、露出した第2非晶質炭素膜を全て除去する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造において基板の金属汚染を抑える。

【解決手段】半導体素子が設けられた基板の、半導体素子形成面とは反対側の裏面および端部に保護膜を形成する工程と、前記半導体素子形成面に設けられた金属含有膜を加工する工程と、前記金属含有膜の加工後に前記保護膜を除去する工程と、を含む半導体装置の製造方法。

(もっと読む)

半導体記憶装置

【課題】低電圧化を可能にする。

【解決手段】実施形態は、第1の配線と、その上に積層されたメモリセルと、その上に第1の配線と交差するように形成された第2の配線とを有するセルアレイ層を備え、メモリセルが極性の異なる電気信号が印加されることにより電気的書き換えが可能な可変抵抗素子及び可変抵抗素子に双方向の電流を流す電流制御素子を直列に接続してなる。電流制御素子は、i型半導体とその両側に接する第1及び第2導電型半導体とを有する。第2導電型半導体中の第2の不純物の拡散長は第1導電型半導体中の第1の不純物の拡散長より長く、第1導電型半導体とi型半導体との接合部に、第2導電型半導体とi型半導体との接合部よりも多くのインパクトイオンを発生させるインパクトイオン化促進部が形成される。

(もっと読む)

抵抗変化型メモリデバイスおよびその動作方法

【課題】ビット線側での素子電流による高い制御性を維持しながらも、低抵抗化動作の高速化を実現する抵抗変化型メモリデバイスを提供する。

【解決手段】ビット線BLに接続されて第1電流I1を流す初期電流駆動部55(N4)と、ビット線BLに対し初期電流駆動部55と並列に接続されて、第2電流I2を制御する素子電流制御部52とを有する。そして、初期電流駆動部55と素子電流制御部52の各NMOSトランジスタN4,N3を差動制御して、BL電流の値をI1からI2に切り替える。

(もっと読む)

ニッケル酸ランタン膜形成用組成物の製造方法、ニッケル酸ランタン膜の製造方法、及び圧電素子の製造方法

【課題】特殊な環境が不要で短時間且つ低コストでニッケル酸ランタン膜形成用組成物を製造することができるニッケル酸ランタン膜形成用組成物の製造方法、ニッケル酸ランタン膜の製造方法、及び圧電素子の製造方法を提供する。

【解決手段】少なくとも酢酸ランタン、酢酸ニッケル、酢酸、及び水を混合して混合溶液を得た後、混合溶液を加熱する。

(もっと読む)

101 - 120 / 2,740

[ Back to top ]