Fターム[5F083MA18]の内容

Fターム[5F083MA18]に分類される特許

21 - 40 / 481

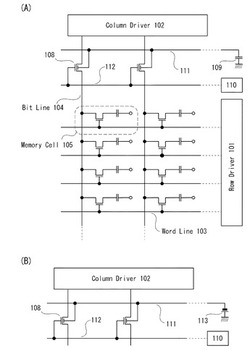

半導体メモリ装置

【課題】酸化物半導体のようなバンドギャップが大きな半導体を用いたメモリ装置の保持特性を高める。

【解決手段】ビット線の一端にバックゲートを有するトランジスタ(バックゲートトランジスタ)を直列に挿入し、そのバックゲートの電位は常に十分な負の値となるようにする。また、ビット線の最低電位はワード線の最低電位よりも高くなるようにする。電源が切れた際には、ビット線はバックゲートトランジスタによって遮断され、ビット線に蓄積された電荷が流出することが十分に抑制される。この際、セルトランジスタのゲートの電位は0Vであり、一方で、そのソースやドレイン(ビット線)の電位は、ゲートよりも十分に高いので、セルトランジスタは十分なオフ状態であり、データを保持できる。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の占有面積を実質的に減少させる。

【解決手段】半導体装置は、第1の方向及びそれと交差する第2の方向に沿って半導体基板上に配列形成された複数の第1の接続領域と、複数の第1の接続領域を第1の方向に沿った列ごとに電気的に接続する複数の配線とを含む。複数の配線は、第2の方向に隣り合う2つの配線が互いに異なる配線層に配置され、かつ平面視において一部が重なってハニカム状に見えるように屈曲させてある。

(もっと読む)

メモリ装置

【課題】メモリセルの占有面積が小さいメモリ装置、また、メモリセルの占有面積が小さく、データ保持期間の極めて長いメモリ装置を提供する。

【解決手段】ビット線と、容量素子と、該ビット線上に設けられた溝部を有する第1の絶縁層と、一部が該溝部の底部で該ビット線と電気的に接続し、他の一部が該第1の絶縁層の上面で該容量素子の一方の電極と電気的に接する半導体層と、該半導体層と接する第2の絶縁層と、該第2の絶縁層と接するワード線と、を有する構成のメモリ装置とする。

(もっと読む)

半導体装置

【課題】フローティングボディにデータを記憶するメモリセルを備えた半導体装置において、トリガ素子となる能動素子を設けなくともメモリセルの導通、非導通状態を確実に制御する。

【解決手段】ビット線BLと、ワード線WLと、第1の端子がビット線に接続され、第2の端子がワード線に接続されたメモリセル66と、メモリセルに対するデータの書込み時に、書込みデータの如何に係わらず、ビット線とワード線を選択し、メモリセルを導通させた後、ビット線の電圧レベルを書込みデータに応じた電圧レベルに設定し、メモリセルにデータを書込む制御回路を備える。

(もっと読む)

記憶装置

【課題】データを保持する期間を確保しつつ、単位面積あたりの記憶容量を高めることが

できる記憶装置の提案を目的の一とする。

【解決手段】記憶素子と、記憶素子における電荷の蓄積、保持、放出を制御するための、

酸化物半導体を活性層に含むトランジスタと、記憶素子に接続された容量素子とを有する

記憶装置。上記容量素子が有する一対の電極の少なくとも一方は、遮光性を有している。

さらに、上記記憶装置は遮光性を有する導電膜或いは絶縁膜を有しており、上記活性層が

、遮光性を有する電極と、遮光性を有する導電膜或いは絶縁膜との間に位置する。

(もっと読む)

強誘電体キャパシタ

【課題】還元性雰囲気による特性劣化を抑制することができる構造の強誘電体キャパシタを提供する。

【解決手段】強誘電体キャパシタ積層構造8は、強誘電体膜3と、強誘電体膜の一方表面に接する下部電極2と、強誘電体膜3の他方表面に接する上部電極4とを含む。上部電極4および下部電極2のうちのうちの少なくともいずれか一方が、酸化物導電体層と金属層とを交互に積層した積層電極構造を有している。この積層電極構造は、酸化物導電体層および金属層のうちの少なくともいずれか一方を2層以上含む。

(もっと読む)

ルチル結晶構造を備えた酸化チタン膜の製造方法

【課題】高温のアニールを必要とせずに、誘電率の高いルチル結晶構造の酸化チタン膜を形成する。

【解決手段】非晶質の酸化ジルコニウム膜上に、チタンプリカーサとしてメチルシクロペンタジエニルトリスジメチルアミノチタンを用いてALD法により非晶質の酸化チタン膜を形成し、300℃以上の温度でアニールして結晶化することでルチル結晶構造を有する酸化チタン膜が得られる。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリおよび容量素子を有する半導体装置の性能を向上させる。

【解決手段】同一の半導体基板1上に、不揮発性メモリのメモリセルMCと容量素子とが形成されている。メモリセルMCは、半導体基板の上部に絶縁膜3を介して形成された制御ゲート電極CGと、半導体基板1の上部に形成されて制御ゲート電極CGと隣合うメモリゲート電極MGと、メモリゲート電極MGと半導体基板1との間および制御ゲート電極CGとメモリゲート電極MGとの間に形成されて内部に電荷蓄積部を有する絶縁膜5とを有している。容量素子は、制御ゲート電極CGと同層のシリコン膜で形成された下部電極と、絶縁膜5と同層の絶縁膜で形成された容量絶縁膜と、メモリゲート電極MGと同層のシリコン膜で形成された上部電極とを有している。そして、上部電極の不純物濃度は、メモリゲート電極MGの不純物濃度よりも高くなっている。

(もっと読む)

半導体デバイス及びその製造方法

【課題】エッチング選択比の高い非晶質炭素膜を用いたシリンダ型キャパシタを有する半導体デバイスでは、非晶質炭素膜を除去する際に、キャパシタの下部電極に変形が生じやすい。

【解決手段】非晶質炭素膜及び層間絶縁膜をメモリセル領域及び周辺回路領域にそれぞれ形成し、非晶質炭素膜及び層間絶縁膜上に絶縁膜を形成し、非晶質炭素膜上のキャパシタに対応した部分における絶縁膜を除去して、キャパシタの下部電極を両側から支持すると共に、メモリセル領域から周辺回路領域まで連続的に覆う絶縁膜パターンを形成する。続いて、非晶質炭素膜を用いたキャパシタを形成した後、絶縁膜パターン下部の非晶質炭素膜を除去する。

(もっと読む)

強誘電体キャパシタの製造方法及び強誘電体キャパシタ

【課題】強誘電体膜の表面に現れた窪みを、強誘電体材料で効率的に埋め込むことが可能な強誘電体キャパシタの製造方法を提供する。

【解決手段】基板10の上に第1導電膜11を形成する。第1導電膜11の上に、表面に複数の凹部15が形成された第1強誘電体膜12を形成する。第1強誘電体膜12の表面の凹部15を埋め込むように、第1強誘電体膜12の上に、原子層堆積法により第2強誘電体膜13を形成する。第2強誘電体膜13の上に、第2導電膜17を形成する。

(もっと読む)

半導体装置および配線レイアウト方法

【課題】配線間のピッチを縮小可能にした半導体装置を提供する。

【解決手段】半導体基板に形成された複数のトランジスタと、第1の方向に延在する第1の配線を備えた第1の配線層と、第1の配線層よりも上層に設けられ、第1の方向と交差する第2の方向に延在し、第1の配線と電気的に接続された第2の配線を備えた第2の配線層と、半導体基板と第1の配線層との間に設けられ、複数のトランジスタに接続する第1の中継配線と、第1の中継配線が形成された第1の中継配線層と第1の配線層との間に設けられ、第1の配線と複数のトランジスタのうちの一つとを接続する第2の中継配線とを有する構成である。

(もっと読む)

半導体装置

【課題】DRAM回路などのように容量を内蔵する半導体装置において、コンタクト容量およびコンタクト抵抗を増加させることなく、容量の容量値を増加させる。

【解決手段】セルコンタクトが形成されるセルコンタクト部にまで容量の形成場所を延長することで、容量値のさらなる増大が可能となる。なお、容量部、容量コンタクト部およびセルコンタクト部にまたがる容量の形成には、ALD法などによるスパッタ装置を用いることが好ましい。

(もっと読む)

半導体装置及びその製造方法

【課題】プラグ形成時に位置ずれが発生しても水分や不純物が溜まる窪みが発生することがなく、微細化しても長期間にわたる信頼性を確保できる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、第1の絶縁膜121の上に形成された強誘電体キャパシタ131と、強誘電体キャパシタ131を覆う第2の絶縁膜311及びエッチングストッパ膜312と、エッチングストッパ膜312の上面からトランジスタTの不純物領域に到達する第1のコンタクトホール内に導電体材料を充填して形成された第1のプラグ313と、エッチングストッパ膜の上に形成された第3の絶縁膜314と、第3の絶縁膜314の上面から第1のプラグに到達する第2のコンタクトホール内に導電体材料を充填して形成された第2のプラグ315とを有する。

(もっと読む)

電界効果トランジスタおよびそれを用いたメモリおよび半導体回路

【課題】微細化した半導体集積回路において用いられる、オフ電流の小さな電界効果トランジスタ(FET)を提供する。

【解決手段】絶縁表面に略垂直に形成された厚さが1nm以上30nm以下の薄片状の酸化物半導体と、前記酸化物半導体を覆って形成されたゲート絶縁膜と、前記ゲート絶縁膜を覆って形成されたストライプ状の幅10nm以上100nm以下のゲートを有する電界効果トランジスタ。この構成では、薄片状の酸化物半導体の三方の面をゲートが覆うこととなるため、ソース、ドレインから注入される電子を効率的に排除し、ソースとドレインの間をほぼ空乏化領域とでき、オフ電流を低減できる。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、接合リーク電流を低減可能で、かつトランジスタの信頼性を向上させることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】ゲート電極61よりも上方に配置されたゲート絶縁膜21、及びゲート電極61の上面61aを覆う水素含有絶縁膜62と、水素含有絶縁膜62を介して、ゲート電極用溝17の上部17Bを埋め込むフッ素含有絶縁膜63と、を備え、ゲート絶縁膜21と接触する第1及び第2の不純物拡散領域65,66の面に、半導体基板13に含まれるシリコンと水素含有絶縁膜62に含まれる水素とが結合したSi−H結合、及び半導体基板13に含まれるシリコンとフッ素含有絶縁膜63に含まれるフッ素とが結合したSi−F結合を有する。

(もっと読む)

半導体装置の製造方法

【課題】サポート膜で保持されたシリンダ型電極を有するキャパシタを形成する際に、シリンダホール形成時にデフォーカスの発生したウエハエッジ部において、シリンダ型電極を形成する際の型材となるコア絶縁膜を除去すると、パターンとびが発生する。

【解決手段】コア絶縁膜26を除去するために形成するサポート膜27の開口部をデフォーカスの発生したウエハエッジ部では形成せず、好ましくは通常露光部のマット幅Maよりも大きなマット幅Mbとなるように形成し、ウエハエッジ部のサポート膜27下にコア絶縁膜26が残るようにする。

(もっと読む)

半導体メモリ装置および半導体メモリ装置の作製方法

【課題】高度に集積化したゲインセル方式の半導体メモリを提供する。

【解決手段】第1絶縁体101、読み出しビット線102b、第2絶縁体103、第3絶縁体103、第1半導体膜105、第1導電層107a乃至107d等を形成し、その上に凸状絶縁体112を形成する。そして、凸状絶縁体112を覆って、第2半導体膜114a、114bと第2ゲート絶縁膜115を形成する。その後、導電膜を形成し、これを異方性エッチングすることで、凸状絶縁体112の側面に書き込みワード線116a、116bを形成し、凸状絶縁体112の頂部に書き込みビット線125へ接続するための第3コンタクトプラグ124を形成する。このような構造でメモリセルの面積を最小で4F2とできる。

(もっと読む)

メモリセルキャパシタ構造におけるメモリセルキャパシタプレートの形成方法

【課題】酸素にさらされても絶縁膜を形成しない材料からメモリセルキャパシタプレートを製造するための形成方法を提供する。

【解決手段】メモリセルキャパシタプレートの形成方法は、犠牲層を堆積する工程と、その犠牲層内に開口部を形成する工程とを含む。続いて、酸素にさらされても相当の導電性を維持する導電性料を含む電極材料層702を、犠牲層の上面に堆積し、開口部の少なくとも一部を充填する。次に、電極材料層702の一部を少なくとも犠牲層の上面と同じ略同じ高さにまで除去することによりメモリセルキャパシタプレートの上面を画定し、その後、犠牲層を除去する。

(もっと読む)

半導体メモリ装置

【課題】DRAMに必要なキャパシタの容量を低減し、高度に集積化したDRAMを提供する。

【解決手段】分割ビット線型DRAMにおいて、サブビット線をワード線の下に形成し、ビット線をワード線の上に形成する。分割ビット方式でサブビット線の寄生容量が低減し、かつ、セルトランジスタのオフ抵抗を必要に応じて高いものとすることによって、キャパシタの容量を通常のDRAMの1/10以下とすることができる。このため、スタック型キャパシタであっても、その高さを従来のものの1/10以下とできるので、その上にビット線を設けることも容易となる。また、セルトランジスタの構造を特殊なものとすることでメモリセルあたりの面積を4F2とできる。

(もっと読む)

キャパシタおよび半導体装置

【課題】微細化した半導体集積回路において用いられるキャパシタを提供する。

【解決手段】誘電体の一つの面に接して設けられた、インジウム、錫あるいは亜鉛の少なくとも一つと窒素とを有する仕事関数が5.0電子ボルト以上、好ましくは5.5電子ボルト以上のn型半導体による電極を有するキャパシタである。電極の仕事関数が高いため、誘電体のポテンシャル障壁が高くなり、誘電体が10nm以下と薄くても十分な絶縁性を保てる。特に、誘電体が、high−k材料である場合に顕著な効果が認められる。

(もっと読む)

21 - 40 / 481

[ Back to top ]