Fターム[5F083MA19]の内容

Fターム[5F083MA19]の下位に属するFターム

拡散層とビット線 (1,521)

Fターム[5F083MA19]に分類される特許

2,361 - 2,373 / 2,373

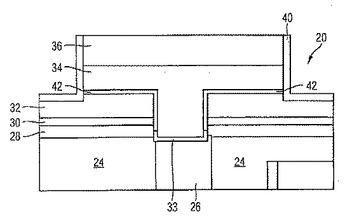

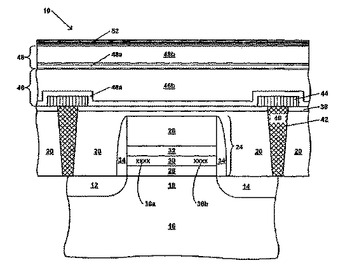

半導体構成のための電気的接続を形成する方法

本発明は、半導体構成に関連して電気的接続を形成する方法を含む。その上に導電線路を有し、導電線路に隣接して少なくとも2つの拡散領域を有する半導体基板が設けられる。パターン化されるエッチ・ストップが拡散領域の上に形成される。パターン化されるエッチ・ストップは、開口を貫通して延びる1対の開口を有し、開口は導電線路の軸に実質的に平行に一列に並んでいる。絶縁材料がエッチ・ストップ上に形成される。絶縁材料は、絶縁材料内にトレンチを形成し且つ開口をエッチ・ストップから拡散領域まで延ばすために、エッチングに対して露出される。トレンチの少なくとも一部分は開口の直上にあり、線路の軸に沿って延びる。導電材料が開口内とトレンチ内に形成される。  (もっと読む)

(もっと読む)

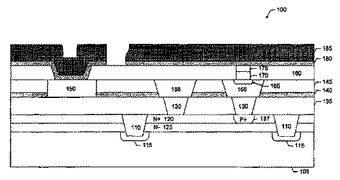

相変化材料を含む電気デバイス

本発明に係る電気デバイス(100)は、第1の電気抵抗率を有する第1の相と第1の電気抵抗率と異なる第2の電気抵抗率を有する第2の相との間で変化可能な相変化材料からなる層(7,107)を備えるレジスタを有している。上記相変化材料は高速成長材料である。電気デバイス(100)は、相変化材料からなる層(7,107)の対応する部分を第1の相から第2の相へ変化させることにより少なくとも三つの異なる電気抵抗値間で抵抗を切り換えるための切換信号生成器(400)を更に備えている。  (もっと読む)

(もっと読む)

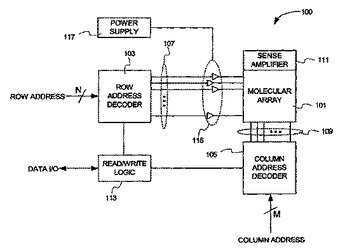

分子メモリデバイスおよび方法

スイッチングデバイスと、前記スイッチングデバイスに結合された少なくとも第1のビット線および第1のワード線と、それぞれがビット線およびワード線に結合された記憶位置のアレイとを具備する分子メモリ素子であって、前記素子は、レドックス活性分子を含む記憶分子を有する第1の電極を具備し、前記アレイは、第2の電極を具備する。

(もっと読む)

(もっと読む)

半導体装置、半導体装置の製造方法

本発明では、水素またはH2Oの拡散を防止することで強誘電体キャパシタの劣化を防止し、高品質の強誘電体キャパシタを有する半導体装置を提供することを課題とする。そのため、本発明では、基板上に形成された強誘電体キャパシタと、前記強誘電体キャパシタ上に形成された配線構造とを有する半導体装置であって、前

記配線構造は、層間絶縁層と当該層間絶縁層中に形成されたCu配線部を含み、前記層間絶縁層に面するように、水素拡散防止層を含むエッチングストッパー層が形成されていることを特徴とする半導体装置を用いた。  (もっと読む)

(もっと読む)

記憶素子、メモリ回路、半導体集積回路

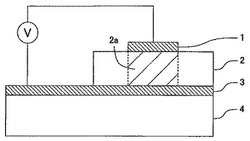

【解決手段】第1の可変抵抗(5)は、第1の端子(7)と第3の端子(9)との間に接続され、第1の端子(7)と第3の端子(9)との間に印加されるパルス電圧の極性に応じてその抵抗値を増加/減少させる。第2の可変抵抗(6)は、第3の端子(9)と第2の端子(8)との間に接続され、第3の端子(9)と第2の端子(8)との間に印加されるパルス電圧の極性に応じてその抵抗値を増加/減少させる。第1の端子(7)と第3の端子(9)との間および第3の端子(9)と第2の端子(8)との間に所定のパルス電圧を印加して第1および第2の可変抵抗(5,6)の抵抗値を可逆的に変化させることにより1ビットあるいは多ビットの情報を記録する。 (もっと読む)

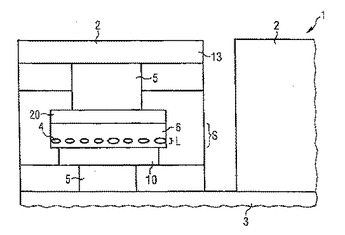

半導体集積メモリーおよび半導体集積メモリーの製造方法

本発明は、2つの電極(10,20)間に配置された記憶媒体(6)を備えた半導体集積メモリー(1)に関する。上記記憶媒体(6)は、例えば相変化媒体であってもよい。記憶媒体(6)は、電流によって第1状態または第2状態に設定される。その結果、情報項目を記憶させることができる。本発明によれば、材料(4)からなる不純物粒子が注入された面(L)が設けられている。その結果、記憶媒体における電流密度が局部的に上昇し、プログラミングのために必要とされるプログラミング電流を低減できる。その結果、相変化媒体を含むメモリー素子の電流消費を低減できる。したがって、相変化媒体を含むメモリー素子を、トランジスタなどの他の部品と共に、最小構造寸法で実施することができ、単一の半導体回路に集積することができ、別個のサブ回路に配置する必要がなくなる。  (もっと読む)

(もっと読む)

強誘電体キャパシタデバイスおよびFeRAMデバイス

1つ以上のコンタクトプラグが通過して延びている基板と、上記基板上に形成された第1の層間絶縁膜とから、強誘電体キャパシタデバイス(例えばFeRAMデバイス)が形成されている。上記第1の層間絶縁膜上にはスペーサ層が形成されていて、このスペーサ層上には第1の酸素バリア層が形成されていて、この第1の酸素バリア層上にはバッファ層が形成されている。上記バッファ層上において、上記バッファ層と上記コンタクトプラグとの間に下地材料の層が形成されていて、第1の電極と第2の電極との間に誘電体層が挟まれている。上記デバイスに第2の酸素バリア層が塗布される。上記スペーサ層があれば、上記下地材料と上記コンタクトプラグとの界面まで酸化が及ぶことが抑制される。なぜなら、上記界面が、上記第1の酸素バリア層の下に位置しているからである。この結果、電気コンタクトが破損することはない。  (もっと読む)

(もっと読む)

ビア開口部中に形成されるポリマーメモリデバイス

本発明は、ビア内にポリマーメモリデバイスを製造する方法に関する。この方法は、少なくとも1つの金属を含む層をその上に備える半導体基板を提供するステップと、この金属を含む層中に少なくとも1つの銅コンタクトを形成するステップと、銅コンタクト上に少なくとも1つの絶縁層を形成するステップと、絶縁層に少なくとも1つのビアを形成し、銅コンタクトの少なくとも一部を露出するステップと、ビアの下側部分にポリマー材料を形成するステップと、ビアの上側部分にトップ電極材料層を形成するステップとを含む。  (もっと読む)

(もっと読む)

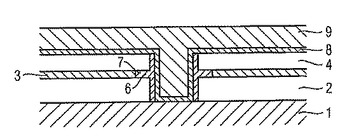

デバイス内にバリア層を有するコンタクトホールを形成する方法及び得られるデバイス

デバイスの下層(2)にコンタクトを形成する方法は、コンタクトホール(5)を形成するステップと、デバイスのコンタクトホール内にバリア材からなるコンタクトホールバリア層(7)を形成するステップと、コンタクトホールの底面のコンタクトホールバリア層をエッチングするステップと、コンタクトホール内にライナ材(8)を堆積するステップと、コンタクトホールに導電性材料(9)を充填するステップとを有する。半導体、受動素子、キャパシタ又はFeRAMなどのデバイスが上記方法に従って形成される。コンタクトホールの側壁にあるコンタクトホールバリア層(7)が、水素及び/又は酸素の側方拡散を抑制する。コンタクトホールバリア層は、ウェットエッチングプロセスによって生じる既存のバリア層(3)内のボイド(6)を充填するために上記プロセス後に、又は既存のバリア層への損傷を抑制するために上記プロセス前に行うことができる。

(もっと読む)

(もっと読む)

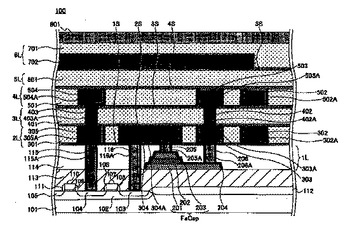

1T‐nメモリセル積層構造体

本発明は、クロスポイントと1T‐1セルとの双方の設計に基づくある種の利点を導入するためのメモリ技術及びメモリアレイに関する新規な変更に関する。これらの設計のある特徴を組み合わせることにより、1T‐1セル設計における読出し時間の高速化及び信号対雑音比の増大と、クロスポイント設計における高記録密度化との双方が達成される。そのために、単一のアクセストランジスタ16を用いて、“Z”軸方向に配置された複数のメモリアレイ層で垂直方向に互いに上下に積み重ねうる多重メモリセルを読出すようにする。  (もっと読む)

(もっと読む)

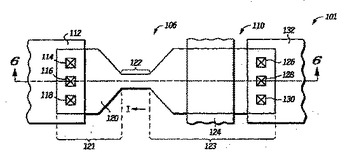

フューズ及びその形成方法

アクティブフューズはアクティブフューズ構造(120)を備え、この構造を使用して可変抵抗体(106)及び選択トランジスタ(110)の双方を形成する。一の実施形態では、アクティブフューズ構造は、半導体基板(140)の活性領域(160)の一部に形成され、選択ゲート(124)はアクティブフューズ構造の一方の端部(123)の上に配置されてアクティブフューズへの書き込みに使用する一体型選択トランジスタ(110)を形成する。共有型のアクティブフューズ構造を活性領域の内部に使用することによって、面積要件を縮小し、かつ検出マージンを大きくすることができる。  (もっと読む)

(もっと読む)

BEOLプロセスにおいて、UVによって誘発されたSONOSデュアルビットのフラッシュメモリデバイスの電荷を低減するUVブロック層

SONOSフラッシュメモリセル(24)をUVにより誘発される電荷から保護する方法であって、SONOSフラッシュメモリセル(24)を半導体デバイス(10、50)に製造するステップと、SONOSフラッシュメモリセル(24)上に、少なくとも1つのUV保護層(38、46、48、又は52)を蒸着させるステップとを含み、UV保護層には実質的にUV不透過性の材料が含まれる。SONOSフラッシュメモリセル(24)と、少なくとも1つのUV保護層(38、46、48又は52)(UV保護層には実質的にUV不透過性の材料が含まれる)を含むSONOSフラッシュメモリデバイス(10、50)が提供される。  (もっと読む)

(もっと読む)

半導体記憶装置及びその製造方法

【課題】ビット線とセルコンタクト部の容量接続用コンタクトとのショートを防止し、容量接続用コンタクトとビット線とのマージンを大きくすることができる半導体記憶装置及びその製造方法の提供。

【解決手段】STIにより活性領域が分離形成された半導体基板上の第1の層間絶縁膜4に活性領域まで貫通するコンタクト孔5を設け、その内部に第1の層間絶縁膜上面よりも低い位置まで多結晶シリコン6を充填した後、多結晶シリコン上部にシリサイド膜12を形成し、第1の層間絶縁膜上の所定領域にポリサイド膜又はメタル膜を含むビット線7とビット線の上面及び側面にシリコン窒化膜を形成した後、ビット線で覆われていないコンタクト孔内部のシリサイド膜を除去することにより、シリンダ型容量と接続されるコンタクト孔内部の導電体とそのコンタクト孔に隣接するビット線とを分離する。その後、第2の層間絶縁膜10を堆積し、シリサイド膜を除去したコンタクト孔まで貫通するシリンダ型容量パターンを形成する。

(もっと読む)

2,361 - 2,373 / 2,373

[ Back to top ]