Fターム[5F083NA01]の内容

Fターム[5F083NA01]に分類される特許

1,801 - 1,820 / 3,470

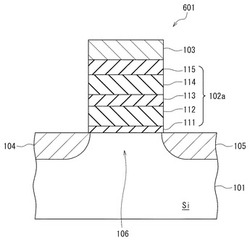

MOS型半導体メモリ装置

【課題】優れたデータ保持特性と、高速でのデータ書換え性能と、低消費電力での動作性能と、高い信頼性と、を同時に兼ね備えた不揮発性MOS型半導体メモリ装置を提供する。

【解決手段】MOS型半導体メモリ装置601は、大きなバンドギャップを持つ第1の絶縁膜111および第5の絶縁膜と、最も小さなバンドギャップを持つ第3の絶縁膜113との間に、両者の中間の大きさのバンドギャップを持つ第2の絶縁膜112および第4の絶縁膜114を備えている。このようなエネルギーバンド構造を有することにより、データ書き込み時には第1の絶縁膜111を介した電荷の移動が起こりやすく、書き込み動作速度を高速化することが可能で、かつ絶縁膜積層体に電荷を注入するために必要な書き込み電圧を小さく抑えることができる。

(もっと読む)

半導体装置の製造方法

【課題】ゲート酸化膜へのプラズマダメージを抑制することができ、ゲート酸化膜の劣化が抑制されるとともにスループットが向上した半導体装置の製造方法を提供する。

【解決手段】本発明にかかる半導体装置の製造方法において、プラズマ絶縁膜を形成する工程は、成膜装置内において、成膜ガスを供給しながら、高周波電界および低周波電界を印加してFET形成領域を覆う前記プラズマ絶縁膜を成膜する工程と、前記プラズマ絶縁膜を成膜した後、前記高周波電界の印加を継続しながら、前記低周波電界の印加を停止した後または同時に前記成膜ガスの流量を経時的に漸次減少させる工程と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチゲートトランジスタにおいて、溝に埋め込まれたゲート電極とゲート絶縁膜との界面にボイドが形成されることを防止する。

【解決手段】半導体基板1に埋め込まれた素子分離絶縁膜3により絶縁分離された活性領域4と、ゲート絶縁膜5を介して活性領域4上を跨ぐように形成されたゲート電極6と、ゲート電極6を挟んだ両側の活性領域4に形成されたソース領域7a及びドレイン領域7bとを有し、活性領域4に溝8が設けられて、この溝8の内側にゲート絶縁膜5を介してゲート電極6の一部が埋め込まれてなるトレンチゲートトランジスタ51を備える半導体装置であって、溝8が少なくとも上端開口部よりも下部側において幅広となる形状を有し、溝8に埋め込まれたゲート電極6内に外殻層13aで覆われた中空部(ボイド)14が設けられている。

(もっと読む)

半導体デバイスの製造方法およびそれによって得られる半導体デバイス

基板(4)上に半導体デバイスを製造する方法は、基板(4)のメモリ領域(1)に不揮発性メモリ(10)を形成することを含む。基板(4)への不揮発性メモリ形成は、メモリ領域(1)に、浮遊ゲート構造と、制御ゲート構造とを形成することを含む。制御ゲート構造は、浮遊ゲート構造とともに積層型構造に位置する。1以上のゲート材料層は、基板(4)の論理領域(3)に形成される。制御ゲート構造とゲート材料層の形成後、充填材料層(130、130’)は論理領域(3)とメモリ領域(1)に堆積される。論理領域(3)とメモリ領域(1)に位置する充填材料の厚さを、1以上のゲート材料層の表面が少なくとも露出するまで薄くすることによって、充填材料層(130、130’)は除去される。論理デバイスは論理領域(3)に形成され、論理デバイスの形成は、ゲート材料層から論理ゲート構造を形成することを含む。  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】リードディスターブ特性を向上させて、高集積化された半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、少なくとも一つの制御端子を有し、電気的に消去可能で、離散的なn値(nは2以上の整数)のデータを記憶する情報蓄積部を有し、少なくとも二つの電流端子間に配置されたメモリエレメントM0〜M15を複数個備え、n値のデータを閾値の低い順に定められた離散的な第1乃至第nのすべての閾値電圧が、データ読み出し時に電流端子に印加される電圧のうち低い方の電圧に比べて高く、このメモリエレメントと電流端子を共有して配置され、電流端子間の導通状態と遮断状態とが切り替わる制御端子の電圧を閾値とすると、n値のデータを閾値の低い順に定められた離散的な第1乃至第nのすべての閾値電圧よりも低い閾値電圧を有する選択エレメントS1を備える。

(もっと読む)

非揮発性メモリのための高効率ホットキャリア注入プログラミングの方法及び構造

【課題】 プログラミング効率を向上させた非揮発性メモリのためのプログラミングの方法及び構造を提供する。

【解決手段】 非揮発性メモリセル内の酸化膜半導体電界効果トランジスタ(MOSFET)は、ソースと、ドレインと、ソースとドレイン間のチャネル領域とを有し、これら全てがソース及びドレインの導電型と逆導電型の基板内に形成されている。MOSFETは、ドレイン電極を非揮発性メモリセルに供給される主電圧Vccの供給源に接続しかつ、ソースからドレインの方へ延在するチャネル領域の一部を反転させるようにソース及び基板へ選択された電圧を供給することによって、プログラミングされる。チャネル領域の反転部分は、ドレインに達する前にピンチオフ点で終わる。ソース−基板間のPN接合の逆バイアスを制御することによって、反転領域のピンチオフ点がソースの方へ引き戻され、それによってMOSFETのプログラミング効率を増大させる。

(もっと読む)

タングステン材料の原子層堆積法

【課題】ALDプロセスを使用して、均一性が良好で、ほとんどまたは全く汚染がなく、かつ導電率が高いつまり抵抗率が低いタングステン含有材料を堆積するための改良されたプロセスを提供する。

【解決手段】一実施形態では、プロセスチャンバ内に基板を位置決めするステップであって、該基板がこの上に配置されている下地層を含有するステップと、該基板をタングステン前駆体および還元ガスに順次曝してALDプロセス時に該下地層上にタングステン核形成層を堆積するステップであって、該還元ガスが約40:1、100:1、500:1、800:1、1,000:1以上の水素/ハイドライド流量比を含有するステップと、該タングステン核形成層上にタングステンバルク層を堆積するステップとを含む、基板上にタングステン含有材料を形成するための方法が提供される。該還元ガスはジボラン、シランまたはジシランなどのハイドライド化合物を含有している。

(もっと読む)

コンタクトスペーサを備えるコンタクト構造体の形成方法及びそれを用いた半導体素子の製造方法

【課題】コンタクトスペーサを備えるコンタクト構造体の形成方法及びそれを用いた半導体素子の製造方法を提供する。

【解決手段】本発明のコンタクト構造体の形成方法は、半導体基板上に層間絶縁膜を形成する工程と、層間絶縁膜をパターニングして半導体基板の所定領域を露出させるコンタクトホールを形成する工程と、半導体基板の主表面に対して傾斜した蒸着方向を有する蒸着法を用いてコンタクトホールの側壁にコンタクトスペーサを形成する工程と、を有する。このとき、蒸着方向は主表面と主表面に対する法線との間に位置する。それと共に、このコンタクト構造体の形成方法を用いた半導体素子の製造方法も提供される。

(もっと読む)

半導体装置およびその製造方法

【課題】溝型トランジスタとPNゲートで構成されるプレーナ型トランジスタとが共存する半導体装置において、溝型トランジスタの溝ゲートの空乏化現象によるオン電流の低下を抑制し、溝型トランジスタと異なる導電型のP又はNゲートで構成されるプレーナ型トランジスタの閾値電圧のバラツキ増加を防止する。

【解決手段】溝型トランジスタのゲート電極であるポリシリコン膜中に高濃度不純物拡散材料9が埋設された構造を有する。

(もっと読む)

半導体装置

【課題】固体電解質中のイオンの動きを高精度で制御できるデバイス構造とすることにより、記憶あるいはスイッチの機能ができる半導体装置の性能を向上させ、多層化した3次元構造も低コストで高集積化することができる技術を提供する。

【解決手段】半導体素子として、縦方向(Z軸方向)に離れて配置された電極101,103間に成分の異なる層108,109を2層以上形成し、電極101,103間にパルス電圧を印加して導電パスを形成し、抵抗値を情報信号に対応して変化させる素子とする。さらに、上記導電パスの途中に導電率を上げる成分が蓄積した領域104を形成し、それによって抵抗率を情報信号に正確に対応させる。X軸方向、Y軸方向の少なくとも一方向にも電極を形成し、制御電圧を印加するとさらに好ましい。

(もっと読む)

下部電極を有する相変化記憶素子の形成方法

【課題】下部電極を有する相変化記憶素子及びその製造方法を提供する。

【解決手段】この相変化記憶素子の形成方法は下部パターンが備えられた基板を準備する工程を含む。前記下部パターンを有する基板上に前記下部パターンとそれぞれ接触し、x軸及びy軸の次元を有する上部面が備えられた一字状またはL字状の下部電極122’’’、222’’’を形成する。この場合、前記下部電極上部面の前記x軸方向の幅はフォトリソグラフィ工程の限界解像度によって決まる幅よりも狭い幅を有するように形成する。また、前記一字状またはL字状は前記下部電極の前記x軸方向の断面形状を示す。前記下部電極の前記上部面と接触し、前記下部電極上部面の前記x軸及び前記y軸方向の幅よりもそれぞれ広い幅を有する相変化パターンを形成する。前記相変化パターン上に上部電極を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】Finの高さを必要以上に高くすることなく、実質的なチャネル幅を増大し得るFin−FETの構造及びその製造方法を提供する。

【解決手段】半導体基板11をFin状に加工して形成されたチャネル形成用半導体層11aの上面、左右両側面及び底面にゲート電極22が形成され、ゲート電極22により4面を囲まれるチャネル領域を有することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】アスペクト比が高い素子分離用溝に素子分離絶縁膜を確実に充填した状態で埋め込み形成する。

【解決手段】シリコン基板1にシリコン酸化膜5、多結晶シリコン膜6およびハードマスク材としてのシリコン窒化膜7を積層形成する。フォトリソグラフィ処理でレジストでマスクを形成し、RIEによりシリコン窒化膜7を加工してハードマスクを形成し、ハードマスクを利用して多結晶シリコン膜6、シリコン酸化膜5およびシリコン基板1をRIEにより加工してトレンチ4を形成する。このとき、エッチング条件としてフロロカーボン系ガスを添加することで、底面部の端部を除いた中間部に凸部1aを形成する。HDP酸化膜8を埋め込むときにボイド発生を防止して埋め込みを確実に行なえ、絶縁耐圧も確保することができる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】MONOS型不揮発性半導体記憶装置において、製造時にメモリセルを紫外線から保護する紫外線遮光膜を安定して形成できるようにする。

【解決手段】半導体基板1の上部にX方向に延びるビット線拡散層9と、半導体基板1の上にY方向に延びると共に電荷トラップ膜4及びゲート電極5からなるゲート構造体とを有する不揮発性半導体記憶装置に、ビット線拡散層3と接続される第1のコンタクト9が形成された第1の層間絶縁膜8と、該第1の層間絶縁膜8の上に形成された紫外線遮光膜10及び第2の層間絶縁膜11を貫通して下端部が第1のコンタクト9と接し且つ上端部が金属配線13と接続される第2のコンタクト12とを設ける構成とする。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜に形成されたダングリングボンドを効果的にキュアリングして向上した電気的特性を確保しうる半導体装置の製造方法を提供する。

【解決手段】基板100上にゲート構造物110が形成される。ゲート構造物110の形成された基板100に水素を含むガス雰囲気下で第1熱処理が行われる。基板100上に金属配線が形成される。これによって、ゲート絶縁膜パターン112のダングリングボンドがキュアリングされ、信頼性のある半導体装置が製造される。

(もっと読む)

不揮発性メモリ素子及びその製造方法

【課題】高集積化に伴うゲート面積の減少に対応して有効チャネル幅を増大させて、動作電流を確保することができる不揮発性メモリ素子及びその製造方法を提供すること。

【解決手段】基板(100)内に形成された素子分離膜(102C)によって画定され、チャネル幅方向(X軸方向)に段差を有する凹部を内部に有し、凹部の両側壁が素子分離膜(102C)の上に突出した活性領域(100B)と、凹部の段差面に沿って形成された下部絶縁膜(108A)と、下部絶縁膜(108A)上に形成された電荷保存層(109A)と、電荷保存層(109A)上に形成された上部絶縁膜(110A)と、上部絶縁膜(110A)上に形成されたゲート電極(111B)とを備える。

(もっと読む)

半導体記憶装置

【課題】プロセッサの微細化にメモリセルのスケーラビリティが追随することのできる直交変換用メモリ装置を提供する。

【解決手段】メモリセル(MC)を、2つのドレインを有するダブルドレインストレージトランジスタ(DDST)と、これらのドレインそれぞれに接続される2つのアクセストランジスタ(ATA,ATB)とで構成する。これらのトランジスタを、SOIトランジスタで構成し、ダブルドレインストレージトランジスタのボディ領域を電荷蓄積ノードとして利用する。アクセストランジスタ(ATA,ATB)に対しては、データ配列を直交変換するように、ワード線(WLA、WLB)とビット線(BLA、BLB)とを配置方向を交換して配置する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置を微細化でき、コンタクトプラグと導電部材との接触面積を十分に確保でき、コンタクト抵抗を十分に下げて、接続部分における電流の集中を低減できるとともに、導電部材を形成する際に、導電部材がコンタクトプラグを踏外すことを防止できるDRAM型キャパシタを有する半導体装置を提供する。

【解決手段】第1層間絶縁膜31よりも下に配置された第1導電部材2と電気的に接続されたコンタクトプラグ12と、第1層間絶縁膜31上に設けられ、コンタクトプラグ12と電気的に接続された第2導電部材16とを有し、コンタクトプラグ12は、小径部12aと、小径部12a上に配置された大径部12bとを有し、大径部12bの外径D1が、小径部12aの外径D2よりも大きく、大径部12bの面積が、第2導電部材16と大径部12bとの接続面16bの面積よりも平面視で大きい半導体装置とする。

(もっと読む)

半導体集積回路装置の製造方法

【課題】半導体量産プロセスにおいて、遷移金属によるウエハの汚染を防止する。

【解決手段】(a)ウエハを準備する工程と、(b)ウエハに対して、遷移金属元素を含有する所望の膜を堆積する工程と、(c)前記膜が堆積されたウエハの裏面または主面の外縁部に堆積された前記膜を除去する工程と、(d)前記裏面または前記主面の外縁部における前記膜が除去されたウエハに対して、所望の処理を実行する工程を含み、前記(c)工程における前記除去工程では、さらに、(c1)ウエハの主面とステージとの間に所定の間隔を設け、ウエハの主面とステージとを非接触な状態として、ステージに配置された複数のピンによりウエハの側面を支持する工程と、(c2)ウエハをステージと一体に回転させ、ステージ側からウエハの主面の周辺部に向かって不活性ガスを供給しながら、ウエハの裏面に洗浄液を供給する工程を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】複数の異なる配線箇所に単一のコンタクト電極を形成した構造を有する半導体装置において、製造歩留まりを向上させる。

【解決手段】半導体基板1の主面の第1方向Aに延在し、その主面上にゲート絶縁膜GZ1を介して形成され、側壁にサイドウォールスペーサ5を備えたゲート電極GE3と、その側方下部である第1部分Jに達するソース/ドレイン領域p1Jと、半導体基板1の主面を覆うようにして順に形成された、エッチング速度の異なる窒化シリコン膜6および酸化シリコン膜7を有する半導体装置であって、第1部分Jにおいて、ゲート電極GE3はサイドウォールスペーサ5に覆われておらず、ゲート電極GE3の上面、側面およびソース/ドレイン領域p1Jは、シリサイド層4Jによって覆われることで電気的に接続され、シリサイド層4Jにはノードコンタクト電極NC2が電気的に接続されている。

(もっと読む)

1,801 - 1,820 / 3,470

[ Back to top ]