Fターム[5F083ZA01]の内容

Fターム[5F083ZA01]の下位に属するFターム

リセス構造 (33)

素子分離構造が異なるもの (133)

MOSFETの構造が異なるもの (1,090)

動作電圧が異なるもの (255)

Fターム[5F083ZA01]に分類される特許

121 - 140 / 362

半導体メモリ装置及びその動作方法

【課題】不揮発性メモリ装置及びその製造方法を提供すること。

【解決手段】本発明の不揮発性メモリ装置の製造方法は、セル領域及び周辺回路領域を有する基板上に層間絶縁膜及びゲート電極膜が交互に積層されたゲート構造物を形成するステップと、前記セル領域の前記ゲート構造物を選択的にエッチングして、複数層の前記ゲート電極膜を一方向から分離させる第1トレンチを形成するステップと、前記周辺回路領域のコンタクト予定領域に対応する前記ゲート構造物を選択的にエッチングして、第2トレンチを形成するステップと、を含む。

(もっと読む)

半導体装置の製造方法

【課題】メモリセル領域とメモリセル領域の外周に周辺回路領域を有する半導体装置の製造において、セルフアラインダブルパターニングを用いてメモリセル領域の半導体基板に溝を形成する際、メモリセル領域端部において正常に溝が形成されないという問題がある。

【解決手段】メモリセル領域の第1のマスクパターンを幅W1、ピッチW3(但し、W3>2×W1)のラインパターンに形成し、その上に犠牲膜をW1の幅のギャップが残るように形成した後、塗布法で第2のマスクパターンとなる膜を形成し、犠牲膜と第2のマスクパターンとなる膜をエッチバックして第1のマスクパターン表面を露出させる。その後、第1及び第2のマスクパターン間の犠牲膜を選択的に除去し、溝パターンを形成する。周辺回路領域では、メモリセル領域との境界部を残して第1のマスクパターンを形成せず、境界部に形成される第1のマスクパターンの幅W2をW1の1〜4倍とする。

(もっと読む)

半導体記憶装置

【課題】CMOSプロセスで、ダイナミック型半導体記憶装置を形成し、ロジックとの混載に適したダイナミック型半導体記憶装置を実現する。

【解決手段】メモリセル(MC)のワード線(WL)を形成する導電線(3)とメモリセルセルプレート電極(CP)を形成する導電線(5)とを、異なる配線層に形成する。対をなすビット線に並行してメモリセルを接続し、2つのメモリセルで1ビットのデータを記憶する。

(もっと読む)

スタティックランダムアクセスメモリ

【課題】第1の導電型の共通ウェルが形成された半導体基板と、前記半導体基板上の前記共通ウェルに行列状に配列されたメモリセルよりなり、列方向に整列して共通のビット線に接続される一群のメモリセルがメモリセルカラムを形成するメモリセルアレイからなるスタティックランダムアクセスメモリにおいて、隣接カラム群間のソフトエラーの伝搬を抑制する。

【解決手段】隣接する第1および第2のカラム群において、前記第1のカラム群CG1で選択される一のメモリセルカラムの第1導電型ウェルPW(01)と、第2カラム群CG2で同時に選択されるメモリセルカラムの第1導電型ウェルPW(05)は、いずれか一方が、共通ウェル11から、第2導電型の深いウェルDNW1により遮断されており、前記第2導電型の深いウェルDNW1は、行方向に測った場合の一つのカラム群の寸法を超えない寸法を有する。

(もっと読む)

半導体記憶装置

【課題】単位面積あたりのメモリモジュールの記憶容量を増加させる。また、消費電力の小さなメモリモジュールを提供する。

【解決手段】DRAMに、高純度化された、バンドギャップが2.5eV以上の酸化物半導体膜、炭化シリコン膜および窒化ガリウム膜などでなるトランジスタを用いることで、キャパシタの電位の保持期間が延びる。また、メモリセルが容量の異なるn個のキャパシタを有し、n個のキャパシタとそれぞれ異なるn本のデータ線を接続することによって保持容量を様々にとることができる。

(もっと読む)

記憶装置

【課題】精確に記憶素子の状態を判別できる記憶装置を提供する。

【解決手段】メモリセル11を複数備えたメモリアレイ10と、読み出し対象のメモリセル11の状態を判別する読み出し回路20を設ける。メモリセル11は抵抗変化素子13を含み、読み出し回路20に備えられた参照メモリセル22は抵抗変化素子23を含む。抵抗変化素子23および抵抗変化素子13は同一の構成材料からなり、抵抗変化素子23の面積は、抵抗変化素子13の面積よりも大きい。読み出し電圧の大きさに対する抵抗変化素子23の抵抗値の変化は、抵抗変化素子13の抵抗値の変化と対応する。

(もっと読む)

固体撮像素子

【課題】記憶部で発生するリーク電流を抑制した固体撮像素子を提供する。

【解決手段】複数の画素回路1aと、列信号線21と、複数の単位記憶回路2aとを備え、複数の単位記憶回路2aのそれぞれは、書き込みトランジスタ31と、記憶容量32と、n型の第1拡散領域143と、第1拡散領域143から所定距離離して形成され、書き込みトランジスタ31のソース又はドレイン領域に隣接する絶縁分離領域141と、絶縁分離領域141の周囲に、第1拡散領域143から所定距離離して形成された、p型の第2拡散領域142とを有し、少なくとも第2拡散領域142の表面には、金属シリサイド層が形成されていないことを特徴とする。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】データの取り扱いが容易な半導体記憶装置及びその製造方法を提供する。

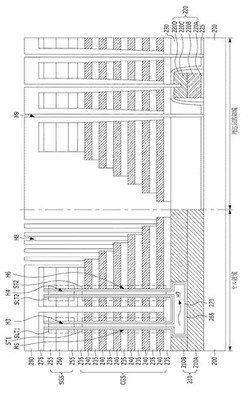

【解決手段】実施形態に係る半導体記憶装置は、基板と、前記基板上に設けられ、それぞれ複数の絶縁膜及び電極膜が交互に積層され、前記基板の上面に対して平行な第1の方向側の端部において、それぞれが各前記電極膜の上面によって構成された複数のテラスが前記第1の方向のみに沿って階段状に形成された積層体と、前記テラスに接続され、前記電極膜を、前記基板の上面に平行な方向であって前記第1の方向に対して直交する第2の方向に引き出し、前記基板に接続する導電部材と、前記積層体の中央部に設けられ、前記絶縁膜及び前記電極膜の積層方向に延びる半導体ピラーと、前記電極膜と前記半導体ピラーとの間に設けられた電荷蓄積層と、を備える。

(もっと読む)

半導体装置及び半導体記憶装置

【課題】データの保持期間を長くする半導体装置又は半導体記憶装置を提供する。

【解決手段】一対の不純物領域を有する第1の半導体層152aと、第1の半導体層と同じ材料であり、第1の半導体層と離間する第2の半導体層152bと、第1、第2の半導体層の上に設けられた第1の絶縁層153と、第1の絶縁層153を介して第1の半導体層に重畳する第1の導電層154と、第1の絶縁層153を介して第1の導電層に重畳し、第1の半導体層と異なる材料である第3の半導体層156と、第1の導電層及び第3の半導体層に電気的に接続される第2の導電層157bと、第3の半導体層156に電気的に接続され、第2の導電層と同じ材料である第3の導電層157aと、第3の半導体層、第2の導電層、及び第3の導電層の上に設けられた第2の絶縁層158と、第2の絶縁層を介して第3の半導体層に重畳する第4の導電層159と、を含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】特性を向上させる不揮発性メモリを有する半導体装置を提供する。

【解決手段】半導体装置を、制御ゲート電極CGと、制御ゲート電極CGと隣合うように配置されたメモリゲート電極MGと、絶縁膜3と、その内部に電荷蓄積部を有する絶縁膜5と、を有するよう構成する。このうち、メモリゲート電極MGは、絶縁膜5上に位置する第1シリコン領域6aと、第1シリコン領域6aの上方に位置する第2シリコン領域6bと、を有するシリコン膜よりなり、第2シリコン領域6bは、p型不純物を含有し、第1シリコン領域6aのp型不純物の濃度は、第2シリコン領域6bのp型不純物の濃度よりも低く構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】活性領域におけるイオン濃度のばらつきを抑制すること。

【解決手段】半導体装置の製造方法は、半導体基板にイオンを注入するための第1開口を有し、第1層ウェルを形成するための第1マスクを半導体基板上に形成する工程と、第1マスクを用いて半導体基板に第1イオンを注入して、第1領域及び第2領域を有する第1層ウェルを形成する工程と、半導体基板にイオンを注入するための第2開口を有し、第2層ウェルを形成するための第2マスクを半導体基板上に形成する工程と、第2マスクを用いて半導体基板に第2イオンを注入して、第1層ウェルより下方に位置する第2層ウェルを形成する工程と、を含む。第1領域を第2領域より第1層ウェルの外縁寄りに形成する。第1イオンを注入する際に、第1マスクの第1内壁面で反射した第1イオンを第1領域に供給する。第2イオンを注入する際に、第2マスクの第2内壁面で反射した第2イオンを第2領域に供給する。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】SRAMは高速で省電力なメモリであるが、携帯機器等で使用するにはさらなる省電力化が求められる。

【解決手段】オフ抵抗が極めて高いトランジスタを書き込みトランジスタとし、書き込みトランジスタのドレインを書き込みビット線に、ソースをCMOSインバータの入力に接続し、読み出しトランジスタのドレインを読み出しビット線に、ソースをCMOSインバータの出力に接続したメモリセルを用いる。書き込みトランジスタのソースにはキャパシタを意図的に設けてもよいが、CMOSインバータのゲート容量あるいはCMOSインバータの正極や負極との間の寄生容量等を用いることもできる。データの保持はこれらのキャパシタに蓄積された電荷によっておこなえるため、CMOSインバータの電源間の電位差を0とできる。このため、CMOSインバータの正負極間を流れるリーク電流がなくなり、消費電力を低減できる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】集積度を向上させた不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態によれば、第1積層構造体と、第1半導体層と、第1有機膜と、第1半導体側絶縁膜と、第1電極側絶縁膜と、を備えた不揮発性半導体記憶装置が提供される。前記第1積層構造体は、第1方向に沿って積層された複数の第1電極膜と、前記複数の第1電極膜どうしの間に設けられた第1電極間絶縁膜と、を有する。前記第1半導体層は、前記複数の第1電極膜の側面に対向する。前記第1有機膜は、前記複数の第1電極膜の前記側面と前記第1半導体層との間に設けられ有機化合物を含む。前記第1半導体側絶縁膜は、前記第1有機膜と前記第1半導体層との間に設けられる。前記第1電極側絶縁膜は、前記第1有機膜と前記複数の第1電極膜の前記側面との間に設けられる。

(もっと読む)

半導体装置

【課題】配線の引き出し性が向上されているとともに、配線間の短絡などの電気的問題が生じるおそれが抑制されており、かつ、配線が形成される領域の省スペース化が図られた半導体装置を提供する。

【解決手段】半導体装置1が備える基板4上の所定の層内に、第1の配線3が複数本並べられて設けられている。各第1の配線3は、それらの並べられた方向に沿って一方の側から他方の側へ向かうに連れて長く延ばされて形成されているか、あるいは短く縮められて形成されている。それとともに、各第1の配線3は、隣接するそれぞれの一端部3aが並べられた方向と直交する方向において互いにずれた位置に配置されている。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】占有面積の増大を抑制した不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、第1領域、第2領域、及び複数のワード線を備える。第1領域は、電気的に書き換え可能な複数のメモリトランジスタを有する。第2領域は、第1領域の周辺に位置する。複数のワード線は、複数のメモリトランジスタのゲートに各々接続されている。複数のワード線は、各々、配線部、及び接続部を備える。配線部は、第1領域から第2領域に向かうように第1方向に延び且つ第1方向に直交する第2方向に所定距離をもって配列されている。接続部は、配線部から延びて第2領域に設けられ且つ積層方向に延びるコンタクトと電気的に接続されている。複数の接続部の端部は、第2方向に延びる直線に沿って形成されている。

(もっと読む)

半導体装置の製造方法

【課題】的確かつ効果的にパターンを形成することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、下地領域上に、第1のピッチで配置された複数のダミーラインパターン21cを形成する工程と、ダミーラインパターン21cの両長側面に形成された所定マスク部分を有し、ダミーラインパターンを囲む閉ループ形状のマスクパターン25cを形成する工程と、ダミーラインパターン21cを除去する工程と、マスクパターン25cの両端部分を除去して所定マスク部分を残す工程と、所定マスク部分をマスクとして用いて下地領域をエッチングする工程とを備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】柱状のチャネル層となる半導体層に沿って、複数の浮遊ゲート型の不揮発性メモリセルが積層された構造の不揮発性半導体記憶装置を提供する。

【解決手段】実施形態によれば、柱状の半導体膜131の側面にトンネル誘電体膜141、浮遊ゲート電極膜142、ゲート間絶縁膜143および制御ゲート電極膜144を備えるメモリセルMCが半導体膜131の延在方向に複数設けられるメモリセル列を、半導体基板101上に略垂直に複数配置した不揮発性半導体記憶装置が提供される。ここで、浮遊ゲート電極膜142と制御ゲート電極膜143は、柱状の半導体膜131の全周のうち特定の方向の側面にのみ形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを有する半導体装置の性能を向上させる。

【解決手段】スプリットゲート型の不揮発性メモリは、半導体基板1上に絶縁膜3を介して形成された制御ゲート電極CGと、半導体基板1上に電荷蓄積部を有する絶縁膜5を介して形成されたメモリゲート電極MGとを有しており、メモリゲート電極MGは、制御ゲート電極CGの側面22上に絶縁膜5を介してサイドウォールスペーサ状に形成されている。制御ゲート電極CGは、メモリゲート電極MGに絶縁膜5を介して隣接する側とは反対側の側面21の下部21aが突出し、また、メモリゲート電極MGに絶縁膜5を介して隣接する側の側面22の下部22aが後退している。メモリゲート電極MGは、制御ゲート電極CGに絶縁膜5を介して隣接する側の側面23の下部23aが突出している。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性を向上させる。

【解決手段】本発明の半導体装置は、面方位が(110)のシリコン基板1と、pMIS領域1Bに形成されたpチャネル型電界効果トランジスタを有する。このpチャネル型電界効果トランジスタは、ゲート絶縁膜3を介して配置されたゲート電極GE2と、ゲート電極GE2の両側のシリコン基板1中に設けられた溝g2の内部に配置され、Siより格子定数が大きいSiGeよりなるソース・ドレイン領域と、を有する。上記溝g2は、ゲート電極GE2側に位置する側壁部において、第1の斜面と、第1の斜面と交差する第2の斜面と、を有する。このように、溝g2の形状をΣ形状とすることで、pチャネル型電界効果トランジスタのチャネル領域に加わる圧縮歪みを大きくすることができる。

(もっと読む)

半導体記憶装置

【課題】

駆動回路からメモリセルへの寄生抵抗や寄生容量の影響により、非選択セルへの熱ディスターブ、印加電圧のばらつき、読み出し時の記憶素子の劣化等の課題があった。

【解決手段】

電流により記憶情報が書き込まれる記憶素子と、当該記憶素子に接続される選択素子と、を有するメモリセル(MC)の上方または下方にキャパシタ(C)を設け、当該キャパシタに蓄積された電荷によって記憶素子に書き込みを行う。

(もっと読む)

121 - 140 / 362

[ Back to top ]