Fターム[5F083ZA01]の内容

Fターム[5F083ZA01]の下位に属するFターム

リセス構造 (33)

素子分離構造が異なるもの (133)

MOSFETの構造が異なるもの (1,090)

動作電圧が異なるもの (255)

Fターム[5F083ZA01]に分類される特許

141 - 160 / 362

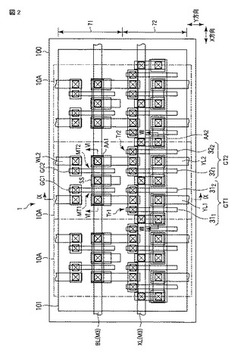

スイッチアレイ

【課題】 スイッチアレイの占有面積の縮小を図る。

【解決手段】本実施形態のスイッチアレイは、基板上に設けられる2つのスイッチと、第1の方向に延在する第1及び第2の制御線と、を具備し、スイッチのそれぞれは、メモリセルトランジスタが設けられる第1のアクティブ領域と、パストランジスタが設けられる第2のアクティブ領域と、を含み、アクティブ領域内でトランジスタのチャネル長方向に隣接するメモリセルトランジスタはソース又はドレインを共有し、第1及び第2のアクティブ領域は、トランジスタのチャネル幅方向に互いに隣接している。

(もっと読む)

半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな駆動方法を提供する。また、新たな駆動方法により、メモリ素子への書き込み電位のばらつきを低減し、信頼性を向上させる。

【解決手段】半導体装置の駆動方法において、書き込み電位を段階的に上昇させて、同時に読み出し電流を確認し、読み出し電流の結果を書き込み電位に利用して書き込みを行う。つまり、正しい電位で書き込みが行われたか確認しながら書き込みを行うことで、信頼性の高い書き込みを行うことが可能である。

(もっと読む)

半導体記憶装置

【課題】 簡略化された構造を実現可能な半導体記憶装置を提供する。

【解決手段】 半導体記憶装置は、基板表面の上方に設けられ、直列接続された複数のメモリセルを含んだ複数のメモリセルユニット3を含む。メモリセルは、半導体柱9と前記半導体柱の周囲の導電膜および絶縁膜5を含み、不揮発にデータを記憶する。複数のメモリセルユニットは複数のブロックを構成する。パイプ層PCは、隣接する第1、第2メモリセルユニットの各組において、第1、第2メモリセルユニットの各半導体柱と接続された半導体層を含む。導電性のプレートBGは、第1、第2メモリセルユニットの各一端と半導体基板の表面との間に設けられ、少なくとも2つのブロックのパイプ層を内部に含み、内部のパイプ層の導通および非導通を制御する。供給経路構造CBG1、LBG1、CBG2、TBG、CBG3は、プレートに接続され、プレートに印加されるプレート線DBGの電位をプレートに供給する。

(もっと読む)

半導体装置及びその製造方法、並びに吸着サイト・ブロッキング原子層堆積法

【課題】キャパシタの誘電体膜において、リーク特性改善のためのAlドープ層を設けても、誘電体膜がAlドープ層で分断されず、サイズ効果の影響を抑え、結晶性の良好な誘電体膜を提供する。

【解決手段】誘電体膜中に少なくとも1層のAlドープ層を有し、Alドープ層の1層におけるAl原子の面密度を1.4E+14[atoms/cm2]未満とする。また、その面密度を達成するため、通常のALDによる誘電体膜成膜と、Alソースの吸着サイトを制限するブロッカー分子の吸着を行った後、Alソースを吸着させ、反応ガスを導入して反応させる吸着サイト・ブロッキングALD法によるAl添加の組み合わせを採用する。

(もっと読む)

半導体記憶装置

【課題】信頼性が高い半導体記憶装置を提供する。

【解決手段】実施形態に係る半導体記憶装置は、基板と、前記基板上に設けられ、それぞれ複数の絶縁膜及び電極膜が交互に積層され、対向する第1の階段及び第2の階段を有する積層体と、前記第1及び第2の階段が形成されている領域外の前記積層体内に設けられ、前記絶縁膜及び前記電極膜の積層方向に延びる半導体部材と、前記電極膜と前記半導体部材との間に設けられた電荷蓄積層とを備える。そして、前記電極膜は、前記第1の階段に形成された第1のテラスと、前記第2の階段に形成された第2のテラスと、前記第1のテラス及び前記第2のテラスを接続するブリッジ部とを有する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】 ダイオードとトランジスタとを直列接続した半導体メモリにおいて、ダイオードからトランジスタにキャリアが入ることで、トランジスタの特性が劣化する課題がある。

【解決手段】 半導体記憶装置において、ダイオード(PD)中のキャリアを生成するダイオード半導体層(40p)と、トランジスタのチャネル層(8p)との間に、当該キャリアを対消滅させる構造(61pと62p等)を有する。

(もっと読む)

不揮発性半導体記憶装置

【課題】書き込みを高速化した不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置110は、ベース半導体層10aと、電極70aと、チャネル半導体層30aと、ベーストンネル絶縁膜20aと、チャネルトンネル絶縁膜40aと、電荷保持層50aと、ブロック絶縁膜60aと、を有するメモリ部MC1を備える。チャネル半導体層30aは、ベース半導体層10aと電極70aとの間に設けられ、電極70aに対向するチャネル部31aを含む。ベーストンネル絶縁膜20aは、ベース半導体層10aとチャネル半導体層30aとの間に設けられる。チャネルトンネル絶縁膜40aは、電極70aとチャネル部31aとの間に設けられる。電荷保持層50aは、電極70aとチャネルトンネル絶縁膜40aとの間に設けられ、電荷を保持する。ブロック絶縁膜60aは、電極70aと電荷保持層50aとの間に設けられる。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリセル領域の周辺に金属電極を有するアンチフューズを製造歩留り良く形成する。

【解決手段】MOSトランジスタを備えたメモリセルを有するメモリセル領域と、アンチフューズを備えた周辺回路領域とを有する半導体装置において、メモリセルを構成するコンタクトプラグ又はビット配線と同層に形成される周辺回路のコンタクトプラグ又は配線を用いて、アンチフューズの電極を形成する。

(もっと読む)

半導体集積回路

【課題】トランジスタの性能の劣化の防止に有利な半導体集積回路を提供する。

【解決手段】実施形態によれば、半導体集積回路は、ワード線とビット線との交差位置にそれぞれ配置されデータを保持するデータ記憶部(SRAMセル)と前記データ記憶部に記憶された保持データを論理的に反転させる反転回路22と、前記データ記憶部が記憶するデータの論理反転の有無を識別するフラグをロウ単位で記憶するフラグビットカラム11−1とを備える、メモリセルアレイ11を具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】不純物の偏析に起因する、ドレイン領域と空乏層との間のリーク電流の発生を抑制することが可能な半導体素子を含む半導体装置を提供する。

【解決手段】本半導体装置は、主表面を有する半導体基板SUBと、主表面上に形成された、論理回路を構成するコアトランジスタと、入出力回路を構成するI/Oトランジスタとを備える。主表面からI/On型トランジスタのn型不純物領域NRの最下部までの距離は、主表面からコアn型トランジスタのn型不純物領域NRの最下部までの距離より長い。主表面からI/Op型トランジスタのp型不純物領域PRの最下部までの距離は、主表面からコアp型トランジスタのp型不純物領域の最下部までの距離より長い。主表面からI/On型トランジスタのn型不純物領域の最下部までの距離は、主表面からI/Op型トランジスタのp型不純物領域の最下部までの距離より長い。

(もっと読む)

半導体装置の製造方法

【課題】前工程においてトランジスタごとに不純物の種類や量を変えることによる、製造コストや製造時間の増大を抑制する。

【解決手段】本発明による半導体装置の製造方法は、第1の閾値電圧及び第1のドレイン・ソース間電流を呈するようなデバイスパラメータをもって設計された第1のトランジスタを含む半導体回路を形成する半導体回路形成工程(ステップS11)と、第1のトランジスタにストレス電圧を印加して第1の閾値電圧とは異なる第2の閾値電圧及び前記第1のドレイン・ソース間電流とは異なる第2のドレイン・ソース間電流の少なくとも一方を第1のトランジスタが呈するようにする特性制御工程(ステップS14)と、第1のトランジスタが第2の閾値電圧及び第2のドレイン・ソース間電流の少なくとも一方を呈する状態で出荷する出荷工程(ステップS16)とを備える。

(もっと読む)

半導体メモリおよびその製造方法

【課題】素子分離トレンチ内の絶縁膜のエッチングとアライメントトレンチ内の絶縁膜のエッチングとを、1つのマスクを用いて同時に行える構造の半導体メモリを提供する。

【解決手段】シリコン基板2には、メモリセル領域70およびアライメントマーク領域80が設定されている。メモリセル領域70には、シリコン基板2の表層部に、アクティブ領域30を分離する素子分離トレンチ21が形成されている。アライメントマーク領域80には、シリコン基板2の表層部に、マスク合わせのためのアライメントトレンチ82が形成されている。素子分離トレンチ21内には、素子分離トレンチ21間のアクティブ領域30が突出するように、絶縁物(酸化膜)23が素子分離トレンチ21の深さ方向途中まで埋め込まれている。一方、アライメントトレンチ82内には、絶縁物23がアライメントトレンチ82の深さ方向途中まで埋め込まれている。

(もっと読む)

半導体装置およびその製造方法

【課題】相変化記録素子のまわりを伝導率の低い真空の空隙部で覆うことで、さらに高い発熱効率を得ることができ、書き換え電流を低減することができる半導体装置を提供する。

【解決手段】半導体基板と、半導体基板の上に形成されたスイッチング素子を含む素子層と、素子層上において、スイッチング素子に接続されたヒータ電極11、ヒータ電極11の熱によって相転移する相変化記録材料層12及び上部電極13が順次積層されてなる相変化記録素子10と、相変化記録素子10の上に積層された層間絶縁膜21bと、素子層と層間絶縁膜21bの間にあってヒータ電極11または相変化記録材料層12のいずれか一方又は両方の周囲に形成された真空の空隙部15と、を具備してなる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】信頼性が高い半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置は、電極膜及び絶縁膜が交互に積層され、端部の形状が前記電極膜毎にステップが設けられた階段状である積層体と、前記端部の上方から前記電極膜に接続されたコンタクトと、前記積層体の前記端部以外の部分に設けられ、前記積層体を積層方向に貫く半導体部材と、前記電極膜と前記半導体部材との間に設けられた電荷蓄積層と、前記端部を前記積層方向に貫く貫通部材と、を備える。そして、前記貫通部材には、前記電荷蓄積層を形成する材料と同種の材料が含まれていない。

(もっと読む)

半導体装置

【課題】高集積化を図り、単位面積あたりの記憶容量を増加させた新たな構造の半導体装置を提供することを目的の一とする。高集積化に伴い増加する回路素子数の低減が可能で、かつ、素子数低減による電力削減が可能な、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ビット線と、m(mは3以上の自然数)本のワード線と、ソース線と、m本の信号線と、第1乃至mのメモリセルと、駆動回路と、を有する半導体装置において、メモリセルは、第1のトランジスタ、容量素子に蓄積された電荷を保持する第2のトランジスタを含み、第2のトランジスタは酸化物半導体層で形成されるチャネルを有する。上記構成において、駆動回路は、第j(jは3以上の自然数)の信号線に出力される信号を用いて第(j−1)の信号線に出力される信号を生成する。

(もっと読む)

ヒューズアレイと共に抵抗ランダムアクセスメモリを形成

【課題】抵抗ランダムアクセスメモリアレイが、ヒューズアレイと同一の基板上に形成する方法及びその集積回路を提供する。

【解決手段】ランダムアクセスメモリとヒューズアレイは同一の有効材料を使用する。例えば、ヒューズアレイとメモリアレイは、有効スイッチング材料としてカルコゲニド材料を使用する。主アレイはトレンチ分離82,84の直交する組のパターンを使用し、ヒューズアレイは平行なトレンチ分離82,84の一つの組のみを使用する。結果として、ヒューズアレイは、隣接するトレンチ分離82,84の間で連続して延伸する導電線を有する。いくつかの実施形態では、この連続する線はヒューズを通る導電性パスの抵抗を低減する。

(もっと読む)

メモリ素子の駆動方法及びメモリ素子を備える記憶装置

【課題】より安定的にスイッチング動作を行う。

【解決手段】絶縁性基板1と、絶縁性基板に設けられた第1電極2及び第2電極3と、第1電極と第2電極との間に設けられ、第1、第2電極間の抵抗値の変化現象が生じるナノメートルオーダーの間隙を有する電極間間隙部4とを備え、所定の低抵抗状態から所定の高抵抗状態への移行と、高抵抗状態から前記低抵抗状態への移行とが可能なメモリ素子10の駆動方法において、高抵抗状態から前記低抵抗状態への移行の際には、メモリ素子に対して定電流回路により電流パルスを加えることを特徴とする。

(もっと読む)

半導体装置

【課題】補償容量素子を構成する容量絶縁膜が破壊されることのない半導体装置を提供する。

【解決手段】第1の電圧が供給される第1の電源端子29と、第2の電圧が供給される第2の電源端子23と、容量絶縁膜42と該容量絶縁膜42を挟んで形成される第1及び第2電極とを其々備えており、前記第1及び第2の電源端子間に直列に設けられる複数の補償容量素子4と、奇数番目の前記補償容量素子4と次の偶数番目の前記補償容量素子4とを各々接続する第1の配線層に形成された第1の容量接続配線と、偶数番目の前記補償容量素子4と次の奇数番目の前記補償容量素子4とを各々接続する第2の配線層に形成された第2の容量接続配線と、前記第1及び第2の容量接続配線のいずれか一方に隣接して設けられ、実質的に固定された電圧が供給されるシールド配線5と、を備える。

(もっと読む)

メモリ素子の駆動方法及びメモリ素子を備える記憶装置

【課題】より安定的にスイッチング動作を行う。

【解決手段】絶縁性基板1と絶縁性基板に設けられた第1電極2及び第2電極3と第1電極と第2電極との間の抵抗値の変化現象を生じる電極間間隙部4とを備えるメモリ素子10に対し、所定の低抵抗状態から所定の高抵抗状態へ移行させるための第1の電圧パルスをパルス発生源から印加し、高抵抗状態から低抵抗状態へ移行させるための第2の電圧パルスの印加を直列接続された抵抗体を介して行うことにより、低抵抗値へ変化後のメモリ素子に流れる電流値を低減させる。

(もっと読む)

不揮発性記憶装置とその制御方法

【課題】スイッチング歩留りを向上させることができる不揮発性記憶装置を提供する。

【解決手段】実施形態によれば、不揮発性記憶装置は、下部電極膜BEと、上部電極膜TEと、前記下部電極膜BEと前記上部電極膜TEとの間に挟持される抵抗変化層RWと、を備える。前記抵抗変化層RWは、前記上部電極膜TE側から前記下部電極膜BE側に流れる電気的信号によって、複数の異なる抵抗状態間を可逆的に変化させることが可能なSi,Cを主成分とし、Nを含むアモルファスの膜からなる。また、前記上部電極膜TEは、前記下部電極膜BEよりも窒素濃度が低い材料によって構成される。

(もっと読む)

141 - 160 / 362

[ Back to top ]