Fターム[5F083ZA01]の内容

Fターム[5F083ZA01]の下位に属するFターム

リセス構造 (33)

素子分離構造が異なるもの (133)

MOSFETの構造が異なるもの (1,090)

動作電圧が異なるもの (255)

Fターム[5F083ZA01]に分類される特許

161 - 180 / 362

半導体装置及び半導体装置の製造方法

【課題】リークパスを確実に防止することができる、半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体装置は、ゲート絶縁膜を介して半導体基板上に設けられたゲート電極と、前記ゲート電極の側部に設けられた側壁絶縁膜と、前記半導体基板内における前記ゲート絶縁膜を挟むような位置に形成され、前記側壁絶縁膜により覆われた被覆領域と前記側壁絶縁膜により覆われていない露出領域とを有する、ソース又はドレイン領域と、前記ゲート電極及び前記側壁絶縁膜を覆うように形成された、エッチングストッパ膜と、前記半導体基板上に、前記エッチングストッパ膜を埋め込むように設けられた、層間絶縁膜と、前記層間絶縁膜を貫通するように設けられ、前記露出領域に接続される、第1セルコンタクトプラグとを具備する。前記エッチングストッパ膜は、前記被覆領域と前記露出領域との境界部分が完全に覆われるように、前記露出領域の一部を覆っている。

(もっと読む)

不揮発性記憶装置とその制御方法

【課題】スイッチング歩留りを向上させることができる不揮発性記憶装置を提供する。

【解決手段】実施形態によれば、不揮発性記憶装置は、下部電極膜BEと、上部電極膜TEと、前記下部電極膜BEと前記上部電極膜TEとの間に挟持される抵抗変化層RWと、を備える。前記抵抗変化層RWは、前記上部電極膜TE側から前記下部電極膜BE側に流れる電気的信号によって、複数の異なる抵抗状態間を可逆的に変化させることが可能なSi,Cを主成分とし、Nを含むアモルファスの膜からなる。また、前記上部電極膜TEは、前記下部電極膜BEよりも窒素濃度が低い材料によって構成される。

(もっと読む)

半導体装置

【課題】キャパシタを形成する領域の占有面積を縮小する。

【解決手段】本実施形態の半導体装置は、半導体基板10内に設けられた半導体領域AACと、半導体領域AAC内に設けられる複数のキャパシタCm,Cnを含むキャパシタ群と、を具備し、キャパシタCm,Cnのそれぞれは、半導体領域AAC上のキャパシタ絶縁膜42Aと、キャパシタ絶縁膜42A上のキャパシタ電極34Am,34Amと、キャパシタ電極34Am,34Amに隣接する拡散層32Aとを有し、を有し、キャパシタ電極34Am,34Anに接続される配線29m,29nのそれぞれは、キャパシタCm,Cn毎に電気的に分離され、キャパシタ電極Cm,Cnのそれぞれに異なる電位Vm,Vnが印加されている。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、メモリセルアレイを有する半導体装置において、直列に接続された第1乃至第mのメモリセルに含まれる各ノードに生じる寄生容量の値を同等の値とすることで、安定して動作可能な半導体装置とする。

(もっと読む)

半導体装置の製造方法

【課題】 メモリセルアレイ領域と周辺回路領域との配線溝の深さを最適化する。

【解決手段】 本発明の一態様の半導体装置の製造方法によれば、レジストパターンをマスクとして芯材膜を加工する工程と、前記芯材膜上に被加工膜とエッチング選択比がある側壁膜を形成する工程と、前記側壁膜を異方性エッチング工程により加工する工程と、前記芯材膜を前記側壁膜と選択的に除去する工程と、第1領域の前記側壁膜上および前記被加工膜上に絶縁膜を第1の膜厚を有するように形成し、第2領域の前記被加工膜上に前記絶縁膜を第2の膜厚を有するように形成する工程と、を備えている。さらに、前記第2領域においてフォトリソグラフィ工程によりレジストパターンを形成する工程と、前記第1領域における前記側壁膜と前記第2領域における前記レジストパターンとをマスクとして前記絶縁膜および前記被加工膜を加工し、前記被加工膜に配線溝を形成する工程と、を備えている。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】低消費電力で動作し、記憶情報の信頼性が高く、小型で軽量、安価な記憶装置と

その駆動方法を提供することを課題とする。さらに低消費電力で動作し、記憶情報の信頼

性が高く、無線通信距離の長い、小型で軽量、安価な半導体装置とその駆動方法を提供す

ることを課題とする。

【解決手段】記憶装置は、少なくとも記憶素子がマトリックス状に配置されたメモリセル

アレイと、書き込み回路とを有し、記憶素子は第一の導電層と、第二の導電層と第一の導

電層と第二の導電層とに挟まれて設けられた有機化合物層とを有し、書き込み回路は、複

数回印加する電圧を発生させる電圧発生回路と、電圧の出力時間を制御するタイミング制

御回路とを有することを特徴とする。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】消去動作特性を向上した一括加工型3次元積層メモリ構成の不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態によれば、積層構造体MLと、導電芯ピラーPBG、芯絶縁膜49、半導体パイプピラーSP、内側絶縁膜42、記憶層48、外側絶縁膜43、を備えた不揮発性半導体記憶装置が提供される。積層構造体は、第1方向に積層された複数の電極膜61と、複数の電極膜どうしの間に設けられた電極間絶縁膜62と、を有する。導電芯ピラーは積層構造体を第1方向に貫通する。芯絶縁膜は導電芯ピラーと電極膜との間に設けられる。半導体パイプピラーは芯絶縁膜と電極膜との間に設けられ、積層構造体を第1方向に貫通する。内側絶縁膜は半導体パイプピラーと電極膜との間に設けられる。記憶層は内側絶縁膜と電極膜との間に設けられる。外側絶縁膜は記憶層と電極膜との間に設けられる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】規則的に配列した複数の微細な開口部OPを有するフィルタFLを通過したイオンビーム22をレンズ26で収束して半導体ウエハ1Wに照射することにより、チャネルドープイオン注入を行なう。この際、フィルタFLには、イオンビーム22と同じ極性の電圧を印加する。フィルタFLの開口部OPの中央部に向かって入射した不純物イオンは、そのまま直進して開口部OPを通過することができるが、フィルタFLの開口部OPの中央部以外の領域に向かって入射する不純物イオンは、フィルタFLによる電場によって進行方向が曲げられて、開口部OPを通過することができない。このため、半導体ウエハ1Wに注入された不純物イオンは、規則的な配列を有したものとなり、MISFETのしきい値電圧のばらつきを抑制できる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】生産性を向上した一括加工型3次元積層メモリ構成の不揮発性半導体記憶装置を提供する。

【解決手段】実施形態によれば、積層構造体MLと、選択ゲート電極SGと、半導体ピラーSPと、記憶層48と、内側絶縁膜42と、外側絶縁膜43と、選択ゲート絶縁膜SGIと、を備えた不揮発性半導体記憶装置が提供される。積層構造体は、第1方向に積層された複数の電極膜61と、電極間絶縁膜62と、を有する。選択ゲート電極は、積層構造体と積層された複数の選択ゲート導電膜71と、選択ゲート導電膜間絶縁膜72と、を有する。半導体ピラーは、積層構造体及び選択ゲート電極を第1方向に貫通する。記憶層は、電極膜と半導体ピラーとの間に、内側絶縁膜は、記憶層と半導体ピラーとの間に、外側絶縁膜は、記憶層と電極膜との間に、選択ゲート絶縁膜は、選択ゲート導電膜と半導体ピラーとの間に設けられる。

(もっと読む)

配線形成方法

【課題】配線層で、配線密度の高い領域では隣接する配線間のショートを防ぎ、配線密度の低い領域では所望の平坦度が得られるとともに所望の配線抵抗が得られるように配線高さを制御できる配線形成方法を提供する。

【解決手段】まず、基板上に第1の絶縁膜111と、第1の絶縁膜111に比してCMP研磨レートの小さい所定の厚さの第2の絶縁膜112を順に積層させて層間絶縁膜11を形成し、ついで、層間絶縁膜11の第1の領域に第1の配線密度となり、第2の領域に第1の配線密度よりも低い第2の配線密度となるように、第2の絶縁膜112を貫通し、底部が第1の絶縁膜111に至る配線形成用溝21を形成した後、配線形成用溝21を形成した層間絶縁膜11上に導電性材料膜14を形成し、そして、CMP法によって、少なくとも第1の領域で第1の絶縁膜111が露出、後退するように層間絶縁膜11と導電性材料膜14を研磨する。

(もっと読む)

半導体装置及びその製造方法

【課題】D−RAMのキャパシタを形成するシリンダのドライエッチ加工において、従来技術の製造方法ではアスペクト比が高いシリンダやコンタクトの形状がボーイング形状となり隣接するホール間ショートの問題やホール内に形成する電極成膜のカバレッジ異常などの問題が発生する。

【解決手段】本発明ではシリコン酸化膜4aにコンタクトホールを形成する際にボーイングが発生する部分にLow−k膜の炭化シリコン酸化膜5を挿入して積層構造とし、ドライエッチでシリコン酸化膜4aのエッチング速度に対し、炭化シリコン酸化膜5のエッチング速度が1/5〜1/10と遅い条件にすることでボーイング形状の抑制を可能にした。

(もっと読む)

抵抗変化メモリ

【課題】高い抵抗値の抵抗素子を実現する。

【解決手段】本実施形態の抵抗変化メモリは、第1の配線レベルILV1に位置し、第1の方向に延びる制御線L1と、第2の配線レベルILV2に位置し、第2の方向に延びる制御線L2と、制御線L1と制御線L2との間に設けられるセルユニットCUとを含むメモリセルアレイを有し、複数の配線レベルに設けられる少なくとも2つの抵抗線RL3A,RL5と、抵抗線RL3A,RL5間に設けられ、セルユニットCUの構成部材又はコンタクトプラグZCの構成部材と同じ構成部材を含む抵抗体91と、を有し、抵抗素子領域17内に設けられる抵抗素子90を含んでいる。

(もっと読む)

半導体装置及びその製造方法、並びにデータ処理システム

【課題】チャネル領域を従来よりも拡大することが可能な半導体装置を提供する。

【解決手段】埋め込みゲート用の溝部9,10のうち、活性領域6に形成される第1の溝部9よりも素子分離領域5に形成される第2の溝部10の深さを深くすることによって、第2の溝部10の底面の間から活性領域6の一部が突き出した第1のフィン部12aと、埋め込みゲート用の溝部9,10の少なくとも上面開口部よりも下部側において、第1の溝部9よりも第2の溝部10の第1の方向における幅を大きくすることによって、第2の溝部10の両側面の間から第1のフィン部12aに連続して活性領域6の一部が突き出した一対の第2のフィン部と12bとを形成する。

(もっと読む)

半導体装置

【課題】コンタクト電極と配線とを安定して接続する。

【解決手段】実施形態の半導体装置は、平面形状がリング状の第1のコンタクト部41を有する第1の配線40と、第1の配線40より下層に設けられる第2の配線50と、コンタクト部41のリング状の部分を貫通して、2つの配線40,50を電気的に接続するコンタクト電極60とを含み、基板11上に設けられる配線領域を具備する。

(もっと読む)

半導体装置及びその作製方法

【課題】書き込み電圧が小さいアンチヒューズを提供する。

【解決手段】アンチヒューズは読み出し専用の記憶装置のメモリ素子に用いられる。アンチヒューズは、第1導電層、絶縁層、半導体層、及び第2導電層を有する。アンチヒューズに含まれる絶縁層は、原料ガス中にアンモニアを添加して形成した酸化窒化シリコンであり、層中に1.2×1021以上3.4×1021atoms/cm3以下の水素、または3.2×1020以上2.2×1021atoms/cm3以下の窒素を含むことで、低電圧での書き込みが可能となる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】補償容量素子のキャパシタ構造に起因したリーク電流の増加を抑制するとともに、立体構造のキャパシタ構造を採用して、占有面積を削減した半導体装置を提供する。

【解決手段】メモリセル領域に形成されたクラウン型のキャパシタ21aと、周辺回路領域に形成されたコンケイブ型の補償容量素子10と、を有することを特徴とする半導体装置20を提供する。また、第1層間絶縁膜上にパッド47a,47bを形成する工程と、パッド47a,47b上に有底筒形状の下部電極66a,66bを形成する工程と、メモリセル領域の下部電極66aの内壁面及び外壁面と、周辺回路領域の下部電極66bの内壁面のみを誘電体膜67a,67bで覆う工程と、誘電体膜上に上部電極69a,69bを形成する工程と、を有することを特徴とする半導体装置20の製造方法を提供する。

(もっと読む)

半導体装置

【課題】不揮発性メモリと容量素子を有し、性能を向上させる半導体装置を提供する。

【解決手段】スプリットゲート型の不揮発性メモリのメモリゲート電極MG6nとp型ウエルPW1との間および制御ゲート電極CG4nとメモリゲート電極MG6nとの間には、内部に電荷蓄積層5bを有する絶縁膜5が形成されている。この絶縁膜5は、酸化シリコン膜5aと、その上に形成された窒化シリコン膜5bと、その上に形成された酸化シリコン膜5cと、その上に形成されかつ酸化シリコン膜5cよりも薄い絶縁膜5dとの積層膜からなる。この絶縁膜5dは、ポリシリコンからなるメモリゲート電極MG6nに接している。絶縁膜5dは、Hf,Zr,Al,Ta,Laのうちの少なくとも1種を含む金属化合物により形成されているため、フェルミピニングを生じることができ、誘電率が高い。

(もっと読む)

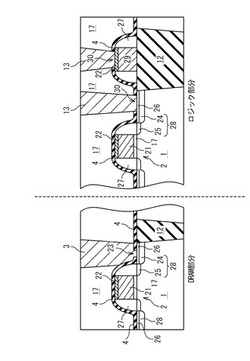

マルチレベルアーキテクチャを有するフラッシュメモリ

【課題】より良く知られている2次元メモリ構造の製造のために用いられる処理フローから比較的小さく修正された処理フローを用いて製造され得る3次元メモリ構造およびその製造方法を提供する。

【解決手段】マルチレベルメモリデバイスを製造する方法であって、基板105上に周辺回路120を形成することと、周辺回路120および基板105を層間誘電層145で覆うことと、層間誘電層145上に1レベル以上のメモリアレイのスタック110を形成することと、を含む製造方法。

(もっと読む)

階段型構造の形成方法及びこれを利用した不揮発性メモリー素子の製造方法

【課題】本発明は、不揮発性メモリー素子の製造方法を提供し、不揮発性メモリー素子において階段形態のゲートを具現できるパターニング方法を提供する。

【解決手段】本発明は階段型構造を形成する方法及びこれを利用した不揮発性メモリー素子の製造方法に関し、複数個の薄膜をプレート形状に積層し、前記複数個の薄膜のうち最上層の薄膜上にマスクを形成し、前記マスクを利用したエッチングを使用して前記最上層の薄膜をパターニングし、前記マスクを順次的に拡大し、そして前記順次的拡大されたマスクを利用したエッチングを使用して余り薄膜を順次的にパターニングすることを含み、前記複数個の薄膜を前記プレート形状から階段形態に形成するパターニング方法を利用して階段型構造を有するコントロールゲートを含む不揮発性メモリー素子を製造できる。

(もっと読む)

半導体装置の製造方法

【課題】検査コストや解析コスト、製品コストを低減可能な半導体装置の製造方法を提供する。

【解決手段】例えば、ウエハ検査工程(S1003)で、半導体ウエハ上のロジック回路を対象とした電気的検査(ロジック部テスト)(S1003a)と、メモリ回路を対象とした電気的検査(メモリ部テスト)(S1003b)を行い、それぞれの検査結果から得られた故障箇所を複合マップ24上に重ねて表示する。この複合マップ24を用いると、例えば、ロジック故障22とメモリ故障23が併存して分布する領域を判別でき、この領域に対してメモリ故障23に対する詳細解析を優先的に行うことで、特にロジック故障22とメモリ故障23の故障原因が共通であった場合に効率的な詳細解析を行うことが可能となる。

(もっと読む)

161 - 180 / 362

[ Back to top ]