Fターム[5F083ZA01]の内容

Fターム[5F083ZA01]の下位に属するFターム

リセス構造 (33)

素子分離構造が異なるもの (133)

MOSFETの構造が異なるもの (1,090)

動作電圧が異なるもの (255)

Fターム[5F083ZA01]に分類される特許

81 - 100 / 362

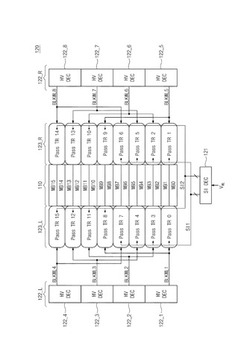

不揮発性メモリ装置

【課題】 パストランジスタ間の空間確保が可能な不揮発性メモリ装置を提供する

【解決手段】 不揮発性メモリ装置100が備える行デコーダ120は、パストランジスタ部123_L、123_Rを含む。パストランジスタ部123_L、123_Rは、メモリブロック110の左右に配列される。ブロック選択信号BLKWL1によって共通ゲートを形成するパストランジスタ端Pass TR 0とパストランジスタ端Pass TR 8とは、選択的に活性化される第1駆動信号ラインSI1及び第2駆動信号ラインSI2によって独立して駆動される。互に異なるブロック選択信号BLKWLによって駆動されるパストランジスタは、1つの活性領域の上に形成され得る。これにより、1つの活性領域の上に2つのパストランジスタを形成する場合、パストランジスタ部123_L、123_Rのチャンネル方向の大きさを減らすことができる。

(もっと読む)

半導体装置

【課題】DRAM回路などのように容量を内蔵する半導体装置において、コンタクト容量およびコンタクト抵抗を増加させることなく、容量の容量値を増加させる。

【解決手段】セルコンタクトが形成されるセルコンタクト部にまで容量の形成場所を延長することで、容量値のさらなる増大が可能となる。なお、容量部、容量コンタクト部およびセルコンタクト部にまたがる容量の形成には、ALD法などによるスパッタ装置を用いることが好ましい。

(もっと読む)

半導体装置

【課題】半導体装置の電源線および接地線の高抵抗化を抑制する。

【解決手段】第1の方向に延伸された第1の回路セル列及び第2の回路セル列と、第1の方向に延伸され、第1の回路セル列上に配置され、第1の電源線には第1の電源電位が供給される、第1及び第2の電源線と、第1の方向に延伸され、第2の回路セル列上に配置され、第2の電源電位が供給される第3の電源線と、第2の電源線と第3の電源線との間に接続され、導通状態において第2の電源線と第3の電源線とを接続して第3の電源線から第2の電源線に第2の電源電位を供給し、非導通状態において第2の電源線と第3の電源線とを電気的に切り離す第1のトランジスタと、第1の回路セル列に配置され、第1の電源線から供給される第1の電源電位と第2の電源線から供給される第2の電源電位との間の電源電圧で動作する第1の回路素子とを備える。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜を用いたトランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を作製する。

【解決手段】酸化物半導体膜を用いた半導体装置であるトランジスタにおいて、酸化物半導体膜から水素を捕縛する膜(水素捕縛膜)、および水素を拡散する膜(水素透過膜)を有し、加熱処理によって酸化物半導体膜から水素透過膜を介して水素捕縛膜へ水素を移動させる。具体的には、酸化物半導体膜を用いたトランジスタの下地膜または保護膜を、水素捕縛膜と水素透過膜との積層構造とする。このとき、水素透過膜を酸化物半導体膜と接する側に、水素捕縛膜をゲート電極と接する側に、それぞれ形成する。その後、加熱処理を行うことで酸化物半導体膜から脱離した水素を、水素透過膜を介して水素捕縛膜へ移動させることができる。

(もっと読む)

半導体装置

【課題】製造時以外にデータの追記が可能であり、書き換えによる偽造等を防止可能な不揮発の記憶装置及びそれを有する半導体装置を提供することを課題とする。また、信頼性が高く、安価な不揮発の記憶装置及び半導体装置の提供を課題とする。

【解決手段】絶縁表面上に形成される第1の導電層と、第2の導電層と、第1の導電層及び第2の導電層に挟持される第1の絶縁層と、第1の導電層の一部を覆う第2の絶縁層とを有し、第1の絶縁層は第1の導電層の端部、絶縁表面、及び第2の絶縁層を覆うことを特徴とする記憶装置である。

(もっと読む)

不揮発性半導体記憶装置

【課題】所定のレイアウト面積内において複数の抵抗値が得られる抵抗素子を有する不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板13上に配置された絶縁膜14と、絶縁膜14上に配置された導電層12と、導電層12上に配置された絶縁膜16と、絶縁膜16上に配置され、開口部を介して導電層12に接続された導電層11Aと、導電層11Aに接続されたコンタクト24Aと、絶縁膜16上に配置され、開口部を介して導電層12に接続された導電層11Bと、導電層11Bに接続されたコンタクト24Bと、絶縁膜16上に配置され、開口部を介して導電層12に接続された導電層11Cと、導電層11Cに接続されたコンタクト24Cとを備える。導電層12はフローティングゲート層と同じ材料から形成され、導電層11A、11B、11Cはコントロールゲート層と同じ材料から形成されている。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】クラックや結晶欠陥の発生なしに高電圧トランジスタの素子領域間の耐圧を向上できるようにした不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、メモリセル領域の第1素子分離絶縁層が当該メモリセル領域の第1素子分離溝内に第1の酸化膜を埋め込んで構成され、第1の酸化膜の上面が半導体基板の上面と第1ゲート電極の上面との間に存在するように構成されている。

周辺領域の第2素子分離絶縁層は、周辺領域の第2素子分離溝内の全体に埋込まれると共にその上面が半導体基板の上面の上方に突出した第1の酸化膜と、当該第1の酸化膜上に積層され、その上面が第1導電膜の上面より上方に突出している第2の酸化膜とで構成されている。

(もっと読む)

半導体装置

【課題】周辺回路領域を整形された形状とすることによりチップ面積を縮小する。

【解決手段】Y方向に延在する複数のデータバスDBがピッチP1でX方向に配列されたメモリセル領域40と、対応する複数のデータバスDBにそれぞれ接続された複数のバッファ回路BCが設けられたバッファ領域61とを備える。バッファ領域61上においては、Y方向に延在する複数のデータバスDBがピッチP2でX方向に配列され、ピッチP2はピッチP1よりも小さい。本発明によれば、データバスDBの配列ピッチをバッファ領域上において縮小していることから、他の回路ブロックに割当可能な面積を十分に確保することが可能となる。これにより、当該回路ブロックの幅拡大や形状の変形が不要となることから、無駄な空きスペースが生じにくく、チップ面積を縮小することが可能となる。

(もっと読む)

抵抗変化型不揮発性半導体記憶装置

【課題】相変化材料配線、抵抗変化材料配線の書き込み電流(Set、Reset電流)、読み出し電流を大幅に低減し、より微細化を可能にし、メモリセルサイズを縮小することを可能にする抵抗変化型不揮発性半導体記憶装置を提供すること。

【解決手段】カルコゲナイド配線GSTと、両端の各々に接続した抵抗配線と、前記抵抗配線のそれぞれの他端を、ソース、ドレインに接続したセルトランジスタとからメモリセルMCを構成し、前記メモリセルを複数直列接続し、一端を、ソースに接続し、ドレインをビット線に接続した選択トランジスタと、前記複数直列接続の他端をソース線に接続し、前記メモリセルのゲートをワード線に接続し、前記選択トランジスタのゲートとブロック選択線に接続したものからセルストリングを構成し、前記セルストリングを複数配設してメモリセルアレイを構成することを特徴とする相変化メモリ。

(もっと読む)

半導体装置及びその製造方法

【課題】キャパシタの高容量化と面積の低減を可能とした半導体装置及びその製造方法を提供する。

【解決手段】EEPROMメモリセル50は、シリコン基板1のメモリセル領域に設けられたN-層21aと、トンネル絶縁膜13aと、浮遊ゲート電極15aと、電極間絶縁膜

17aと、制御ゲート電極19aと、を有する。また、キャパシタ60は、シリコン基板1のキャパシタ領域に設けられた下部電極層24aと、第1の誘電体膜13cと、共通電極15cと、第2の誘電体膜17cと、上部電極19cと、を有する。下部電極層24aと第1の誘電体膜13cと共通電極15cとにより第1のキャパシタ61が構成されると共に、共通電極15cと第2の誘電体膜17cと上部電極19cとにより第2のキャパシタ62が構成されており、第1のキャパシタ61と第2のキャパシタ62とが並列に接続されている。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】安定した性能と高い生産性とを実現する不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態によれば、メモリセルアレイ部と、第1平面内においてメモリセルアレイ部と並置されたコンタクト部と、を備えた不揮発性半導体記憶装置が提供される。メモリセルアレイ部は、積層体、半導体層、メモリ膜を含む。積層体は、第1平面に対して垂直な第1軸に沿って積層された複数の電極膜とそれらの間の電極間絶縁膜とを含む。半導体層は電極膜の側面に対向する。メモリ膜は電極膜と半導体層との間に設けられ電荷保持層を含む。コンタクト部は、コンタクト部絶縁層と複数のコンタクト電極とを含む。コンタクト部絶縁層は、コンタクト部絶縁膜と粒子とを含む。コンタクト電極はコンタクト部絶縁層を第1軸に沿って貫通する。コンタクト電極は電極膜に接続される。

(もっと読む)

半導体記憶装置

【課題】メモリアレイの周辺に配置される周辺回路の専有面積を小さくすることができる半導体記憶装置を提供する。

【解決手段】実施形態に係る半導体記憶装置は、メモリアレイと、周辺回路と、を備える。メモリアレイは、複数のメモリセルと、複数のワード線と、複数のビット線と、を有し、4つのブロックを有する。周辺回路は、第1ブロックに属するワード線に接続された第1転送トランジスタと、第2ブロックに属する前記ワード線に接続された第2転送トランジスタと、第3ブロックに属するワード線に接続された第3転送トランジスタと、を含むトランジスタグループを有する。第1〜第3転送トランジスタにおいては、それぞれのソース及びドレインのいずれか他方を共有し、ソース及びドレインのいずれか一方と他方とをむすぶ方向が隣り合う転送トランジスタどうしで互いに90°または180°異なる。

(もっと読む)

半導体装置

【課題】実動作キャパシタとダミーキャパシタとが形成された半導体装置において、水素・水分、不均一なストレスによる実動作キャパシタの性能劣化を抑制し、FeRAMの寿命特性を向上する。

【解決手段】半導体基板10上の実動作キャパシタ部26の下部電極30と強誘電体膜32と上部電極34を有する複数の実動作キャパシタ36aと、半導体基板10上の実動作キャパシタ部26の外側のダミーキャパシタ部28の下部電極30と強誘電体膜32と上部電極34を有する複数のダミーキャパシタ36bと、複数の実動作キャパシタ36a上の複数の配線40と、複数のダミーキャパシタ36b上の配線40を有し、ダミーキャパシタ36bのピッチの実動作キャパシタ36aのピッチに対する比は、0.9〜1.1の範囲にあり、ダミーキャパシタ36b上の配線40のピッチの実動作キャパシタ36a上の配線40のピッチに対する比は、0.9〜1.1の範囲にある。

(もっと読む)

半導体装置の製造方法及びコンピュータ記録媒体

【課題】効率良く多段の良好な形状の階段状の構造を形成することのできる半導体装置の製造方法及びコンピュータ記録媒体を提供する。

【解決手段】第1の誘電率の第1の膜と、第1の誘電率とは異なる第2の誘電率の第2の膜とが交互に積層された多層膜と、多層膜の上層に位置しエッチングマスクとして機能するフォトレジスト層とを有する基板をエッチングして、階段状の構造を形成する半導体装置の製造方法であって、フォトレジスト層をマスクとして第1の膜をプラズマエッチングする第1工程と、水素含有プラズマにフォトレジスト層を晒す第2工程と、フォトレジスト層をトリミングする第3工程と、第3工程によってトリミングしたフォトレジスト層及び第1工程でプラズマエッチングした第1の膜をマスクとして第2の膜をエッチングする第4工程とを有し、第1工程乃至第4工程を繰り返して行うことにより、多層膜を階段状の構造とする。

(もっと読む)

半導体記憶装置

【課題】メモリセル面積を増大させることなく、配線間のカップリングノイズを低減可能な半導体記憶装置を提供する。

【解決手段】複数の連想メモリセルが行列状に配置されている。複数のワード線WLの各々は、各行に対応して配置され、連想メモリセルに接続されている。複数のマッチ線MLの各々は、各行に対応して配置され、連想メモリセルに接続されている。互いに隣合う第1の行と第2の行とにおいて第1の行のワード線WL2と第2の行のワード線WL1とが互いに隣合っており、かつ互いに隣合う第2の行と第3の行とにおいて第2の行のマッチ線ML1と第3の行のマッチ線ML0とが互いに隣合っている。

(もっと読む)

半導体装置及びその製造方法

【課題】高品質な半導体装置を提供する。

【解決手段】P型の半導体基板10と、半導体基板10内に形成されるNウェル11、半導体基板10内かつNウェル11上に形成されるPウェル12、及びPウェル12上に形成されるメモリセルトランジスタMTを含むCell領域と、半導体基板10内に形成されるNウェル14、及びNウェル上14に形成されるトランジスタHVP−Trを含むHVP−Tr領域と、半導体基板10上に形成されるトランジスタHVN―Trを含むHVN―Tr領域と、半導体基板10内に形成されるNウェル22、半導体基板10内かつNウェル22上に形成されるPウェル23、およびPウェル23上に形成されるトランジスタLVNE−Trを含むLVNE−Tr領域と、を具備し、Nウェル11及びNウェル22の底面の位置はNウェル14の底面の位置よりも低く、Nウェル14の底面の位置はPウェル12及びPウェル23の底面の位置よりも低い。

(もっと読む)

半導体装置

【課題】 高信頼動作の相変化メモリを実現する。

【解決手段】 本発明による半導体装置は、カルコゲナイド材料を用いた記憶層とダイオードで構成されたメモリセルを積層した構造のメモリアレイを有し、選択されたメモリセルが位置する層に応じて、初期化条件及び書き換え条件が変更されるものである。カレントミラー回路を動作に応じて選択するとともに、電圧選択回路とカレントミラー回路におけるリセット電流の制御機構により、初期化条件及び書き換え条件(ここでは、リセット条件)を動作に応じて変更する。

(もっと読む)

半導体メモリ装置および半導体メモリ装置の作製方法

【課題】高度に集積化したDRAMを提供する。

【解決手段】第1絶縁体101上にビット線102b、ビット線102b上に第2絶縁体103、第2絶縁体103上にストライプ状の第3絶縁体106a乃至106c等を形成し、第3絶縁体106bを覆って、半導体領域109bとゲート絶縁体110を形成する。ビット線102bと半導体領域109bは第1のコンタクトプラグ105a、105bで接続される。その後、導電性膜を形成し、これを異方性エッチングすることで、第3絶縁体106a乃至106cの側面にワード線111a乃至111dを形成し、第3絶縁体106bの頂部にキャパシタへ接続するための第2コンタクトプラグ115bを形成する。ワード線111b、111cを同期させることで、キャパシタに電荷を出入りさせる。このような構造でメモリセルの面積を4F2とできる。

(もっと読む)

不揮発性記憶素子および不揮発性記憶装置

【課題】電極と抵抗変化層の界面に小さな突起を形成することなく、低電圧での初期化が可能な不揮発性記憶素子を提供する。

【解決手段】下部電極105と上部電極107との間に介在され、両電極間に与えられる電気的信号に基づいて可逆的に抵抗値が変化する抵抗変化層116を備える。抵抗変化層116は、第1の抵抗変化層1161と第2の抵抗変化層1162との少なくとも2層から構成され、第1の抵抗変化層1161は第1の遷移金属酸化物116bから構成され、第2の抵抗変化層1162は、第2の遷移金属酸化物116aと第3の遷移金属酸化物116cとから構成され、第2の遷移金属酸化物116aの酸素不足度は第1の遷移金属酸化物116bの酸素不足度及び第3の遷移金属酸化物116cの酸素不足度のいずれよりも高く、第2の遷移金属酸化物116a及び第3の遷移金属酸化物116cは、第1の抵抗変化層1161と接している。

(もっと読む)

半導体メモリ装置

【課題】DRAMに必要なキャパシタの容量を低減し、高度に集積化したDRAMを提供する。

【解決手段】分割ビット線型DRAMにおいて、サブビット線をワード線の下に形成し、ビット線をワード線の上に形成する。分割ビット方式でサブビット線の寄生容量が低減し、かつ、セルトランジスタのオフ抵抗を必要に応じて高いものとすることによって、キャパシタの容量を通常のDRAMの1/10以下とすることができる。このため、スタック型キャパシタであっても、その高さを従来のものの1/10以下とできるので、その上にビット線を設けることも容易となる。また、セルトランジスタの構造を特殊なものとすることでメモリセルあたりの面積を4F2とできる。

(もっと読む)

81 - 100 / 362

[ Back to top ]