Fターム[5F083ZA12]の内容

半導体メモリ (164,393) | その他 (6,553) | メモリと独立機能ブロック (1,941) | メモリ+(ロジック、アナログ)LSI (844)

Fターム[5F083ZA12]に分類される特許

41 - 60 / 844

半導体装置

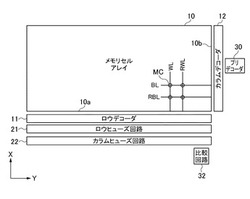

【課題】トリミング時間の短縮とヒューズ素子による占有面積の縮小を達成しつつ、高速アクセスを実現する。

【解決手段】不良ワード線のアドレスを記憶するロウヒューズ回路21と、不良ビット線のアドレスを記憶するカラムヒューズ回路22と、ロウアドレスXADD又はロウヒューズ回路21から読み出されたアドレスRXADDに基づいてワード線WL又は冗長ワード線RWLを選択するロウデコーダ11と、カラムアドレスYADD又はカラムヒューズ回路22から読み出されたアドレスRXADDに基づいてビット線BL又は冗長ビット線RBLを選択するカラムデコーダ12とを備える。ロウデコーダ11、ロウヒューズ回路21及びカラムヒューズ回路22はメモリセルアレイ10の長辺10aに沿って配置され、カラムデコーダ12はメモリセルアレイ10の短辺10bに沿って配置される。

(もっと読む)

半導体装置の作製方法

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける半導体装置を提供する。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタ102は、半導体特性を示す金属酸化物により設けられ、下部のトランジスタ100が有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、ゲート電極層と同一の層の一部を上部のトランジスタ102のバックゲートBGとして機能させる。下部のトランジスタ100は、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタ102のソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

半導体装置

【課題】ノーマリーオフのスイッチング素子を実現するトランジスタ構造およびその作製方法を提供する。トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する構成およびその作製方法を提供する。信頼性の高い半導体装置を提供する。

【解決手段】半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてインジウム、ガリウム、亜鉛、及び酸素の4元素を少なくとも含み、該4元素の組成比を原子百分率で表したとき、インジウムの割合が、ガリウムの割合及び亜鉛の割合の2倍以上である酸化物半導体層を用いる。

(もっと読む)

半導体装置

【課題】一定時間電力が供給されない状況でも記憶内容の保持が可能な半導体装置を提供すること。さらに、半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させること。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料として、ワイドバンドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、トランジスタの下に設けた配線層と、酸化物半導体膜の高抵抗領域と、ソース電極とを用いて容量素子を形成することで、トランジスタと容量素子の占有面積の低減を図る。

(もっと読む)

半導体記憶装置、および、ビット線の充電方法

【課題】低消費電力モードから通常動作モードへの復帰時におけるビット線の充電時間を適切に設定することで、復帰動作で消費される電力を低減する。

【解決手段】半導体記憶装置10は、複数のビット線2a,2b…のそれぞれを充電する充電回路4と、帰還経路5aの配線にダミービット線3が用いられているリングオシレータ5と、リングオシレータ5の発振回数が、複数のビット線2a,2b…の数に基づいて設定された所定の回数に達すると、検出信号を出力するカウンタ6と、低消費電力モードから通常動作モードへの復帰を指示する復帰信号に応じて、充電回路4による複数のビット線2a,2b…の充電を開始させるとともにリングオシレータ5の発振を開始させ、カウンタ6から出力された検出信号に応じて、充電回路4による複数のビット線2a,2b…の充電を終了させる制御回路7と、を有する。

(もっと読む)

不揮発性メモリ要素及びこれを含むメモリ素子

【課題】不揮発性メモリ要素及びこれを含むメモリ素子を提供する。

【解決手段】両電極の間にメモリ層を含み、該メモリ層は複数層構造を持つ不揮発性メモリ要素である。メモリ層は、ベース層及びイオン種交換層を含み、これらの間のイオン種の移動による抵抗変化特性を持つ。イオン種交換層は、少なくとも2つの層を含む複数層構造を持つ。不揮発性メモリ要素は、複数層構造のイオン種交換層によりマルチビットメモリ特性を持つ。ベース層は酸素供給層であり、イオン種交換層は酸素交換層である。

(もっと読む)

半導体装置

【課題】非接触でデータの送受信が可能な半導体装置は、鉄道乗車カードや電子マネーカ

ードなどの一部では普及しているが、さらなる普及のためには、安価な半導体装置を提供

することが急務の課題であった。上記の実情を鑑み、単純な構造のメモリを含む半導体装

置を提供して、安価な半導体装置及びその作製方法の提供を課題とする。

【解決手段】有機化合物を含む層を有するメモリとし、メモリ素子部に設けるTFTのソ

ース電極またはドレイン電極をエッチングにより加工し、メモリのビット線を構成する導

電層とする。

(もっと読む)

半導体装置

【課題】Y方向に隣接する2つの回路ブロックに対しX方向に延在する制御線からタイミング信号を同時に供給する。

【解決手段】例えば、Y方向に配列されたポートPT1,PT2と、ポートPT1,PT2にそれぞれ接続された回路C1,C2と、X方向に延在し回路C1,C2それぞれに含まれるサブ回路SC1,SC2を共通に制御する制御線CTL1を備える。サブ回路SC1,SC2のY方向における中間座標である座標Y1は、ポートPT1,PT2のY方向における中間座標Y0とは異なる。制御線CTL1からサブ回路SC1,SC2へのY方向における距離は互いに等しい。本発明によれば回路C1,C2の動作タイミングを正確に一致させることが可能となる。しかも、複数の制御線を必要とする場合であっても、制御線ごとに対応するサブ回路までの距離を一定とすることが可能となる。

(もっと読む)

不揮発性半導体記憶装置

【課題】アクセス性能の向上を図ることが可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、データバッファに格納されエラー訂正されたリードデータを第1の入出力ピンから出力するのに同期して、エラー訂正されたリードデータに対応する第1のパリティフラグを第2の入出力ピンから出力する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の一部にメタルゲート電極を有するMISEFTにおいて、メタルゲート電極を構成するグレインの配向性のばらつきに起因するMISFETのしきい値電圧のばらつきを小さくする。

【解決手段】メタルゲート電極4a、4bに炭素(C)を導入することにより、メタルゲート電極4a、4b内のグレインの粒径が大きくなることを防ぎ、メタルゲート電極4a、4bの中に多数の小さいグレインを形成することにより、グレインの配向性を均一化し、ゲート電極の仕事関数のばらつきを低減する。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜と該酸化物半導体膜と接する下地となる膜との界面の電子状態が良好なトランジスタ。

【解決手段】下地となる膜は酸化物半導体膜と同様の原子配列を有し、下地となる膜と酸化物半導体膜とが接している面において、面内の下地膜の最隣接原子間距離と酸化物半導体の格子定数の差を、下地となる膜の同面内における最隣接原子間距離で除した値は0.15以下、好ましくは0.12以下、さらに好ましくは0.10以下、さらに好ましくは0.08以下とする。例えば、立方晶系の結晶構造を有し(111)面に配向する安定化ジルコニアを含む下地となる膜上に酸化物半導体膜を成膜することで、下地となる膜の直上においても結晶化度の高い結晶領域を有する酸化物半導体膜が得られる。

(もっと読む)

半導体装置およびその製造方法

【課題】活性領域における上記プラグと、活性領域の外部における上記プラグとの双方を有する、微細化された半導体装置において、枠付け絶縁膜を確実に形成し、かつ導電性などの機能を最適化することが可能な半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、半導体基板SUBの主表面上に形成される活性領域と、平面視における活性領域の周辺に形成されるゲート接続領域と、活性領域上に形成される複数の第1のトランジスタTGに挟まれる領域に形成される、第1のトランジスタTGと第1のトランジスタTGよりも上側の層とを電気的に接続するための第1の接続層CTと、ゲート接続領域上に形成される第2のトランジスタTGと、第2のトランジスタTGよりも上側の層とを電気的に接続するための第2の接続層とを備えている。上記第1の接続層CTには第1の導電部PP1aと第2の導電部PP2aとを含み、第2の接続層SNCには第3の導電部PP2bを含む。

(もっと読む)

半導体装置

【課題】浮遊状態の配線と洗浄水との間において高い密度で電荷が移動することに起因する配線の高抵抗化を防ぐ。

【解決手段】半導体製造装置の製造工程中において、半導体基板1Sなどと絶縁された浮遊状態となる銅配線である第1層配線L1の上面に、電気的に機能する接続ビアPL2と電気的に機能しないダミービアDP2とを接続させて形成する。これにより、第1層配線L1の上面に接続ビアPL2を形成するためのビアホールを形成した後の洗浄工程中に、第1層配線L1に溜まった電荷が洗浄水中に移動する際、前記電荷をダミービアDP2形成用のビアホールにも分散させることで、接続ビアPL2形成用のビアホールの底部のみに前記電荷が集中することを防ぐ。

(もっと読む)

半導体装置

【課題】プロセス技術が比較的簡単、且つ、少ない素子数で多値情報を記憶することがでるメモリを提供する。

【解決手段】メモリ素子426において、第1の記憶素子における第1の電極417の形状の一部を、第2の記憶素子における第1の電極417の形状と異ならせることで、第1の電極417と第2の電極420の間の電気抵抗が変化する電圧値を異ならせて、1ビットを越える多値の情報の記憶を一つのメモリセルで行う。第1の電極417を部分的に加工することで単位面積当たりの記憶容量を増大することができる。

(もっと読む)

表示装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装

置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び

有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電

層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあ

わせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

半導体装置およびその製造方法

【課題】選択用トランジスタのゲート電極と記憶用トランジスタのゲート電極との間の耐圧を確保し、かつ閾値電圧の変動が抑制されたMONOS型メモリセルを提供する。

【解決手段】主表面SBSを有する半導体基板SUBと、主表面SBS上に形成された第1のゲート電極CGと、主表面SBS上において第1のゲート電極CGと隣接するように形成された第2のゲート電極MGと、第2のゲート電極MGと半導体基板SUBとに挟まれた領域から、第1のゲート電極CGと第2のゲート電極MGとに挟まれた領域に連なるように延びる第1の絶縁膜ONOとを備える半導体装置である。上記第2のゲート電極MGの最上面MGSは第1のゲート電極CGの最上面CGSより低くなっている。上記第2のゲート電極MGの最上面MGSは主表面SBSに沿うように形成されている。

(もっと読む)

記憶回路、信号処理回路、電子機器

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】酸化物半導体を用いて形成されたトランジスタと、該トランジスタのソース電極またはドレイン電極の一方と接続された容量素子を用いて、不揮発性の記憶回路を構成する。記憶回路に予めハイレベル電位を書き込んでおき、退避させるデータがハイレベル電位の場合は、そのままの状態を維持し、退避させるデータがローレベル電位の場合は、ローレベル電位を記憶回路に書き込むことで、書き込み速度を向上させた信号処理回路を実現できる。

(もっと読む)

記憶回路

【課題】短時間の電源停止により消費電力を抑えることができ、電源再開時において誤動作を引き起こすことなく初期化することのできる信号処理装置の記憶回路の提供を目的の一つとする。

【解決手段】記憶回路に電源が供給されない間は、揮発性記憶部に記憶していたデータ信号を、不揮発性記憶部に保持する。不揮発性記憶部では、オフ電流が極めて小さいトランジスタを用いることによって、容量素子に保持されたデータ信号は長期間にわたり保持する。こうして、不揮発性記憶部は電源の供給が停止した間も論理状態を保持する。また電源停止時に容量素子で保持されたデータ信号は、電源再開時にはリセット回路を導通状態とすることで、誤動作を引き起こすことのない電位にする。

(もっと読む)

記憶装置及び信号処理回路

【課題】電源の供給を停止しても、記憶している論理状態が消えない記憶装置を提供する。また、該記憶装置を用いることで、電源供給停止により消費電力を抑えることができる信号処理回路を提供する。

【解決手段】第1及び第2のノードを有する論理回路と、第1のノードに接続された第1の記憶回路と、第2のノードに接続された第2の記憶回路と、第1のノード、第2のノード、第1の記憶回路、及び第2の記憶回路に接続されたプリチャージ回路と、を有し、読み出しの際に、プリチャージ回路は、プリチャージ電位を第1のノード及び第2のノードに出力し、第1の記憶回路及び第2の記憶回路は、チャネルが酸化物半導体膜に形成されるトランジスタを含む記憶装置である。

(もっと読む)

半導体装置

【課題】貫通電極を用いた積層型の半導体装置において不良のある信号経路を救済する。

【解決手段】インターフェースチップIFと、互いに積層されたコアチップCC0〜CC7と、コアチップCC0〜CC7を貫通する複数の貫通電極TSV3により構成され、コアチップCC0〜CC7をインターフェースチップIFにそれぞれ個別に接続する複数の第1の信号経路と、コアチップCC0〜CC7を貫通する複数の貫通電極TSV1により構成され、コアチップCC0〜CC7をインターフェースチップIFに共通接続する第2の信号経路と、複数の第1の信号経路のいずれかを第2の信号経路に置換する切り替え回路110とを備える。本発明によれば、貫通電極の全てに切り替え回路を設ける必要がなくなる。また、救済のために追加する貫通電極の数も最小限に抑えられることから、チップ面積の増大を抑制することも可能となる。

(もっと読む)

41 - 60 / 844

[ Back to top ]