Fターム[5F083ZA12]の内容

半導体メモリ (164,393) | その他 (6,553) | メモリと独立機能ブロック (1,941) | メモリ+(ロジック、アナログ)LSI (844)

Fターム[5F083ZA12]に分類される特許

161 - 180 / 844

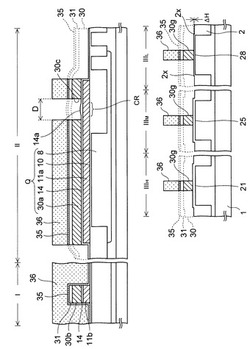

半導体装置の製造方法

【課題】半導体装置の製造方法において、半導体装置の小型化を図ること。

【解決手段】第1の領域IにフラッシュメモリセルFLを形成する工程と、第2の領域IIにキャパシタQの第1の電極11aを形成する工程と、第2の絶縁膜14として第1の酸化シリコン膜14a、窒化シリコン膜14b、及び第2の酸化シリコン膜14cをこの順に形成する工程と、第1の電極11aの一部領域CRにおける窒化シリコン膜14bと第2の酸化シリコン膜14cとを除去する工程と、第3の領域IIIHにおける第1の絶縁膜10と第2の絶縁膜14とをウエットエッチングする工程と、キャパシタQの第2の電極30aを形成する工程と、一部領域CRにおける第1の酸化シリコン膜14aをエッチングして除去する工程とを有する半導体装置の製造方法による。

(もっと読む)

不揮発性記憶装置

【課題】電源投入後、高速なセットアップが可能な不揮発性記憶装置を提供する。

【解決手段】不揮発性記憶装置は、データを不揮発的に記憶するメモリセルを有する第1および第2のメモリモジュール16−1、16−2と、第1および第2のメモリモジュールとそれぞれ接続されて、前記第1および第2のメモリモジュールを駆動するための外部電源を供給する第1および第2の外部電源線VL11、VL12とを備え、第1の外部電源線の電源容量C1は、前記第2の外部電源線の電源容量C2よりも小さい。

(もっと読む)

抵抗変化メモリ

【課題】大きい静電容量のキャパシタを含む抵抗変化メモリを提供する。

【解決手段】本実施形態の抵抗変化メモリは、アクティブ領域としての半導体領域20と、ゲート絶縁膜22を介して半導体領域21の側面に対向するゲート電極21とを有する選択トランジスタと、記憶するデータに応じて抵抗値が変化するメモリ素子1とを含むメモリセルMCと、第1のキャパシタ電極としての半導体領域30と、半導体領域30の側面に対向するキャパシタ電極31と、半導体領域20とキャパシタ電極31との間に設けられたキャパシタ絶縁膜32とを含むキャパシタ3と、を含む。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体素子のビア構造物及び導電構造物を提供する。

【解決手段】前記ビア構造物は、平坦部及び突出部を含む表面を有する。前記導電構造物は前記平坦部のうち、少なくとも一部上に形成され、前記突出部のうち、少なくとも一部上には形成されない。例えば、前記導電構造物は前記平坦部上のみに形成されて前記突出部上には全く形成されない。これによって、前記導電構造物と前記ビア構造物との間に高品質の接続を形成することができる。

(もっと読む)

相変化メモリコーディング

【課題】取り付け工程に係る半田付け及び高温環境での熱事象を通じても、データを保持することができる相変化メモリデバイスの提供。

【解決手段】一部のセルとメモリに第一抵抗状態、及び他部のセルとメモリに第二抵抗状態を誘導することにより、データセットを表わすために、プレコーディング(pre−coded)することができる。前記データセットがコーディングされ、基板に取り付けられた後に、前記第一及び前記第二抵抗状態を感知することにより、前記データセットを読み取り、前記第一抵抗状態を第三抵抗状態に変化させ、前記第二抵抗状態を第四抵抗状態に変化させる。半田接合と他の熱サイクルプロセスの後、前記第一及び前記第二抵抗状態は、感知マージン(sensing margin)を維持する。より高速とより低い電力を使用すると、前記第三及び前記第四抵抗状態は、転移(transition)を引き起こす能力がある。

(もっと読む)

半導体集積回路装置

【課題】設計工数をほとんど掛けないで、CMP対策及び短時間光アニール対策の両対策に最適化されたダミーパターンを有する半導体集積回路装置を提供すること。

【解決手段】基板上に、メモリマクロ領域10及び機能回路領域20を有する半導体集積回路装置1において、機能回路領域20間、及び、メモリマクロ領域10と機能回路領域20との間に配置されるとともにダミーパターン41を含むダミーパターン領域40を備え、ダミーパターン41は、前記メモリセルアレイ領域におけるメモリセルパターン11の拡散層12、13及びゲート電極14と同等のパターンであり、ダミーパターン領域40におけるダミー拡散層42、43及びダミーゲート電極44の面積率は、メモリセルアレイ領域における拡散層12、13及びゲート電極14の面積率と同等以上である。

(もっと読む)

パルス変換回路

【課題】回路面積を低減する。

【解決手段】第1の信号が入力され、第2の信号を出力する論理回路を具備し、論理回路は、ゲートに第1の信号が入力され、ゲートの電圧に応じて第2の信号の電圧を第1の電圧に設定するか否かを制御するP型トランジスタと、エンハンスメント型であり、閾値電圧の絶対値がP型トランジスタより大きく、ゲートに第1の信号が入力され、ゲートの電圧に応じて第2の信号の電圧を第1の電圧より高い第2の電圧に設定するか否かを制御するN型トランジスタと、を備え、P型トランジスタは、チャネルが形成され、第14族の元素を含有する半導体層を含み、N型トランジスタは、チャネルが形成され、キャリア濃度が1×1014/cm3未満である酸化物半導体層を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】追加のマスクや追加のプロセスを必要とせず、トランジスタを含む半導体装置に搭載することが可能なメモリ素子を実現する。

【解決手段】半導体装置を、絶縁膜17と金属膜又は金属化合物膜19とを積層した構造を有するメモリ素子16と、メモリ素子16と同一の積層構造を有するゲート構造を持つトランジスタとを備えるものとする。

(もっと読む)

半導体装置

【課題】相変化材料を用いたメモリセルを含む半導体装置において、書込み速度を律速しているセット動作を高速化することができる技術を提供する。

【解決手段】相変化材料に印加するセットパルス電圧を2段とし、相変化材料の温度を1段目の電圧で核生成の最も早くなる温度とし、2段目のパルスでは結晶成長の最も早くなる温度とし、相変化材料を溶かさずに固相成長させる手段を用いる。また、相変化材料に印加される2段パルス電圧は、ドレイン電流ばらつきが低減できるワード線に印加される2段の電圧により制御する手段を用いる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】歩留まりに優れた構造を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板と、基板上に形成されており、配線および絶縁層により構成された配線層が複数積層された多層配線層と、平面視において、基板内の記憶回路領域に形成されており、多層配線層内に埋め込まれた少なくとも1以上の容量素子および周辺回路を有する記憶回路と、平面視において、基板内の憶回路領域とは異なる領域である論理回路領域に形成された論理回路と、を備え、容量素子は、下部電極、容量絶縁膜、上部電極、埋設電極および、上部接続配線で構成されており、上部接続配線と埋設電極とは、同一の材料かつ一体に構成されており、上部接続配線と下部電極との間には、論理回路を構成する前記配線が少なくとも1以上設けられており、上部接続配線の上面と、上部接続配線と同じ配線層に形成された論理回路を構成する配線の上面とが、同一面を構成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子の平面形状を大きくせずに、その容量を大きくすることができ、かつ容量素子のリーク電流が増大することを抑制する。

【解決手段】下部電極410は、表層に、厚さが2nm以下の金属含有酸化層414を有している。金属含有酸化層414は、下部電極410の表面を酸化することにより形成されている。そして誘電膜420は、バルク状態において常温で出現する第1相と、バルク状態において第1相より高温で出現する第2相と、を含んでいる。第2相は第1相より比誘電率が高い。

(もっと読む)

半導体装置

【課題】内蔵メモリに連続したアドレスをそのまま入力していたので、領域のサイズを同じ値にしなければならなかった。このため、メモリサイズを大まかにしか設定することができず、リーク電流および消費電力を大幅に低減できなかった。本発明はリーク電流および消費電力を大幅に低減できる半導体装置を提供することを目的にする。

【解決手段】メモリをサイズが異なる複数の領域に分割して必要な領域のみ電力を供給するようにし、かつアドレス変換部を用いて連続したアドレスをメモリの実アドレスに変換するようにした。アドレス変換を行うので、サイズおよび電力を供給する領域を自由に設定できるので、リーク電流および消費電力を大きく低減できる。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、周辺回路領域のうち、メモリセル領域と周辺回路領域の境界付近に位置する領域において、多層的に配線層のレイアウトを行うことで、高集積化を実現することのできる半導体装置及びその製造方法を提供することを課題とする。

【解決手段】素子層16上であって、周辺回路領域12のうち、メモリセル領域11と周辺回路領域12との境界付近に位置する境界領域13に設けられた局所配線21と、素子層16上に設けられた複数の第1及び第2の下部電極95,96及び上部電極98を有するキャパシタ31と、複数の第1の下部電極95を連結すると共に、局所配線19の一部と対向する位置まで延出形成された第1のサポート膜26と、上部電極98とその上方に配置された第1の上部配線42とを連結すると共に、局所配線19の上方に位置し、かつ第1のサポート膜26に到達する第1のコンタクトプラグ37と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】高耐圧MISFETを含む半導体装置の信頼性向上を図ることができる技術を提供する。

【解決手段】高耐圧MISFETQ4のゲート絶縁膜GOX4を、酸化シリコン膜と窒化シリコン膜という異なる種類の膜から形成する。具体的に、高耐圧MISFETQ4では、ゲート絶縁膜GOX4を、酸化シリコン膜PREOX1と、この酸化シリコン膜PREOX1上に形成された酸化シリコン膜OX1と、酸化シリコン膜OX1上に形成された窒化シリコン膜SN1と、窒化シリコン膜SN1上に形成された酸化シリコン膜OX2から形成している。

(もっと読む)

抵抗変化素子及びその製造方法、並びに半導体装置及びその製造方法

【課題】低動作電圧を実現すると共に、スイッチング電圧のばらつきを低減した抵抗変化素子及びその製造方法、並びに半導体装置及びその製造方法を提供すること。

【解決手段】抵抗変化素子は、第1電極と、第1電極に接し、電圧の印加により抵抗が変化する抵抗変化層と、抵抗変化層に接する第2電極と、を備える。抵抗変化層は、高密度層と、高密度層より低密度の低密度層を有する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルに書き込み用のトランジスタ、読み出し用のトランジスタおよび選択用のトランジスタを備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体装置の製造方法

【課題】シリンダ状下部電極の型材となる犠牲層間絶縁膜を除去する際に、倒壊を防止する梁が形成されることで、梁と下部電極の接続部でキャパシタのリーク電流が増加する。

【解決手段】梁となる層、例えばカーボン膜86を介装した犠牲層間絶縁膜24にシリンダホールを形成し、シリンダ孔内にキャパシタの下部電極51を形成し、続いて、犠牲層間絶縁膜24をウェットエッチングにて選択的に除去した後、カーボン膜86をドライ条件で選択的に除去する。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】多層配線構造を使って、キャパシタンスが大きく、かつキャパシタンス値が安定なキャパシタ素子を半導体基板上に集積化する。

【解決手段】多層配線構造18は、少なくとも第1層目の層間絶縁膜16と、第1層目の層間絶縁膜中に埋設された第1配線層と、を含み、第1配線層は、第1の電源に接続され前記第1の層間絶縁膜中に埋設された第1の配線パタ―ン15C1と、第2の電源に接続され前記第1の層間絶縁膜中に埋設された第2の配線パタ―ン15C2と、を含み、第1の配線パタ―ンと前記第2の配線パタ―ンとは容量結合して第1のキャパシタを形成し、第1の配線パタ―ンは積層配線パタ―ン13C上に形成されて、前記第4の電極パターン13Gと容量結合して第2のキャパシタを形成し、第4の電極パターンは第2の配線パタ―ンに電気的に接続されている。

(もっと読む)

限られたチャージ拡散を有するチャージトラップメモリ

【課題】隣接メモリセルへの漏洩電流を減らすフラッシュメモリ、特にチャージトラップメモリおよびそれを形成するプロセスフローの提供。

【解決手段】セルチャンネル620を含む半導体線が、STI領域120上に形成される。セルチャンネルは、トンネル酸化物層621、トラッピング誘電体層623、およびブロッキング誘電体層628を含む活性誘電体スタックで覆われる。結果として得られるセルチャンネルを分離するトレンチ625は、伝導層460で少なくとも部分的に充填され得る。活性誘電体層および/または伝導層の部分は、セルチャンネルの下、たとえば、セルチャンネルおよびSTI領域の間の界面695の下に位置し得る。そのような構成は、活性誘電体スタックおよび/または半導体層がセルチャンネルの下に位置しない構成に比べて、あるセルチャンネルから隣接セルチャンネルに拡散する荷電粒子670に対して経路長の増大をもたらす。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】シリコン抵抗とメモリ回路とを混載した半導体装置において、メモリの情報の保持時間を長くして、かつ書込・読出時間を短くする。

【解決手段】容量素子400はメモリセルを構成しており、第1トランジスタ200は、ソース及びドレインとなる第1拡散層226が容量素子400に接続している。シリコン抵抗素子300はシリコン層からなる。第1拡散層226はシリサイド層を有していない。また第1ゲート電極230は、金属層232及びシリコン層234を積層した積層構造を有している。そして第1ゲート電極230は、素子分離膜50上に位置する領域の少なくとも一部にシリサイド層235を有しており、かつ第1拡散層226に挟まれた領域にはシリサイド層を有していない。そしてコンタクト513は、シリサイド層235を介して第1ゲート電極230に接続している。

(もっと読む)

161 - 180 / 844

[ Back to top ]