Fターム[5F083ZA23]の内容

Fターム[5F083ZA23]の下位に属するFターム

窓/開口を有するもの (5)

リードフレーム (23)

Fターム[5F083ZA23]に分類される特許

101 - 120 / 222

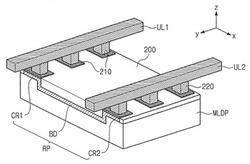

抵抗素子を有する半導体装置及びその製造方法

【課題】基準電圧を調整する回路を構成する抵抗素子を有するフラッシュ記憶素子である半導体装置及びその製造方法を提供する。

【解決手段】フラッシュ記憶素子である半導体装置の製造方法は、半導体基板上にトレンチを定義する鋳型パターンMLDPを形成し、鋳型パターンMLDP上にトレンチを横切る抵抗パターンRPを形成し、抵抗パターンRP上に互いに離隔された第1及び第2導電パターン210、220を形成し、第1及び第2導電パターン210、220に各々接続する第1及び第2配線UL1,UL2を形成する段階を有し、第1及び第2導電パターンUL1,UL2は鋳型パターンMLDPの上部に各々形成される。

(もっと読む)

メモリ半導体装置、その製造方法、及び動作方法

【課題】メモリ半導体装置、その製造方法及び動作方法を提供する。

【解決手段】メモリ半導体装置は、基板の上部面に垂直長軸を有し、2次元的に配列される複数の半導体パターン、及び複数の半導体パターンを横切る長軸を有しながら、複数の半導体パターン間で3次元的に配列される複数のワードラインを包含できる。

(もっと読む)

半導体メモリー装置のチャンネルをプリチャージする方法

【課題】プログラムディスターバンスが効果的に遮断されて高いデータ信頼性を有する3次元半導体メモリー装置のチャンネルをプリチャージする方法を提供する。

【解決手段】本発明による半導体メモリー装置のプログラム方法は、複数のビットラインの中でプログラムビットラインに連結される少なくとも1つのインヒビットストリングのチャンネルと、インヒビットビットラインに連結されるインヒビットストリングの中で少なくとも何れか1つのチャンネルとを共通ソースラインに供給されるプリチャージ電圧に充電する段階と、ワードライン電圧を複数のセルストリングに供給してプリチャージされたチャンネルをブースティングさせる段階と、を有する。

(もっと読む)

半導体装置

【課題】複数の被制御チップを積層して構成される積層半導体装置では、制御チップが積層半導体層の外部に設けられており、被制御チップと制御チップとの間のデータ転送による遅延等が問題となっている。

【解決手段】制御チップと共に複数の被制御チップを積層し、制御チップは、それぞれの被制御チップに異なるI/Oセットをアサインし、複数のI/Oセットを同一のアクセスサイクルで処理するシステムインパッケージにおいて、制御チップに近い下位の被制御チップのI/O貫通電極に関連する貫通配線は、使用されることのない上位の被制御チップまで延伸されることによって、すべての被制御チップで使用するそれぞれの貫通配線を等長配線とする半導体装置が得られる。

(もっと読む)

高性能メモリ用およびロジック用パッケージ半導体デバイス

【課題】 メモリデバイスとロジック回路間の待ち時間を最小化するとともに組み立てに有利なデバイスを提供すること。

【解決手段】 パッケージ半導体デバイスが開示される。本デバイスは、対向配置された第1の面と第2の面間の複数層と、少なくとも1つの集積回路メモリデバイスを入れ子式に組み込むための第1の面に開口を有するキャビティとを有する基板を含む。ロジック回路は第2の面上に配置され、積層された集積回路メモリデバイスに電気的に接続するための接点を含む。ロジック回路は、基板の複数層内に形成された、導電性トレースとビアとを含む第1の電気経路を介して、第1の面上に形成された電気接点に接続される。

(もっと読む)

3次元メモリー装置、及びそのプログラム方法

【課題】集積度の増加と共にプログラムディスターバンス問題を効果的に減らすことができる3次元メモリー装置、及びそのプログラム方法が提供される。

【解決手段】本発明の3次元メモリー装置は、複数のワードライン平面が積層されたメモリーセルアレイ、選択されたワードライン平面に具備された少なくとも2以上のページのメモリーセルを同時にプログラムする書込み読出し回路、そして前記書込み読出し回路のプログラム動作を制御する制御回路を含むことができる。

(もっと読む)

半導体装置

【課題】半導体チップがパッケージに実装された状態でのヒューズ専用端子を不所望に増加させることなく、最終テスト工程での電気ヒューズ溶断を実現する。

【解決手段】第1パッド(P1)、第2パッド(P3)、第3パッド(P2)を半導体チップに設ける。上記第1パッドと上記第3パッドとの間には、所定電圧が印加されることでプログラミング可能な第1ヒューズ素子を有する第1ヒューズ部(WFM)を設ける。上記第2パッドと上記第3パッドとの間には、所定電圧が印加されることでプログラミング可能な第2ヒューズ素子を有する第2ヒューズ部(PFM)を設ける。上記第2パッドに結合された第1端子(T3)と、上記第3パッドに結合された第2端子(T2)をパッケージに設ける。上記第1端子は、上記第2端子とは電気的に独立しており、上記第1端子を介して、上記第2ヒューズ部にヒューズ溶断のための電圧を印加することができる。

(もっと読む)

3次元垂直チャンネル構造を有する不揮発性メモリ装置のプログラム方法

【課題】本発明は、ビットラインとストリング選択ラインとの交差領域に各々形成され、各々が基板上に垂直に多層構造で形成されたメモリセルを有するストリングを含む不揮発性メモリ装置のプログラム方法を提供する。

【解決手段】本発明のプログラム方法によると、シャドープログラム方式によってYZ平面の各層に属したメモリセルがマルチビットデータにプログラムされ、YZ平面のN番目の層(ここで、Nは1、またはそれより大きい定数)のメモリセルがプログラムされる場合、YZ平面の他層のメモリセルがプログラムされる前にN番目の層に対応するXZ平面の残りのメモリセルがプログラムされる。

(もっと読む)

半導体装置

【課題】回路に発生したノイズが接地電位供給配線を介して他の回路に流れるのを防いだ半導体装置を提供する。

【解決手段】第1および第2のパッド列と、第1のパッド列の近くに設けられた第1の配線に接続された第1の接地電位供給電極と、第2のパッド列の近くに設けられた第2の配線に接続された第2の接地電位供給電極とを有し、第1のパッド列は、チップ内の第1の回路に接続され、第1のボンディングワイヤを介して第1の配線と接続された第1のパッドと、チップ内の第2の回路に接続され、第2のパッド列をまたぐ第2のボンディングワイヤを介して第2の配線と接続された第2のパッドとを含む構成である。

(もっと読む)

メモリモジュール及びこれを備えるメモリシステム

【課題】高いデータ転送レートを実現可能なLoad Reduced型のメモリモジュールを提供する。

【解決手段】モジュール基板110に搭載されたメモリチップ200、データレジスタバッファ300及びコマンド/アドレスレジスタバッファ400を備える。データレジスタバッファ300は、メモリチップ200との間でデータ転送を行う。コマンド/アドレスレジスタバッファ400は、コマンド/アドレス信号をバッファリングするとともに、コントロール信号を生成する。バッファリングされたコマンド/アドレス信号は、メモリチップ200に供給され、コントロール信号はデータレジスタバッファ300に供給される。本発明によれば、データレジスタバッファ300とメモリチップ200との配線距離が短くなることから、非常に高いデータ転送レートを実現することが可能となる。

(もっと読む)

メモリモジュール

【課題】高いデータ転送レートを実現可能なLoad Reduced型のメモリモジュールを提供する。

【解決手段】モジュール基板110の長辺に沿って設けられた複数のデータコネクタ120と、モジュール基板110に搭載されたメモリチップ200及びデータレジスタバッファ300と、データコネクタ120とデータレジスタバッファ300とを接続するデータ配線L0と、データレジスタバッファ300とメモリチップ200とを接続するデータ配線L1,L2とを備える。各データレジスタバッファ300と、これに対応するデータコネクタ120及びメモリチップ200は、モジュール基板110の短辺方向に並べて配置されている。本発明によれば、データ配線の配線距離が非常に短くなることから、非常に高いデータ転送レートを実現することが可能となる。

(もっと読む)

パッケージされた集積回路装置及びその動作方法とこれを有するメモリ保存装置及び電子システム

【課題】減少した信号スキューを提供するマルチチップ・パッケージされた集積回路装置及びその動作方法を提供する。

【解決手段】本発明のパッケージされた集積回路装置は、導電性パッドを上に含む基板と、基板上に複数のチップを含むチップスタックと、1次導電性ラインと、2次導電性ラインと、を備える。1次導電性ラインは、基板上の導電性パッドと、チップスタックの複数のチップのうちの一つの上に設けられた導電性パッドとを電気的に連結する。2次導電性ラインは、チップスタック内の複数のチップのうちの一つの上に設けられた導電性パッドを、その上側にある複数のチップのうちの一つ、及び下側にある複数のチップのうちの一つの上に設けられた対応する導電性パッドに電気的に連結する。

(もっと読む)

積層メモリ素子

【課題】集積度を高めることが容易な3次元積層された多層構造メモリ素子を提供する。

【解決手段】本積層メモリ素子は、基板と、基板上に相互積層され、複数の群に分割された複数のメモリ層と、各群内のメモリ層と電気的に接続され、各群内のメモリ層の間に配された複数のインターデコーダと、複数のインターデコーダと電気的に接続され、複数のインターデコーダの間に配された少なくとも一つのプレデコーダと、を備えることを特徴とする。

(もっと読む)

他の素子からの電流を使用する不揮発性記憶素子のプログラミング

不揮発性記憶装置は、Y線の組と、共通X線と、それぞれが共通X線に接続された複数のデータ記憶素子と、共通X線及び特定のY線に接続されたダミー記憶素子と、共通X線及びY線の組と通信する制御回路を有している。複数のデータ記憶素子は、第1状態又は第2状態になることができる。ダミー記憶素子は、導電状態にある。制御回路は、ダミー記憶素子を介して特定のY線から第1のデータ記憶素子に電流を流すことによって、複数のデータ記憶素子のうちの第1データ記憶素子を第1状態から第2状態に変化させるために、制御信号を共通X線及びY線の組に供給する。制御回路は、複数のデータ記憶素子のうちの第2状態に予め変化させられているデータ記憶素子とこれらに関連付けられた異なるY線から複数のデータ記憶素子のうちの付加的なデータ記憶素子へ電流を流すことによって、付加的なデータ記憶素子を第1状態から第2状態に順次に変化させるために、制御信号を共通X線及びY線の組に供給する。  (もっと読む)

(もっと読む)

半導体基板、積層チップパッケージおよび半導体プレート並びにこれらの製造方法

【課題】積層チップパッケージの製造工程を簡略化し得る構造を備えた半導体基板、積層チップパッケージおよび半導体プレート並びにこれらの製造方法を提供する。

【解決手段】半導体基板は、スクライブラインに沿って複数の溝部が形成されている。半導体基板は、複数の溝部に形成されている絶縁層と、複数の溝部のいずれか少なくとも1つに接する矩形状の単位領域と、その単位領域から溝部の内側に延出された延出端子部を備えた配線電極とを有している。半導体基板は、スクライブラインに沿って複数の溝部を形成し、複数の溝部に絶縁材を埋め込み平坦化して絶縁層を形成し、複数の溝部のいずれか少なくとも1つに接する矩形状の単位領域から溝部の内側に延出された延出端子部を備える配線電極を形成することによって製造する。

(もっと読む)

超高帯域メモリのダイスタック

【課題】 3次元ダイスタックを用いて形成されたメモリを提供する。

【解決手段】 システムは、中央処理装置(CPU)、CPUと連絡し、複数の垂直に積層された集積回路チップと複数の入力/出力(I/O)ポートを含み、各I/Oポートは、基板貫通ビアによって複数のチップの少なくとも1つに接続されるメモリデバイス、及び

CPUと前記メモリデバイスと連絡し、メモリデバイスにデータを伝送、またはメモリデバイスから伝送するのを管理するように構成するダイレクトメモリアクセス(DMA)コントローラを含むシステム。

(もっと読む)

半導体メモリ

【課題】メモリセルの微細化と信頼性の向上とを図る。

【解決手段】本発明の例に係る半導体メモリは、アクティブエリアAA1,AA2,・・・と素子分離エリアとが第1方向に交互に配置される周期構造を備える。第1方向の最端部からm(mは2以上の数)番目以降のアクティブエリア上には、第1ゲート絶縁膜が形成され、第1方向の最端部からm番目未満のアクティブエリア上には、第1ゲート絶縁膜よりも厚い第2ゲート絶縁膜が形成される。素子分離絶縁膜は、第1方向の最端部からm−1番目とm番目のアクティブエリアの間に段差を有する。第1方向において、m−1番目とm番目のアクティブエリアの間の素子分離絶縁膜の幅は、m番目とm+1番目のアクティブエリアの間の素子分離絶縁膜の幅よりも広い。

(もっと読む)

半導体装置

【課題】微細化が進んだ半導体装置の短チャネル効果を防ぎ、特性を向上させることができる半導体装置の提供を課題とする。

【解決手段】単結晶シリコン基板上に形成された酸化膜と、酸化膜上に形成された単結晶シリコン層と、単結晶シリコン層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極を有する半導体装置であって、単結晶シリコン層はチャネル形成領域、ソース領域、ドレイン領域を有し、チャネル形成領域には、ソース領域、ドレイン領域とは逆の導電型の不純物元素が添加され、チャネル形成領域の不純物元素が添加された領域は、上面から見て主軸がソース領域からドレイン領域にかけて伸びるフィッシュボーン形状を有し、フィッシュボーン形状は単結晶シリコン層の表面から底部にかけて形成され、チャネル形成領域の不純物元素が添加された領域は、空乏層を抑止する機能を有することを特徴としている半導体装置を提供する。

(もっと読む)

除去可能な補助検査端子を有するソリッドステート・ドライブの検査方法

【課題】除去可能な補助検査端子を有するソリッドステート・ドライブの検査方法を提供する。

【解決手段】除去可能な補助検査端子を有するソリッドステート・ドライブの検査方法において、該ソリッドステート・ドライブのメモリ半導体素子に不良が発生した場合、不良分析のために検査端子が設けられた補助ボードを別途に使用して除去するか、又は印刷回路基板の一側面エッジにメモリ半導体素子を検査可能な印刷回路パターンと接続された貫通ホールを設け、不良発生時に、前記貫通ホールが露出されるように、印刷回路基板の一部を切断し、メモリ半導体素子に対する不良分析を実施する。従って、印刷回路基板に搭載されたメモリ半導体素子を取り外さずに不良分析を実施することが可能である。

(もっと読む)

不揮発性半導体記憶装置およびその閾値制御方法

【課題】信頼性よく、かつ高速にメモリセルにデータを書き込むことができる。

【解決手段】NOR型フラッシュメモリは、第1〜第4の電源切替部135〜138を備える。第1の電源切替部135は、ロウデコーダ115内の第1のプリデコーダ131に対して専用の電源電圧VSWiを供給するため、電源電圧VSWiの負荷容量が小さくなり、選択ワード線WL電圧の遷移速度が向上する。また、第2の電源切替部136は、第2のプリデコーダ132、ロウメインデコーダ133およびロウサブデコーダ134に対して、書き込み時とベリファイ読み出し時で電圧レベルが変化しない電源電圧VSW2iを供給するため、電源電圧VSW2iの負荷容量が大きくても書き込み時間には大きく影響しない。これにより、書き込みとベリファイ読み出し間の選択ワード線WL電圧の切替を迅速に行うことができる。

(もっと読む)

101 - 120 / 222

[ Back to top ]