Fターム[5F083ZA23]の内容

Fターム[5F083ZA23]の下位に属するFターム

窓/開口を有するもの (5)

リードフレーム (23)

Fターム[5F083ZA23]に分類される特許

61 - 80 / 222

半導体装置

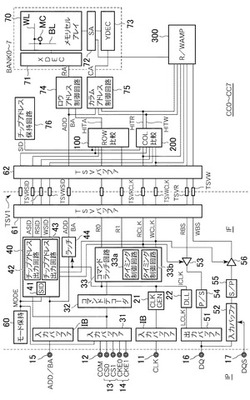

【課題】複数のランクに分類された積層型の半導体装置において、異なるランクに対して連続アクセスされた場合のデータの衝突を防止する。

【解決手段】ライトデータを伝送する貫通電極TSVWとリードデータを伝送する貫通電極TSVRとをそれぞれ有する互いに積層された複数のコアチップCC0〜CC7と、これらコアチップCC0〜CC7に共通接続されたインターフェースチップIFとを備える。インターフェースチップIFは、データ入出力端子16と、データ入出力端子と貫通電極TSVWとの間に設けられた52入力バッファと、データ入出力端子16と貫通電極TSVRの間に設けられた出力バッファ51とを有する。本発明によれば、ライトデータとリードデータを互いに異なる貫通電極を介して伝送していることから、異なるランクに対して連続アクセスされた場合であってもデータの衝突が生じない。

(もっと読む)

半導体装置

【課題】積層型の半導体装置においてインターフェースチップからコアチップへのクロック信号の供給を不要とする。

【解決手段】外部から供給されるコマンド信号CMD及びクロック信号CKを受けて、各々がクロック信号CKに同期し、且つ、互いにタイミングが異なる複数のリード制御信号R1,R2を出力するリードタイミング制御回路100を有するインターフェースチップIFと、インターフェースチップIFに積層され、コマンド信号CMDが示す動作をリード制御信号R1,R2に同期してそれぞれ実行する複数の内部回路を有するコアチップCC0〜CC7とを備える。本発明によれば、コアチップに内でのレイテンシ制御が不要となることから、コアチップにクロック信号を供給する必要がなくなる。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】有機基板の使用量を抑えて、製造コストの抑制を図ることのできる半導体記憶装置を提供すること。

【解決手段】半導体記憶装置10は、一方の面に外部接続端子が設けられ、外部接続端子が設けられる領域と略同じ平面形状に個片化された有機基板11と、有機基板11に対して相対的に位置決めされた載置領域21を有するリードフレーム13と、載置領域21に接着された半導体メモリチップ15と、を備えることを特徴とする。

(もっと読む)

3次元半導体記憶素子

【課題】優れた信頼性を有し、高集積化のために最適化された3次元半導体記憶素子が提供される。

【解決手段】本発明の素子によれば、積層構造体が基板上に配置されて第1の方向に延長される。積層構造体は交互に反復的に積層されたゲートパターン及び絶縁パターンを含む。垂直形活性パターンが積層構造体を貫通する。積層構造体は第1の部分及び第2の部分を含み、積層構造体の第2の部分は第1の方向と垂直である第2の方向に第1の部分より小さい幅を有する。積層構造体の第2の部分の横にストラッピングコンタクトプラグが配置されて、共通ソース領域と接触される。

(もっと読む)

半導体装置及びその製造方法、並びにデータ処理システム

【課題】メモリセル領域に埋め込みゲート電極を有し、周辺回路領域にプレーナ型ゲート電極と貫通電極を有する半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、半導体基板50のメモリセル領域の溝部内に第一のゲート絶縁膜を介して、ワード線を埋め込み形成する工程と、周辺回路領域の前記半導体基板50上に、第二のゲート絶縁膜を介して周辺ゲート電極を形成する工程と、前記半導体基板50の主面上に層間絶縁膜と金属膜とを形成したのちに、前記金属膜をパターニングして、前記メモリセル領域の容量コンタクトパッドと前記周辺回路領域の局所配線127とを同時に形成する工程と、前記局所配線127の下面127a側を露出する開口151を形成したのちに導電体を充填することにより貫通プラグを形成する工程と、を採用する。

(もっと読む)

積層チップパッケージおよびその製造方法

【課題】簡単な構成で、複数の積層チップパッケージを積層し互いに電気的に接続することを可能にし、所望の数の半導体チップを含むパッケージを低コストで実現する。

【解決手段】積層チップパッケージ1Sは、本体2を備え、本体2は、主要部分2Mと、主要部分2Mの上面、下面に配置された複数の第1の端子4、第2の端子5を有している。主要部分2Mは、2つの階層部分10S1,10S2と、これらを貫通する複数の貫通電極Tを含んでいる。複数の貫通電極Tは、複数の端子4,5に電気的に接続されている。各階層部分は、第1の面と第2の面を有する半導体チップと、複数の表面電極を含んでいる。階層部分10S1,10S2は、第2の面同士が対向するように接合されている。端子4は階層部分10S1の表面電極を用いて構成され、端子5は階層部分10S2の表面電極を用いて構成されている。

(もっと読む)

半導体装置、および、その製造方法、電子機器

【課題】製造効率の向上、コストダウン、信頼性の向上、小型化を容易に実現させる。

【解決手段】各配線111h,211hにおいて、第1半導体チップ100および第2半導体チップ200の側端部にて露出した側面を、導電層401で被覆される。これにより、導電層401によって両配線111h,211hの間が電気的に接続させる。

(もっと読む)

半導体記憶装置

【課題】樹脂モールド部を外部に露出させて、部品点数の削減や製造コストの削減を図ることのできる半導体記憶装置を提供すること。

【解決手段】実施の形態の半導体記憶装置10は、半導体メモリチップ15を樹脂モールド部18でモールドした半導体記憶装置であって、樹脂モールド部にモールドされて半導体メモリチップが載置されるプレート21と、半導体記憶装置の外周面に露出される外部接続端子19と、を備え、プレートは、樹脂モールド部の外周面に露出する複数の露出部21bを有し、複数の露出部同士は、樹脂モールド部の内部で互いに電気的に絶縁される。

(もっと読む)

メモリ装置

【課題】空きソケットとなっている第2ソケットでの信号の反射を抑制可能なメモリ装置を提供する。

【解決手段】メモリモジュール2が接続されたソケット3と、空きソケットとなっているソケット4と、コントローラ5とは、接続配線6によって接続されている。接続配線6は、ソケット3とコントローラ5とを接続する配線6aと、配線6aから分岐点6bで分岐しソケット4と接続する配線6cと、を備える。配線6cには、ダミー配線7の一端7aが接続され、ダミー配線7の他端7bは、終端抵抗8に接続されている。

(もっと読む)

垂直的に集積された不揮発性記憶セルサブストリングを含む不揮発性記憶装置の形成方法、及び形成された不揮発性記憶装置

【課題】 セルの電気的特性の均一性を向上させ得る3次元不揮発性記憶装置及びその形成方法を提供する。

【解決手段】 本発明の不揮発性記憶装置の形成方法は不揮発性記憶セルが高集積化された垂直的積層を形成するための段階を含む。不揮発性記憶セルでは、直列に電気的に連結される複数の垂直サブストリングを使用して記憶セルが半導体基板上に垂直に積層される。このとき、記憶セルの垂直方向の積層は劣等に作用するメモリセルストリングが発生しないように、製造工程において補正するためにダミー記憶セルを利用する。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体素子及びその製造方法を提供する。

【解決手段】基板上で第1方向に延在するラインパターンと、ラインパターンの端部から、第1方向と異なる方向に延在する分岐ラインパターンとをそれぞれ含む第1導電ライン;第2導電ライン;第3導電ラインとを含む半導体素子であり、中間に位置する導電ラインの分岐ラインパターンは、他の導電ラインの分岐ラインパターン間に位置し、長さもさらに短い。これにより、コンタクト・パッドが、導電ラインの分岐ラインパターンと一体に形成されうる。

(もっと読む)

相変化メモリコーディング

【課題】取り付け工程に係る半田付け及び高温環境での熱事象を通じても、データを保持することができる相変化メモリデバイスの提供。

【解決手段】一部のセルとメモリに第一抵抗状態、及び他部のセルとメモリに第二抵抗状態を誘導することにより、データセットを表わすために、プレコーディング(pre−coded)することができる。前記データセットがコーディングされ、基板に取り付けられた後に、前記第一及び前記第二抵抗状態を感知することにより、前記データセットを読み取り、前記第一抵抗状態を第三抵抗状態に変化させ、前記第二抵抗状態を第四抵抗状態に変化させる。半田接合と他の熱サイクルプロセスの後、前記第一及び前記第二抵抗状態は、感知マージン(sensing margin)を維持する。より高速とより低い電力を使用すると、前記第三及び前記第四抵抗状態は、転移(transition)を引き起こす能力がある。

(もっと読む)

半導体メモリ装置

【課題】積層された複数のメモリチップからなる積層メモリチップとメモリコントロールチップとを基板上に並置した構成のMCP型半導体メモリ装置において、パッケージサイズの更なる小面積化を実現する。

【解決手段】

半導体メモリ装置は、積層された複数のメモリチップからなる積層メモリチップと、積層メモリチップを搭載する基板と、基板上に積層メモリチップに隣接して搭載されたメモリコントロールチップと、を含む。積層メモリチップは、上方のメモリチップが直下のメモリチップに対してメモリコントロールチップの搭載位置に向けてずらした状態で積層されて構成される。積層メモリチップのメモリコントロールチップに向けて迫り出した部分と基板との間の空間にメモリコントロールチップの少なくとも一部が侵入している。

(もっと読む)

半導体記憶装置とその製造方法

【課題】不揮発性半導体メモリチップや、コントローラで発生する熱の効率的な放熱を図ることのできる半導体記憶装置とその製造方法を提供すること。

【解決手段】半導体記憶装置20は、複数の不揮発性半導体メモリチップおよび不揮発性半導体メモリチップへのデータの読み書きを制御するコントローラチップが一方の面に実装されたプリント回路板と、導電性材料で形成され、プリント回路板を収容する筐体4と、筐体の内側面に設けられ、コントローラチップと筐体との隙間または不揮発性半導体メモリチップと筐体との隙間を囲む囲い部18と、囲い部の内側に設けられ、不揮発性半導体メモリチップまたはコントローラチップと、筐体との両方に接するゲル部材22と、を備える。

(もっと読む)

半導体メモリチップ、半導体集積回路、半導体パッケージ、半導体メモリ装置、半導体装置パッケージの製造方法、および半導体装置の製造方法

【課題】3D半導体装置を提供する。

【解決手段】半導体メモリチップであって、データチップパッドと、データチップパッドに連結されるデータ入力バッファと、データ入力バッファに連結され、データ入力バッファから出力されるデータをラッチするラッチと、メモリセル・アレイと、を具備し、データ入力バッファとラッチは、データチップパッドからメモリセル・アレイまでの第1データ書き込み経路の部分であり、半導体メモリチップは、第1データ書き込み経路の電気的なノードに電気的に連結され、第1データ書き込み経路の一部分を含む第2データ書き込み経路を形成する貫通電極をさらに具備し、第2データ書き込み経路は、データチップパッドとは異なるチップ・ターミナルから、メモリセル・アレイまで拡張される。

(もっと読む)

不揮発性半導体記憶装置

【課題】積層されるチップ数が増加した際にワイヤボンディング数の増加を抑制でき、さらにインダクタ素子の形成によるチップ面積の増大を抑制できる高速なインタフェースを有する不揮発性半導体記憶装置を提供する。

【解決手段】信号を送受信するインダクタ素子ID1を有するNANDチップNC1と、信号を送受信するインダクタ素子ID0を有するNANDチップNC0と、NANDチップNC1,NC0の動作を制御する制御回路が形成され、インダクタ素子ID1,ID0との間で信号を送受信するインダクタ素子IDCを有する制御用チップCC0とを備える。インダクタ素子ID1,ID0の外周は、インダクタ素子IDCの外周をインダクタ素子IDCを含む平面に垂直な方向に延長した閉空間に含まれ、インダクタ素子IDCのインダクタンスは、インダクタ素子ID1あるいはID0のインダクタンスの少なくともいずれか一方より大きい。

(もっと読む)

半導体記憶装置

【課題】占有面積が小さく、高い信頼性を有する半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、ロウ方向、カラム方向及び積層方向に配列された複数のメモリトランジスタMTr1〜8と、メモリトランジスタMTr1〜8に信号を供給するワード線WL1〜WL8と、それらを埋める層間絶縁層10とを備えたメモリセルアレイ層100と、メモリセルアレイ層100の上面の側に形成される半導体基板200と、半導体基板200に形成されメモリセルアレイ層100に対し所定の電圧を供給する周辺回路層300と、周辺回路層300とメモリセルアレイ層100とを電気的に接続する接続層400とを備える。メモリセルアレイ層100は、半導体基板200とは別の半導体基板500上に形成されたものである

(もっと読む)

昇圧回路及び半導体装置

【課題】半導体チップのチップ面積を小さくできる昇圧回路を提供する。

【解決手段】昇圧回路100は、N個(Nは2以上の自然数)の容量素子(容量素子C0〜C3)を備える。N個の容量素子のうち第K番目(1<K<N、Kは自然数)の容量素子(容量素子C2)は第(K−1)番目の容量素子(容量素子C1)によって昇圧された第(K−1)番目の昇圧電圧を受けて、第(K−1)番目の昇圧電圧を更に昇圧した第K番目の昇圧電圧を発生して第(K+1)番目の容量素子(容量素子C3)に供給し、第N番目の容量素子の一端(出力端子OUT)から第N番目の昇圧電圧を発生する。N個の容量素子の内、少なくとも1つの容量素子(容量素子C0及びC1)は他の容量素子(容量素子C2及びC3)が形成された第1のチップ(半導体チップCHIP2)とは異なる第2のチップ(半導体チップCHIP1)に形成され、第1及び第2のチップは互いに積層されている。

(もっと読む)

情報処理方法、積層型集積回路メモリ

【課題】メモリの単位メガバイト当たり製造コストを、単にモノリシック回路集積法で慣用的に製造される回路の数分の一に低減させる。

【解決手段】各層が別々に最適化されるように、別々の層(103)上へのメモリ回路(103)および制御論理回路(101)の物理的分離が可能な三次元(3DS)メモリ(100)。幾つかのメモリ回路(103)について1つの制御論理回路(101)で十分であり、コストを低減できる。3DSメモリ(100)の製造は、メモリ回路(103)を50μm以下の厚さに薄肉化する工程と、該メモリ回路を、ウェーハ基板形態のまま回路積層体に接合する工程とを有する。微粒子の高密度層間垂直バス相互接続部(105)が使用されている。3DSメモリ(100)製造方法は、幾つかの性能および物理的サイズ効率を可能にしかつ確立された半導体加工技術により実施される。

(もっと読む)

プロセス均一性及び熱消散を改善するダミーTSV(スルーシリコンビア)

【解決手段】

各々が能動回路領域を含むチップの積層体において、多重チップ積層体内の複数のスルーシリコンビア(TSV)開口をパターニングし、エッチングし、そして熱的伝導性材料で充填することによって、多重チップ積層体からの熱を熱的に伝導させるための複数のTSV構造が形成され、複数のTSV開口は、いずれの能動回路領域をも貫通せずに多重チップ積層体の実質的に全体を通って延びる第1の大きなTSV開口と、能動回路領域まで下に延びるが通過はしない第2の小さい開口と、を含む。

(もっと読む)

61 - 80 / 222

[ Back to top ]