Fターム[5F083ZA23]の内容

Fターム[5F083ZA23]の下位に属するFターム

窓/開口を有するもの (5)

リードフレーム (23)

Fターム[5F083ZA23]に分類される特許

161 - 180 / 222

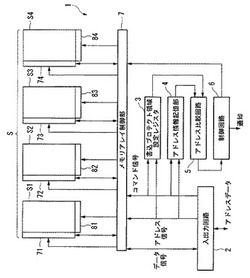

不揮発性RAM

【課題】アプリケーションに頻繁にアクセスされるワーク領域と、プログラムコードを記憶させる領域とを、従来に比較して小型なチップサイズにて、1チップで構成することができる不揮発性RAMを提供する。

【解決手段】本発明の不揮発性RAMは、ランダムにデータの読み書きを行う不揮発性メモリであり、電源を切っても記憶内容が失われない不揮発性モード、及び電源を切ると記憶内容が失われる揮発性モードのデータ保持状態に、データ保持の状態を制御可能なメモリ素子からなるメモリ領域と、該メモリ領域において、不揮発性モード書込及び揮発性モード書込各々の対象となるアドレス範囲の領域が設定されるアドレス設定レジスタと、該アドレス設定レジスタを参照して、それぞれのアドレス範囲に対応したデータの書き込みを行うメモリ制御回路とを有する。

(もっと読む)

多層基板の間の相互接続構造及びその製造方法

【課題】多層基板の間の相互接続構造及びその製造方法を提供する。

【解決手段】多層基板の間の相互接続構造は、第1の多層基板(300)と第2の多層基板(400)を含む。第1の多層基板は複数の第1の金属層(11、14、17)、複数の第1の誘電層(10、13、16)及び複数のビアホール(1、2、3)を有する。一つの第1の金属層の端縁は、それに対応する第1の誘電層の端縁と互いに接続され、それと隣接する他の第1の金属層の端縁と他の第1の誘電層の端縁から分離される。第2の多層基板は複数の第2の金属層(21、24、27)及び複数の第2の誘電層(20、23、26)を有する。一つの第2の金属層の端縁は、それに対応する第2の誘電層の端縁と互いに接続され、それと隣接する他の第2の金属層の端縁と他の第2の誘電層の端縁から分離される。ビアホールは第1の誘電層の端縁に設けられ、導電部を有する。第1の金属層に対応する導電部と第2の金属層は互いに接着される。

(もっと読む)

積層メモリ

【課題】 積層メモリの貫通電極は同一配置位置であり、各層は並列接続となる。そのため各層を個別にアクセスするために複数の貫通電極が必要になるという問題がある。

【解決手段】 本発明の積層メモリは、各層の階層認識情報を設定するID用貫通電極の配置位置を異ならせた第1及び第2のメモリチップを交互に積層する。このように交互に積層することで、各層の階層認識情報用の内部回路はカスケード接続となる。内部回路は各層の階層認識情報を簡単に生成することができる。これらの階層認識情報を識別することで各層の動作又は非動作が選択できる積層メモリが得られる。

(もっと読む)

記憶素子及びその作製方法、半導体装置

【課題】歩留まりが高く、簡便かつ安価に記憶素子を提供する。

【解決手段】記憶素子を少なくとも第1の導電層110と、第2の導電層112と、第1の導電層110と第2の導電層に挟持されたメモリ層111とを有する構成とする。メモリ層111は、有機薄膜で被覆された導電性材料よりなるナノ粒子から構成されており、液滴吐出法を用いて形成する。有機薄膜で被覆された導電性材料よりなるナノ粒子が溶媒に分散された組成物を液滴として吐出(噴出)し、乾燥することで該溶媒を気化させ、メモリ層を形成する。よって、簡便に記憶素子を形成することができる。また、材料の利用効率、さらには歩留まりも上がるため安価に記憶素子を提供することが可能となる。

(もっと読む)

情報処理方法

【課題】メモリの単位メガバイト当たり製造コストを、単にモノリシック回路集積法で慣用的に製造される回路の数分の一に低減させる

【解決手段】各層が別々に最適化されるように、別々の層(103)上へのメモリ回路(103)および制御論理回路(101)の物理的分離が可能な三次元(3DS)メモリ(100)。幾つかのメモリ回路(103)について1つの制御論理回路(101)で十分であり、コストを低減できる。3DSメモリ(100)の製造は、メモリ回路(103)を50μm以下の厚さに薄肉化する工程と、該メモリ回路を、ウェーハ基板形態のまま回路積層体に接合する工程とを有する。微粒子の高密度層間垂直バス相互接続部(105)が使用されている。3DSメモリ(100)製造方法は、幾つかの性能および物理的サイズ効率を可能にしかつ確立された半導体加工技術により実施される。

(もっと読む)

記憶装置及び半導体装置並びにそれらの作製方法

【課題】有機化合物を含む層を有する素子が設けられたフレキシブルな記憶装置及び半導体装置を歩留まり高く作製する。また、信頼性の高いフレキシブルな記憶装置及び半導体装置を歩留まり高く作製する。

【解決手段】剥離層を有する基板上に素子層及び素子層を封止する絶縁層を有する積層体を形成し、剥離層から積層体を剥離してフレキシブルな記憶装置及び半導体装置を作製する方法であって、素子層において第1の電極層及び第2の電極層からなる一対の電極間に有機化合物を含む層を有する記憶素子を含み、少なくとも一方の電極層はスズを含む合金層で形成する。また、第1の電極層及び第2の電極層からなる一対の電極間に有機化合物を含む層を有する記憶素子を含み、少なくとも一方の電極層はスズを含む合金層で形成されるフレキシブルな記憶装置及び半導体装置である。

(もっと読む)

半導体装置

【課題】高速DRAMなどにおいてボンディングパッドと共に評価パッドも増加する状況の下、余計なチップ面積の増大を最小限に抑える。

【解決手段】ウェハ上の1チップ分のDRAMでは、チップ上の中央部に、アドレスピン、データピン、電源ピン、グラウンドピンなどの様々な機能を持つ複数のパッド(No.1~103)が一列に配置されている。これらのパッド(No.1~103)のうち、パッケージ組み立て時にはボンディングはするが評価用パッケージ段階やプローブテスト時では使用しないパッド3の横に、パッケージ組み立て時にボンディングは実施されない電源モニタ用評価パッド4が近接して配置されている。

(もっと読む)

メモリモジュール

【課題】制御チップの裏面側に搭載されたメモリチップにて生じる信号の反射の影響を低減する。

【解決手段】モジュール基板10を介してメモリバッファMBと対向する位置に配置されたメモリチップMC1と、モジュール基板10を介してメモリバッファMBと対向しない位置に配置されたメモリチップMC3と、モジュール基板10を介してメモリチップMC3と対向する位置に配置されたメモリチップMC11とを備え、メモリチップMC1に接続される配線部分A101とメモリチップMC3,11に接続される配線部分A103とが分岐する分岐点B100が、メモリバッファMBの平面的な搭載位置とメモリチップMC3,11の平面的な搭載位置との中間線Cから見てメモリバッファMB側に位置している。これにより、配線部分A101の配線長を十分に短くすることができる。

(もっと読む)

電気ヒューズ及びその作成方法

【課題】 低プログラミング電力で切断可能な半導体ヒューズ及びその作成方法を提供する。

【解決手段】 半導体ヒューズは、ヒューズ要素と、ヒューズ要素のエレクトロマイグレーション耐性を低減する圧縮応力ライナとを含む。方法は、基板内にトレンチ構造部を形成するステップと、トレンチ構造部内にヒューズ材料を堆積させるステップと、ヒューズ材料の上に圧縮応力ライナ材料を堆積させるステップと、圧縮応力ライナ材料をパターン付けするステップとを含む。

(もっと読む)

シリコン・オン・インシュレータ基板上に形成された薄膜相変化メモリ・セル、その形成方法、および1つ以上のメモリ・セルを含む集積回路

【課題】メモリ・セルは、半導体フィーチャおよび相変化材料を含む。

【解決手段】半導体フィーチャは、半導体フィーチャを第1の電極および第2の電極に分割する溝を画成する。相変化材料は、少なくとも部分的にこの溝を満たし、第1および第2の電極を電気的に結合するように働く。相変化材料の少なくとも一部は、第1および第2の電極のうちの少なくとも1つに対して加えられるスイッチング信号に呼応して、低電気抵抗状態と高電気抵抗状態を切り換えるように作動する。

(もっと読む)

半導体集積回路装置および不揮発性メモリ装置

【課題】 不揮発性メモリ装置にデータを電気的に書き込むときに、半導体集積回路基板には高電圧が印加されないようにする。

【解決手段】 1つの配線基板(51)上に、第1の電圧で電気的にデータを書込み可能な不揮発性メモリ装置(15B)と、第1の電圧よりも低い第2の電圧で動作する半導体集積回路基板(10E)とが搭載された半導体集積回路装置(20E)において、不揮発性メモリ装置は、第1の電圧が供給される第1の端子(15−3)と第2の電圧を出力する第2の端子(15−4)とを持ち、半導体集積回路基板(10E)は、第2の端子と電気的に接続された第3の端子(RES#)を持つ。不揮発性メモリ装置(15B)は、第1の端子と第2の端子との間に設けられて、第1の電圧を第2の電圧に変換する電圧変換回路を有する。不揮発性メモリ装置(15B)は、半導体集積回路基板(10E)上に積層されている。

(もっと読む)

半導体集積回路装置

【課題】 パッケージの端子数の増加と、ベースチップのI/O領域の増加を抑制すること。

【解決手段】 マスクROM領域と内部バス(13)とを有する半導体集積回路基板(10)と、この半導体集積回路基板上に積層され、複数のROM接続端子(15−1,15−2)を持つプログラマブルROM(15)とを備えた半導体集積回路装置(20)において、内部バスに接続された複数のバス接続端子(132−1,134−1)と複数のROM接続端子とがそれぞれ電気的に接続されている。複数のバス接続端子は、半導体集積回路基板の外周に設けられて良いし、マスクROM領域上に設けられても良いし、内部バス上に設けられても良い。この場合、複数のROM接続端子と複数のバス接続端子とはワイヤボンディングによって電気的に接続される。

(もっと読む)

情報処理方法

【課題】メモリの単位メガバイト当たり製造コストを、単にモノリシック回路集積法で慣用的に製造される回路の数分の一に低減させる

【解決手段】各層が別々に最適化されるように、別々の層(103)上へのメモリ回路(103)および制御論理回路(101)の物理的分離が可能な三次元(3DS)メモリ(100)。幾つかのメモリ回路(103)について1つの制御論理回路(101)で充分であり、コストを低減できる。3DSメモリ(100)の製造は、メモリ回路(103)を50μm以下の厚さに薄肉化する工程と、該メモリ回路を、ウェーハ基板形態のまま回路積層体に接合する工程とを有する。微粒子の高密度層間垂直バス相互接続部(105)が使用されている。3DSメモリ(100)製造方法は、幾つかの性能および物理的サイズ効率を可能にしかつ確立された半導体加工技術により実施される。

(もっと読む)

半導体記憶装置

【課題】複数の半導体記憶装置を混載した場合であってもより効率的なデータ転送が可能な半導体記憶装置を提供すること。

【解決手段】本発明の半導体記憶装置は、基板と、基板上に形成される揮発性の第一の半導体記憶装置及び不揮発性の第二の半導体記憶装置とを有する半導体装置であって、第一の半導体記憶装置及び第二の半導体記憶装置のそれぞれは、チップイネーブル信号を入力するための第一のパッド、書き込みイネーブル信号を入力するための第二のパッド、出力イネーブル信号を入力するための第三のパッド、アドレス信号を入力するための第四のパッド、データを入力するための第五のパッドを有し、かつ、第一の半導体記憶装置は、第二の半導体記憶装置における第一のパッドに電気的に接続される第六のパッドを、第二の半導体記憶装置は、第一の半導体記憶装置における前記第一のパッドに電気的に接続される第七のパッドを、有している。

(もっと読む)

半導体メモリ装置

【課題】低コストで大容量の半導体メモリ装置を実現する。

【解決手段】メモリカードは、メモリチップ100と、複数のメモリチップ200と、これらメモリチップを制御するメモリコントローラとから構成される。メモリチップ100は、メモリセルアレイ3、デコーダ4及びセンスアンプ5から構成されるNANDフラッシュメモリと、周辺回路6と、チャージポンプ部7と、ボンディングパッド領域2−1及び2−2から構成される。ボンディングパッド領域2−1にはチャージポンプ部7の出力電圧を外部に出力する端子パッド22が設けられ、メモリチップ200はメモリチップ100からの出力電圧を入力して動作する。メモリチップ200は電源回路を備える必要が無いため面積を削減することが可能である。このため、メモリカードの実装密度が向上し、低価格が実現できる。

(もっと読む)

メモリモジュール

【課題】高速且つ低コストで、メモリ容量の拡張性を確保できる使い勝手の良い情報システム装置を提供する。

【解決手段】情報処理装置、揮発性メモリおよび不揮発性メモリを含む情報処理システムを構成する。情報処理装置、揮発性メモリおよび不揮発性メモリは直列接続させ、接続信号数を少なくすることにより、メモリ容量の拡張性を保ちつつ、高速化を図る。不揮発性メモリのデータを揮発性メモリへ転送させる際は、エラー訂正を行い、信頼性の向上を図る。これら複数のチップからなる情報処理システムを、各チップが相互に積層して配置され、ボールグリッドアレイ(BGA)やチップ間のボンディングによって配線された情報処理システム・モジュールとして構成する。

(もっと読む)

ダイナミックランダムアクセスメモリおよび半導体記憶装置

【課題】アスペクト比が1:2のパッケージに高い有効比率で収容できる22N+1ビットの半導体記憶装置を提供する。

【解決手段】アスペクト比が1:2の半導体基板2の主表面を3行3列の9個の領域に等分割し、中央領域以外の各領域にアスペクト比が1:2で22N−2ビットのサブアレイ部3を配置する。中央領域には制御回路4およびパッド5群を設ける。アスペクト比が1:2のメモリチップを形成することができ、従来と同様のアスペクト比が1:2のパッケージに高い有効比率で収容できる。

(もっと読む)

不揮発性半導体記憶装置

【課題】 電気的にデータの書き換えが可能な不揮発性の複数のメモリセルを有する複数のメモリセルアレイが配置された不揮発半導体記憶装置のチップ上において、特にチップ端にパッドを配置することを前提とした場合に、データ伝送遅延を最小限度にし、スキューを最小化すると共に、高集積化を実現する。

【解決手段】 データ線の配線方法について、パッドから近い位置に配置されるページバッファブロック内に、パッドから遠い位置に配置されるページバッファブロックから出力されるデータ線を配線する。

(もっと読む)

不揮発性記憶装置

【課題】信頼性や信号伝達性能を確保しつつ、小型化や量産性を向上させた不揮発性記憶装置を提供する。

【解決手段】搭載基板上にパッドが形成されない第1辺及びパッドが形成された第2辺とを有する不揮発性メモリチップを搭載する。上記不揮発性メモリチップ上に、上記不揮発性メモリチップを制御するコントロールチップを搭載する。上記コントロールチップは、上記不揮発性メモリチップのパッドに対応した第1パッド列を有し、上記第1パッド列が上記不揮発性メモリチップの上記第1辺に近接するように搭載する。上記コントロールチップの第1パッド列と上記搭載基板上に形成された第1電極列とを第1ワイヤ群を介して接続する。上記不揮発性メモリチップのパッドと、上記搭載基板上に形成された第2電極列とを第2ワイヤ群を介して接続する。上記第1電極列と上記第2電極列とを上記搭載基板に形成された配線を介して接続する。

(もっと読む)

半導体装置およびその作製方法

【課題】コントロールゲート電極を形成する際の位置ずれの問題を起こさず自己整合的に形成し、さらにコントロールゲート電極とフローティングゲート電極間でリークを発生させない半導体装置及びその作製方法を提供する。

【解決手段】半導体膜と、前記半導体膜上の第1のゲート絶縁膜と、前記第1のゲート絶縁膜上のフローティングゲート電極と、前記フローティングゲート電極を覆った第2のゲート絶縁膜と、前記第2のゲート絶縁膜上のコントロールゲート電極と、を有し、前記コントロールゲート電極は、前記第2のゲート絶縁膜を介して前記フローティングゲート電極を覆うように形成され、前記コントロールゲート電極にはサイドウォールが形成され、前記サイドウォールは前記フローティングゲート電極によって生じた前記コントロールゲート電極の段差部分に形成されている。

(もっと読む)

161 - 180 / 222

[ Back to top ]