Fターム[5F083ZA23]の内容

Fターム[5F083ZA23]の下位に属するFターム

窓/開口を有するもの (5)

リードフレーム (23)

Fターム[5F083ZA23]に分類される特許

121 - 140 / 222

半導体集積回路装置およびその製造方法

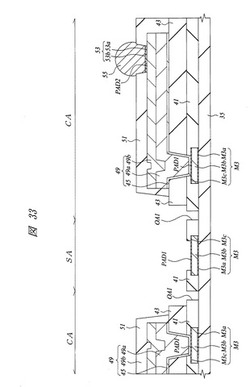

【課題】TEG上のパッド部の浸食を防止し、また、実デバイスのパッド部の半田のぬれ性や半田形成後のシェア強度の向上を図る。

【解決手段】半導体ウエハのチップ領域CAの第3層配線M3およびスクライブ領域SAの第3層配線M3を、それぞれ、TiN膜M3a、Al合金膜M3bおよびTiN膜M3cで構成し、チップ領域CAの再配線49上の第2パッド部PAD2を洗浄し、もしくはその上部に無電界メッキ法でAu膜53aを形成する。さらに、Au膜53a形成後、リテンション検査を行い、その後、さらに、Au膜53bを形成した後、半田バンプ電極55を形成する。その結果、TiN膜M3cによってTEGであるスクライブ領域SAの第3層配線M3の第1パッド部PAD1のメッキ液等による浸食を防止でき、また、Au膜53a、53bによって第2パッド部PAD2の半田のぬれ性や半田形成後のシェア強度の向上を図ることができる。

(もっと読む)

半導体装置

【課題】基板上に複数のメモリチップとコントローラチップを搭載した半導体装置において、チップ間の配線を短縮するチップレイアウトを実現して性能向上を実現することができる半導体装置を提供する。

【解決手段】本発明の実施の形態に係る半導体装置は、半導体基板と、一方の表面上の中央部に複数のパッドが形成され、前記半導体基板上に搭載されたメモリチップと、前記メモリチップの外形サイズより外形サイズが小さく、一方の表面上の周辺部に複数のパッドが形成され、前記メモリチップの一方の表面上の中央部を除く一部分に搭載されたコントローラチップと、前記メモリチップの一方の表面上の中央部に形成された複数のパッドと前記コントローラチップの一方の表面上の周辺部に形成された複数のパッドとを電気的に接続する複数の金属ワイヤと、を備える。

(もっと読む)

半導体記憶装置

【課題】複数の半導体メモリチップと半導体キャッシュメモリチップとを具える半導体記憶装置において、その小型化を図るとともに、動作速度及び放熱特性を向上させる。

【解決手段】配線基板の第1の主面上に、複数の半導体メモリチップを積層するとともに、前記複数の半導体メモリチップ上にインターポーザチップを積層し、さらに前記インターポーザチップ上に半導体コントローラチップを積層する。前記複数の半導体メモリチップは、それぞれ前記配線基板の内部接続用端子と配線を介して互いに独立に電気的に接続されてなり、前記インタポーザチップを介して前記配線基板の他の内部接続用端子と電気的に接続されてなる前記半導体コントローラチップによって、互いに独立に制御される。

(もっと読む)

半導体装置、半導体システム

【課題】動作速度が従来よりも高速な半導体装置を提供する。

【解決手段】各々に同じ信号が入力される第1電極パッド21及び第2電極パッド22と、第1電極パッド21及び第2電極パッド22の両方から信号が入力されるメモリ回路23と、を備える半導体装置である。メモリ回路23は、第1電極パッド21から入力される信号と、第2電極パッド22から入力される信号と、のいずれか早く入力される信号により動作する。

(もっと読む)

半導体素子の形成方法及びメモリシステムの製造方法

【課題】半導体素子の形成方法、及びメモリシステムの製造方法を提供する。

【解決手段】基板400上にパターン形成対象層430を形成し、パターン形成対象層430上に、マスク層432を形成する。半導体素子の第1領域でマスク層432の一部を除去し、マスク層432を半導体素子の第2領域に残留させる。第1領域ではパターン形成対象層430上に、第2領域ではマスク層432上にモールドマスクパターン450を形成する。第1領域及び第2領域で、モールドマスクパターン450上にスペーサ層460を形成する。モールドマスクパターン450のパターン構造物の側壁に複数のスペーサが残留するようにスペーサ層460をエッチングし、第2領域でマスク層432をエッチングする。

(もっと読む)

半導体装置及びその製造方法

【課題】リテンションタイム(情報保持時間)を大きくすることで、リフレッシュサイクルを長くでき、消費電力を大幅に低減できるキャパシタレスRAMを提供する。

【解決手段】キャパシタレスRAMを含む半導体装置は、フローテイングボデイ構造を有する電界効果トランジスタ(FET)を含み、FETは所定のバンドギャップを有する第1の半導体(p−SiGe)からなる領域に設けられたチャネルボデイ部3と、第1の半導体よりもバンドギャップの大きい第2の半導体(n−Si)からなる領域10−2を有する。この特徴により電荷(ホール)をボデイ領域3に蓄える際、ボデイ領域3にあるホールから見たソース・ドレイン領域10のエネルギー障壁が大きいので、蓄えられるホール(正電荷)数を多くすることができる。

(もっと読む)

集積回路装置及びその端子配置方法

【課題】複数の機種に展開される集積回路装置の低コスト化を実現する集積回路装置及びその端子配置方法を提供する。

【解決手段】マスクROMを内蔵する集積回路装置は、EPROMを内蔵する集積回路装置の第1の辺に沿って配置される外部端子群と共通の第1の共通外部端子群と、前記EPROMにアクセスするEPROM版処理回路の機能の少なくとも一部を有し、その処理内容に対応した信号が前記第1の共通外部端子群を介して入力又は出力される処理回路と、前記処理回路によってアクセスされる前記マスクROMとを含み、前記第1の共通外部端子群が、当該集積回路装置の周囲の4辺のうち前記第1の辺に対応する第2の辺に沿って配置され、前記外部端子群を構成する各外部端子の並び順序と、前記第1の共通外部端子群を構成する各共通外部端子の並び順序とが同じである。

(もっと読む)

メモリチップ及び半導体装置

【課題】ロジックチップとメモリチップとをインタポーザを介して積層した半導体装置におけるインタポーザ上での接続配線構造の複雑化を緩和できるメモリチップの提供。

【解決手段】ロジックチップとメモリチップ500とをインタポーザを介して積層した構造の半導体装置であって、前記ロジックチップは、その中央部に前記メモリチップ500と電気的に接続される信号及びデータ用内部端子を有し、前記メモリチップ500は、中央部に配置された信号及びデータ用内部端子と、前記内部端子を取り囲むようにその周囲に配置され前記内部端子と電気的に接続されたメモリアレイを含み、前記ロジックチップの内部端子が前記メモリチップの内部端子に前記インタポーザのスルーホール(貫通電極)を介して接続されている。

(もっと読む)

情報処理装置および半導体記憶装置

【課題】マルチコア構成のシステムLSIの処理性能を高める。

【解決手段】1チップ内に複数のCPUコアを有するシステムLSIまたはマイクロプロセッサと、それに積層されたDRAMにより情報処理装置を構成する。システムLSIチップ内部はチップ多分割I/O分散アーキテクチャをとる。システムLSI内に独立動作可能な複数のCPUコアを有し、それぞれのCPUコアに3Dインターフェース回路を設け、独立にデータ送受信を行うことを可能とする。DRAMチップ内部もチップ多分割I/O分散アーキテクチャをとる。DRAMを独立動作可能な複数のDRAMコアに分割し、それぞれのDRAMコアに3Dインターフェース回路を設け、独立にデータ送受信を行うことを可能とする。

(もっと読む)

記憶回路スタックの製造方法と記憶回路のアドレス方法、及び対応するスタックと装置

本発明は複数の記憶回路から成るスタックの製造方法(10)に関し、少なくとも2つの記憶回路の有効性をテストする段階(14)を含む。この方法は、各記憶回路を構成する段階(18)を含み、この段階では、スタック内の各記憶回路の構成装置に、スタック内の記憶回路に割り当てられた識別子に関する情報と、記憶回路の有効性テストの結果に関する情報とを書き込む(110)。本発明はまた、記憶回路をアドレスする方法と、記憶回路スタック、及びスタックを含む電子装置に関する。 (もっと読む)

半導体記憶装置

【課題】積層して搭載する複数の半導体記憶素子のサイズの拡大や積層数の増大を可能にする半導体記憶装置を提供する。

【解決手段】本発明の実施の形態に係る半導体記憶装置は、素子搭載部と、外形の一辺に沿って配列された接続パッドとを備える配線基板と、外形の一辺に沿って配列された電極パッドを有する複数の半導体記憶素子を備え、複数の半導体記憶素子は配線基板の素子搭載部上にパッド配列辺を同方向に向けるように積層された半導体記憶素子群と、半導体記憶素子群上に積層され、少なくとも外形の一辺に沿って配列された電極パッドを有するコントローラ素子と、を具備し、複数の半導体記憶素子の電極パッドとコントローラ素子の電極パッドは、配線基板の接続パッドの配列位置に合わせて平行に配置する。

(もっと読む)

ICパッケージおよび通信機器

【課題】不揮発性メモリ等の書き込み状態を外観だけで認識できるICパッケージおよび通信機器を提供する。

【解決手段】ICパッケージ10に、データの書き換えが可能な記憶部11と、記憶部11の状態を検出する検出部12と、検出部12の検出結果に応じた報知を行う表示部14とを設ける。

(もっと読む)

半導体素子のリセスゲート及びその製造方法

【課題】リセスゲート及びこれを含む半導体素子の製造方法を提供する。

【解決手段】半導体素子のリセスゲートは、基板110と、金属層165と、ポリシリコン層と、ポリシリコン層に隣接し、金属層165から離隔され、形成されたソース領域及びドレーン領域と、を含む。半導体素子の形成方法は、基板110の上にソース/ドレーン120層を形成する段階と、リセス112を形成し、第1導電層パターン145を形成する段階と、第1導電層パターン145上に第2導電層を形成する段階、ソース/ドレーン層120と重畳されるように第2導電層パターン156を形成する段階と、前記第2導電層パターン156と、前記ソース/ドレーン層120上に絶縁層を蒸着する段階と、第2導電層パターン156上にキャップを形成するように絶縁層を平坦化する段階と、を含む。

(もっと読む)

データ記憶装置及び積層可能構成

第1のメモリデバイス及び第2のメモリデバイスは同一の入力/出力レイアウト配置を有する。スタックを形成するように第2のメモリデバイスは第1のメモリデバイスに固定される。接続を容易にするため、第2のメモリデバイスは、第1のメモリデバイスの出力を第2のメモリデバイスの対応する入力と位置整合させるよう、スタック内の第1のメモリデバイスに対して回転オフセットされる。第1のメモリデバイスに対する第2のメモリデバイスの回転オフセットは、第1のメモリデバイスの1つ以上の出力を、第2のメモリデバイスの1つ以上のそれぞれの入力と位置整合させる。スタック内の第1のメモリデバイスから別のメモリデバイスへの出力群と入力群との間のリンク群に基づいて、メモリデバイスのスタックは、これらのメモリデバイスを通る1つ以上の直列接続構成を担う経路群を含むことができる。  (もっと読む)

(もっと読む)

選択的プリチャージを使用したメモリ読取り安定性の改善

メモリデバイスは、ビットセル(34)にアクセスする前にビット線電圧を低減するために、選択的プリチャージおよび電荷共有を利用する。ビット線電圧の低減は、ビット線の異なるセクション(31、33)を異なる電圧(たとえば、供給電圧および接地)にプリチャージし、これらのセクション間で電荷共有を使用することによって達成される。読取り安定性は、ビット線電圧の低減の結果として改善される。ビット線セクション間の相対容量差(B2−C2)により、電荷共有後のビット線電圧を決定する。したがって、メモリデバイスはプロセス変動または温度変動に耐性がある。ビット線電圧は、供給電圧または接地にプリチャージされるセクションを選択することによって、設計において制御できる。  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】基準電流の立ち上がりの高速化を図ることが可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、しきい値電圧に応じたデータを保持するメモリセルにデータを記憶し、読み出すことが可能な半導体記憶装置であって、基準電流生成部と、基準電流生成部の出力に応じて出力端子から配線に基準電流を出力するアンプ部と、を有する基準電流生成回路を備える。

(もっと読む)

半導体記憶装置

【課題】本発明は、抵抗変化型メモリ素子をセルに用いたマルチチップパッケージにおいて、高抵抗素子を利用することにより、工程数の増加を必要とすることなく、積層された複数のメモリチップを識別できるようにする。

【解決手段】たとえば、同一パッケージ内に積層された複数のメモリチップは、それぞれ、チップアドレス識別回路150を備える。各チップは、相互に接続される第1のメモリ位置検知用パッドのテストパッドTT,TB間に、それぞれ、メモリセルと共通のプロセスにより同時に形成される可変抵抗素子CCを有する。チップアドレス識別回路150は、各チップの可変抵抗素子CCを高抵抗化することにより、チップの積層順に応じて、テストパッドTTにそれぞれ現れる電圧を、比較器154にて、メモリ位置検知回路156からの既知の比較信号と比較することで、各層のメモリチップの位置を検知する。

(もっと読む)

半導体装置の製造方法

【課題】ヒューズ配線部の開口工程において、ヒューズ配線にダメージを与えて誤切断してしまうことを防ぐ。

【解決手段】ヒューズ配線6上の開口部17下にて、SiCN膜からなる保護膜11とプラズマCVD法によって成膜された窒化シリコン膜または酸化シリコン膜からなる保護膜18とが積層された構造を形成することにより、ヒューズ配線6上のシード膜23およびバリア導電膜22をウエットエッチングする際の洗浄液のヒューズ配線6への浸入を保護膜18にて防ぐ。

(もっと読む)

非線形導体メモリ

高速で低電力のメモリ素子は、非線形導体のアレイを備え、格納、アドレスデコーディング、および出力検出はすべて、ダイオードまたは他の非線形導体によって達成される。様々な実施形態において、行抵抗器および列抵抗器は、選択されていない行または列に接続されているときの高抵抗と、選択された行および列に接続されたときの低抵抗との間で切り替え可能である。電子メモリ素子は、情報回路と、複数の行スイッチと、複数の列スイッチと、選択回路とを含む。  (もっと読む)

(もっと読む)

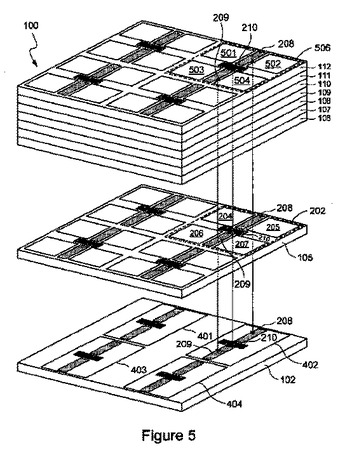

3次元メモリモジュールアーキテクチャ

本発明の様々な実施形態は、スタックされたメモリモジュールに向けられている。本発明の一実施形態において、メモリモジュール(100,600,1200,1400)は、少なくとも1つのメモリ層がスタックされた少なくとも1つのメモリコントローラ層(102,602,1204,1402)を備える。ファインピッチのスルー複数バイア(例えば、スルーシリコン複数バイア)(114,116)が、前記少なくとも1つのメモリコントローラ(401〜404)と、前記少なくとも1つのメモリ層との間の電気的な伝達を提供する前記スタックを通じて、前記少なくとも1つのメモリコントローラの表面に対してほぼ垂直に延在する。追加的には、前記メモリコントローラ層は、前記メモリモジュールに対して双方向にデータを伝達するよう構成された少なくとも1つの外部インターフェースを含む。更にまた、前記メモリモジュールには、光学層(602,1202)を含めることができる。該光学層を、前記スタック内に含めることができ、及び、該光学層は、前記少なくとも1つのメモリコントローラに対して双方向にデータを伝達するバス導波路を有する。前記外部インターフェースは、前記光学層とインターフェースする光学的な外部インターフェースとすることができる。  (もっと読む)

(もっと読む)

121 - 140 / 222

[ Back to top ]