Fターム[5F083ZA23]の内容

Fターム[5F083ZA23]の下位に属するFターム

窓/開口を有するもの (5)

リードフレーム (23)

Fターム[5F083ZA23]に分類される特許

81 - 100 / 222

スイッチング素子

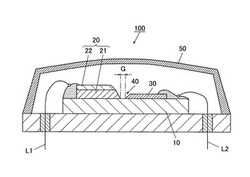

【課題】より単純な構造で構成されるとともに、安定的にスイッチング動作を行うことができる3端子のスイッチング素子を提供する。

【解決手段】絶縁性基板10と、絶縁性基板に設けられた第1電極20及び第2電極30と、第1電極と第2電極との間に設けられ、第1電極と第2電極との間への所定電圧の印加により抵抗のスイッチング現象が生じるナノメートルオーダーの間隙を有する電極間間隙部40と、電極間間隙部に気体の酸素が満たされた状態で少なくとも電極間間隙部を密封する封止部材50とによりスイッチング素子100を構成する。

(もっと読む)

半導体装置

【課題】単一の半導体メモリチップを互いに異なるピン配列を備えたパッケージに実装する場合に、半導体メモリチップのパッド数の増加を防止する。

【解決手段】製品指定情報が、ボンディンク回路、ヒューズ回路等の製品指定情報回路228から与えられる。デコーダ回路224は、この製品指定情報をデコードして、該デコード結果に応じて複数の信号回路220の1つを選択的にチップ・パッド210に接続する。

(もっと読む)

半導体メモリ装置及びそれを含む半導体パッケージ

【課題】高性能及び低電力が要求される多様な装置及びシステムを支援できる、マルチチャネルインタフェース方式のワイド入出力を有する半導体メモリ装置及びそれを含む半導体パッケージを提供する。

【解決手段】本発明の一実施形態に係る半導体メモリ装置は、複数のメモリセルアレイを含む半導体ダイからなり、半導体ダイの中央部に形成される入出力バンプパッド部を含む。入出力バンプパッド部は、前記それぞれのメモリセルアレイを外部装置と独立的に接続するための複数のチャネルを提供する。マルチチャネル方式のワイド入出力インタフェースを通じて動作周波数の減少及びバンド幅の拡張を図ることによって、高性能の装置及びシステムを支援すると同時に電力消耗を減少させる。

(もっと読む)

半導体セル構造物、上記半導体セル構造物を含む半導体装置、及び上記半導体装置を含む半導体モジュール

【課題】所定の整列関係を有する単位セルを含む半導体セル構造物を提供すること。

【解決手段】単位セルは、活性領域14、18、24、28、ゲートパターン32、34、36、38、ダミーパターン42、44、46、48、及び導電パターン94を有する。ゲートパターン32、34、36、38は活性領域14、18、24、28と交差する。ダミーパターン42、44、46、48は単位セルを電気的に接続する。選択された単位セル内のダミーパターン42、44、46、48は、選択された単位セル内のゲートパターン32、34、36、38との間に対角的に配置される。導電パターン94はダミーパターン42、44、46、48と電気的に接続する。これにより、半導体セル構造物は、行及び列に沿って互い突出しない単位セルを有することができる。上述した半導体セル構造物は半導体装置及び半導体モジュールに配置される。

(もっと読む)

抵抗変化物質を含む半導体素子及びその動作方法

【課題】抵抗変化物質を含む半導体素子及びその動作方法を提供する。

【解決手段】印加された電圧によって抵抗が変化する抵抗変化物質をチャネル層として使用する半導体素子である。

(もっと読む)

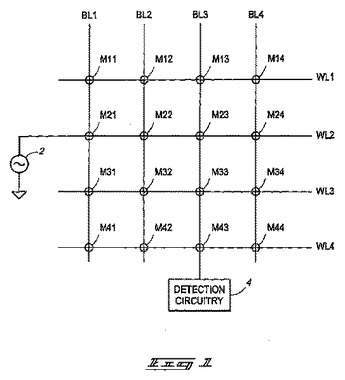

クロスポイントメモリセル、不揮発性メモリアレイ、メモリセルの読み出し方法、メモリセルのプログラミング方法、メモリセルへの書き込み方法およびメモリセルからの読み出し方法、ならびにコンピュータシステム。

クロスポイントメモリセル、不揮発性メモリアレイ、メモリセルを読み出す方法、メモリセルをプログラミングする方法、メモリセルへの書き込み方法およびメモリセルからの読み出し方法が記述される。一実施形態においては、クロスポイントメモリセルは、第一の方向に伸長するワード線と、第一の方向とは異なる第二の方向に伸長するビット線とを含み、ビット線およびワード線は、お互いに物理的に接触することなく交差する。クロスポイントメモリセルは、そのように交差する位置でワード線およびビット線の間に形成されるキャパシタを含む。キャパシタは、ワード線からビット線へと流れる直流電流およびビット線からワード線へと流れる直流電流を妨げるように構成された誘電体材料を含む。  (もっと読む)

(もっと読む)

リセス埋込ダイを備えるコアレスパッケージ

マイクロエレクトロニクスパッケージ構造を形成する方法、及びそれによって形成される構造物が提供される。該方法は、めっき部材に、ダイを保持するためのキャビティを形成し、前記キャビティ内にダイを取り付け、前記ダイに隣接して誘電体材料を形成し、前記ダイに隣接して前記誘電体材料内にビアを形成し、前記ビア内にPoPランドを形成し、前記ビア内にインターコネクトを形成し、その後、前記めっき部材を除去して、前記PoPランドと前記ダイとを露出させることを有し、前記ダイは前記PoPランドより上に配置される。  (もっと読む)

(もっと読む)

半導体メモリ素子及びその製造方法

【課題】電気的特性が向上した半導体メモリ素子及びその製造方法を提供する。

【解決手段】本発明の半導体メモリ素子は第1電極及び第2電極を含む。第1元素を含む可変抵抗物質パターンが第1及び第2電極の間に提供される。第1スペーサは可変抵抗物質パターンに隣接して提供される。

(もっと読む)

相変化メモリアレイのための方法

相変化メモリアレイを操作する方法を開示する。方法は、相変化メモリアレイに書き込まれるパターンを決定することと、パターンに従って、2つまたはそれ以上の適切なリセットシーケンスを相変化メモリアレイ上で実行し、相変化メモリアレイにパターンを書き込むことと、を含む。別の方法は、相変化メモリアレイ上でセットシーケンスを実行することと、相変化メモリアレイの適切な読み出しを実施し、セットシーケンスの実行から得られるパターンを取得することと、を含む。 (もっと読む)

記憶装置

【課題】ロジック回路を増やすことなく、第三者がメモリセルにアクセスできずかつ必要な場合にはいつでもアクセス可能なメモリセルを有する記憶装置を提供する。

【解決手段】本実施形態は、第1のメモリセルと、第2のメモリセルと、を有し、第2のメモリセルに設けられた第2のトランジスタの第2のチャネルが酸化物半導体膜からなる記憶装置であって、第2のメモリセルからのデータの読み出しは第2のトランジスタに紫外線を照射している時に行われる記憶装置によって解決する。

(もっと読む)

半導体装置の製造方法

【課題】POPの場合、下段パッケージの中央部には、半導体チップが搭載されているため、上段パッケージの半田ボールを周縁部に配置しなければならない等の制約がある。そこで、下段パッケージの上面に、サブ基板を配置することで、上段パッケージの様々なボール配置、あるいは様々なチップ部品を搭載することに対応できる。このようなデュアルフェイス型パッケージの場合、サブ基板の表面には複数の接続用ランドが配置される。そのため、テスト工程においてパッケージをソケット内に収納する際、サブ基板の表面を吸着することが困難となる。

【解決手段】本願の一つの発明は、デュアルフェイス型パッケージの電気的なテストにおいて、半導体パッケージの周辺部を保持した状態で、半導体パッケージをテスト用ソケットに搬送し、電気的なテストの後、そこから搬出する半導体装置の製造方法である。

(もっと読む)

半導体システム

【課題】複数のエリアを有する半導体システムにおいて不使用エリアにおける消費電力を削減する。

【解決手段】内部電源発生回路70b〜70dを其々有する複数のコアチップCC0〜CC7と、コアチップCC0〜CC7を制御するインターフェースチップIFと、を備えた半導体システムであって、前記インターフェースチップIFはコアチップCC0〜CC7の不使用チップ情報DEFを保持する不使用チップ情報保持回路33を備える。コアチップCC0〜CC7は其々対応する不使用チップ情報DEFを不使用チップ情報保持回路33から受け、該不使用チップ情報DEFが不使用状態を示すときには内部電源発生回路70b〜70dを非活性とし、使用状態を示すときには内部電源発生回路70b〜70dを活性とする。これにより、不使用チップにおける無駄な電力消費が削減される。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通電極の基板からの抜け落ちを防止する。

【解決手段】半導体装置は、基板80と、基板80に設けられた1又は複数のビアホール91と、1又は複数のビアホール91内にそれぞれ設けられた貫通電極TSVとをそれぞれ有する複数のコアチップと、貫通電極TSVを通じて各コアチップと電気的に接続するインターフェースチップとを備え、ビアホール91は、両端部の径r1,r3に比べて中央部r2の径が大きいボーイング形状部分91aを有する。

(もっと読む)

半導体装置

【課題】従来のメモリ素子とは異なり、軟化又は溶融といった状態変化を利用したメモリ素子を提供し、メモリ容量が増大されたメモリ装置を提供することを課題とする。

【解決手段】一対の電極間に、ガラス転移温度が異なる複数のメモリ材料層を積層させたメモリ素子である。ガラス転移温度は10℃以上の差があると好ましい。このようなメモリ素子に電圧を印加することで、複数のメモリ材料層を一つずつ軟化又は溶融させる。このような構成により、メモリ容量が3値以上となり増大される。

(もっと読む)

積層型半導体装置およびチップ自動認識選択回路

【課題】貫通電極によって共通接続された積層型半導体装置を構成する各半導体チップを別々に動作させる。

【解決手段】積層される半導体チップに設けられたチップ自動認識選択回路900a〜900eは、それぞれ、入力されるパルス信号の周期を2倍の周期に変換し出力する周期変更回路12(TFF回路)と、周期変更回路12の入力の論理レベルが、他の全ての周期変更回路12の入力の論理レベルと異なる時間に、半導体チップに対し共通に供給されるチップ選択アドレス信号B0、B1、B2を取り込み、自己チップアドレスとして記憶する自己アドレス記憶回路(ラッチ回路LC1〜LC5)と、チップ選択アドレスと自己チップアドレスとを比較して一致判定を行う判定回路(比較回路13)とを備える。

(もっと読む)

積層型半導体装置

【課題】積層された複数の半導体チップ間で貫通電極切替情報を共有する。

【解決手段】複数の半導体チップ間でデータ転送を行うための複数の貫通電極を互いに共有した積層型半導体装置であって、複数の半導体チップに含まれる第1の半導体チップIFは、複数の貫通電極のうちデータ転送を行う貫通電極を指定する貫通電極切替情報SWを保持し、複数の半導体チップに含まれる第2の半導体チップCC0〜CC7に貫通電極切替情報SWを転送する。本発明によれば、貫通電極切替情報SWが第1の半導体チップIFから第2の半導体チップCC0〜CC7に転送されることから、第2の半導体チップには貫通電極切替情報SWを不揮発的に記憶する回路を設ける必要がない。これにより、第2の半導体チップのチップ面積を縮小することが可能となる。

(もっと読む)

半導体記憶装置及びこれを備える情報処理システム

【課題】複数のコアチップとインターフェースチップからなる半導体記憶装置において、従来の半導体記憶装置との互換性を確保する。

【解決手段】互いに異なるチップ識別情報LIDが割り当てられた複数のコアチップCC0〜CC7と、コアチップCC0〜CC7を制御するインターフェースチップIFとを備える。インターフェースチップIFは、メモリセルを特定するためのアドレス情報ADDを受け、その一部をチップ識別情報LIDと比較するためのチップ選択情報SELとしてコアチップCC0〜CC7に共通に供給する。これにより、コントローラからは単にアドレス空間が拡大されたように見えるだけであることから、従来の半導体記憶装置と同じインターフェースを用いることが可能となる。

(もっと読む)

半導体記憶装置及びこれを備える情報処理システム

【課題】複数のコアチップとインターフェースチップからなる半導体記憶装置において、I/O構成の切り替えを容易とする。

【解決手段】互いに異なるチップ識別情報LIDが割り当てられた複数のコアチップCC0〜CC7と、コアチップCC0〜CC7を制御するインターフェースチップIFとを備える。インターフェースチップIFは、外部との間で同時に入出力する単位外部データのビット数が可変であり、チップ識別情報LIDと比較するためのチップ選択情報SELを、単位外部データのビット数に応じて可変とする。これにより、I/O構成の変更に伴うページ構成の切り替えを不要とすることが可能となる。

(もっと読む)

半導体記憶装置及びデータ処理システム

【課題】複数のコアチップとインターフェースチップからなる半導体記憶装置においてリフレッシュ動作時におけるピーク電流を低減する。

【解決手段】予め互いに異なるチップ情報LIDが付与される複数のコアチップCC0〜CC7を備え、内部リフレッシュコマンドREFaを互いにタイミングの異なる複数のリフレッシュコマンドREFbに分割し、分割されたリフレッシュコマンドREFbのカウント値C2とチップ情報LIDの少なくとも一部とが互いに一致したコアチップにおいてリフレッシュ動作が実行される。これにより、複数のコアチップCC0〜CC7に内部リフレッシュコマンドREFbが共通に供給される場合であっても、各コアチップにおけるリフレッシュ動作のタイミングをずらすことが可能となる。これにより、リフレッシュ動作時におけるピーク電流を低減することが可能となる。

(もっと読む)

半導体装置及びその制御方法並びにデータ処理システム

【課題】複数のコアチップから出力されるリードデータをインターフェースチップにおいて正しく取り込む。

【解決手段】コアチップCC0〜CC7は、パラレルデータの出力に同期したタイミング信号DRAOIFをインターフェースチップIFに出力するタイミング制御回路100を含み、インターフェースチップIFは、タイミング信号DRAOIFに同期してパラレルデータを取り込むデータ入力回路25iを含む。これにより、パラレルデータの出力タイミングと、パラレルデータの取り込みタイミングがいずれもコアチップによって生成されるタイミング信号に同期することから、各コアチップとインターフェースチップとの間に動作速度差がある場合であっても、インターフェースチップ側においてパラレルデータを正しく取り込むことが可能となる。

(もっと読む)

81 - 100 / 222

[ Back to top ]