Fターム[5F083ZA23]の内容

Fターム[5F083ZA23]の下位に属するFターム

窓/開口を有するもの (5)

リードフレーム (23)

Fターム[5F083ZA23]に分類される特許

21 - 40 / 222

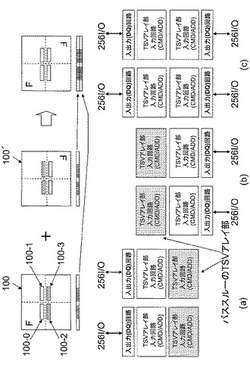

半導体装置及びその製造方法

【課題】TSV構造を採用し複数のチップをスタックした半導体装置を、改良された入出力形式で提供できるようにする。

【解決手段】複数のチップをスタックしてなり、隣り合うチップ間の接続を、貫通電極を介して行なうTSV構造を持つ半導体装置に適用される。各チップは複数のチャンネルに対応した複数のTSVアレイ部を備え、該複数のTSVアレイ部は、スタックするチップの数に応じて入出力に寄与するTSVアレイ部と入出力回路に接続されないパススルーのTSVアレイ部とに分けられている。スタックするチップの数に応じて2段目以降のチップを面方向に回転させてスタックし、前記パススルーのTSVアレイ部を経由してデータの入出力を行なう構成とすることにより、前記データの入出力に寄与するTSVアレイ部にのみ共有の入出力回路を備える構成とし、入出力回路の数を低減させた。

(もっと読む)

半導体装置

【課題】消費電力の低減と干渉の抑制を実現できる半導体装置を提供する。

【解決手段】半導体装置は、直列に多段接続された第1及び第2のチップと制御チップとを備える。第1及び第2のチップのそれぞれの転送制御部は、識別信号が制御チップから供給されると当該識別信号後段のチップへ伝送し、制御チップが供給するクロック信号のn番目のパルスに基づいて、識別信号が表す識別情報を第2の記憶領域に書き込み、書き込みが終了するまでクロック信号の後段のチップへの伝送を阻止する。制御チップは、コマンドによって第1及び第2のチップを排他的にアクセスし、第1及び第2のチップのスイッチ制御回路は、コマンド及び識別情報に応じてそれぞれ対応する第1のスイッチ回路を互いに排他的に制御する。

(もっと読む)

半導体モジュール及びモジュール基板

【課題】モジュール基板の短辺方向における搭載マージンを確保しつつ、モジュール基板に形成する配線の低密度化及び等長化を図る。

【解決手段】モジュール基板20と、モジュール基板20に搭載された複数の半導体装置、例えばDRAM101〜136とを備える。X方向に隣接する2つのDRAMの搭載方向は互いに180°異なっており、Y方向に隣接する2つのDRAMの搭載方向も互いに180°異なっている。これにより、斜め方向に位置するDRAMをフライバイ方式で接続すれば、モジュール基板20に設ける配線の低密度化及び等長化を図ることが可能となる。

(もっと読む)

半導体装置

【課題】貫通電極を用いた積層型の半導体装置において不良のある信号経路を救済する。

【解決手段】インターフェースチップIFと、互いに積層されたコアチップCC0〜CC7と、コアチップCC0〜CC7を貫通する複数の貫通電極TSV3により構成され、コアチップCC0〜CC7をインターフェースチップIFにそれぞれ個別に接続する複数の第1の信号経路と、コアチップCC0〜CC7を貫通する複数の貫通電極TSV1により構成され、コアチップCC0〜CC7をインターフェースチップIFに共通接続する第2の信号経路と、複数の第1の信号経路のいずれかを第2の信号経路に置換する切り替え回路110とを備える。本発明によれば、貫通電極の全てに切り替え回路を設ける必要がなくなる。また、救済のために追加する貫通電極の数も最小限に抑えられることから、チップ面積の増大を抑制することも可能となる。

(もっと読む)

半導体装置

【課題】複数の半導体チップが積層された構造を有する半導体装置において、パンプ電極BP_0に接触せずに、かつ、貫通電極TSV_0の負荷容量を増やさずにテストできる半導体装置10を提供する。

【解決手段】積層された複数の半導体チップ21〜24のそれぞれが、バンプ電極BP_0と、テストパッドPAD_0と、テストパッドから供給される信号を受け取りバンプ電極に供給するテストバッファTD_0と、テストバッファの活性状態と非活性状態とを制御する制御信号を供給するバッファ制御部BCとを含む。

(もっと読む)

半導体装置

【課題】従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタがオン・オフするのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。また、トランジスタの微細化を進めて集積化を図っても、メモリ容量を増加させるためには、半導体装置の面積が大きくなるといった問題があった。

【解決手段】酸化物半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。また、トレンチ構造の酸化物半導体を有するトランジスタにより、半導体装置の記憶素子を構成し、該記憶素子を複数積層することで、半導体装置の回路面積を縮小することができる。

(もっと読む)

記憶装置、及び半導体装置

【課題】プロセスを複雑化させることなく、単位面積あたりの記憶容量を高めることができる記憶装置を提案する。

【解決手段】複数のメモリセルと、複数のワード線と、複数のビット線とを有し、複数のメモリセルは、スイッチング素子と、第1の電極及び第2の電極を有する容量素子と、をそれぞれ有し、複数のメモリセルの少なくとも1つにおいて、複数のワード線のうち一のワード線に与えられる電位に従って、スイッチング素子が複数のビット線のうち一のビット線と第1の電極の接続を制御し、なおかつ、第2の電極が複数のワード線のうち一のワード線とは異なる一のワード線に接続されている記憶装置。

(もっと読む)

半導体記憶装置

【課題】電源電圧の供給の停止及び再開を行う構成において、揮発性の記憶装置と不揮発性の記憶装置との間のデータの退避及び復帰の必要のない半導体記憶装置を提供する。

【解決手段】不揮発性の半導体記憶装置とする際、揮発性の記憶装置と不揮発性の記憶装置を分離することなく構成する。具体的に半導体記憶装置には、酸化物半導体を半導体層に有するトランジスタ及び容量素子に接続されたデータ保持部にデータを保持する構成とする。そしてデータ保持部に保持される電位は、電荷をリークすることなくデータの出力が可能なデータ電位保持回路及び電荷をリークすることなくデータ保持部に保持した電位を容量素子を介した容量結合により制御可能なデータ電位制御回路で制御される。

(もっと読む)

記憶装置

【課題】リフレッシュ動作の回数を減らすことで、消費電力を抑える。また、先に書き込んだデータを破壊することなく、データを読み出す。

【解決手段】ソースまたはドレインの一方となる第1の電極と、ソースまたはドレインの他方となる第2の電極と、第1のチャネル形成領域に絶縁膜を介して重畳して設けられた第1のゲート電極と、を有する第1のトランジスタと、ソースまたはドレインの一方となる第3の電極と、ソースまたはドレインの他方となる第4の電極と、第2のチャネル形成領域が第2のゲート電極と第3のゲート電極との間に絶縁膜を介して設けられた第2のトランジスタと、を有するメモリセルを複数有し、第1のチャネル形成領域及び第2のチャネル形成領域は、酸化物半導体を含んでおり、第2の電極は、第2のゲート電極に直接接続されている記憶装置とする。

(もっと読む)

半導体構造

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、半導体構造を提供することを目的とする。

【解決手段】下部誘電層(151)へ接合された基板(103)、および、下部電極(121)を通じて前記下部誘電層(151)と接合される垂直方向半導体装置(111)を含む半導体構造であって、前記垂直方向半導体装置(111)は、n+−p−n+層(124)を有する隔離構造(135)を含む。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】シリサイド層を有するトランジスタにおいて、オン電流の高いトランジスタを得ることを課題とする。さらに、加熱処理等の工程を増やさずにオン電流の高いトランジスタを得ることを課題とする。

【解決手段】チャネル形成領域、不純物領域及びシリサイド層を有するシリコン膜と、ゲート絶縁膜と、ゲート電極と、不純物領域にシリサイド層を介して電気的に接続する配線とを有し、シリサイド層断面は、チャネル形成領域側の端点から膜厚が増加している第1領域と、第1領域と比べて膜厚が一定である第2領域とを有する半導体装置において、第1領域と第2領域は、シリサイド層断面の端点を通り、水平線とθ(0°<θ<45°)の角度をなす直線がシリサイド層と不純物領域の界面と交わる点を通り、且つ水平線に対し垂直な線で分けられ、シリコン膜の膜厚に対する第2領域の膜厚比は0.6以上である。

(もっと読む)

半導体メモリ装置、半導体メモリパッケージ、及び半導体メモリ装置の集積度増大方法

【課題】半導体メモリ装置、半導体メモリパッケージ、及び半導体メモリ装置の集積度増大方法を提供すること。

【解決手段】半導体メモリ装置は、2の指数ビットの集積度で形成された揮発性メモリセル及び揮発性メモリセルのデータ入出力のための入出力端子を各々具備し、1つのチップに形成することによってインテリム集積度(interim density)を有する複数のメモリ領域、並びに、外部から入力されるコマンド及びアドレスに基づいて複数のメモリ領域にデータを書き込みするか、または、複数のメモリ領域からデータを読み出しする動作を制御する少なくとも1つ以上の周辺領域を含む。従って、半導体メモリ装置は、インテリム集積度、即ち、2m+2n+2o…(ただし、m、n、oは0以上の整数として互いに相異する)の集積度を有することができる。

(もっと読む)

半導体チップのクラックのチェックテスト構造を有する半導体装置

【課題】半導体チップ積層後に、チップごとにクラックの有無検出可能な半導体装置の提供。

【解決手段】積層半導体装置において、半導体チップ21〜24は、基板10とこの表裏面の対向する位置に形成した対のテスト端子と配線61を備える。これらは、一対の(表側)第1のテスト端子621h、(裏側)第1のテスト端子621t及び複数対の(表側)第2のテスト端子622〜625h、(裏側)第2のテスト端子622〜625tで、貫通電極TSVT1が(表側)第1のテスト端子と(裏側)第1のテスト端子を接続し、貫通電極TSVT2〜5が対の(表側)第2のテスト端子と(裏側)第2のテスト端子同士を接続し、配線は、一端が第1のテスト端子と、他端が第2のテスト端子の一つに接続され、基板の外周に沿って延びる。また異なる半導体チップの上下に隣接する第2のテスト端子同士も接続する。

(もっと読む)

半導体記憶装置

【課題】不揮発性の記憶装置を有するCAMとする際に、メモリセルの低消費電力化を図ることのできる半導体記憶装置を提供することを課題の一とする。また、データの書き込みを繰り返し行う際の劣化をなくすことができる半導体記憶装置を提供することを課題の一とする。また、メモリセルの高密度化が可能な不揮発性の記憶装置を提供する。

【解決手段】酸化物半導体を半導体層に有する第1のトランジスタ及び当該第1のトランジスタをオフ状態とすることで書き込んだデータに対応する電位を保持できる容量素子を有するメモリ回路と、書き込んだ電位を参照するための参照回路を有し、参照回路を構成する第2のトランジスタの導通状態を検出することで、整合するデータのアドレスを取得し、高速な検索機能を可能にした半導体記憶装置である。

(もっと読む)

半導体メモリ装置及びそのリペア方法

【課題】リペア過程が簡素化された半導体メモリ装置及びそのリペア方法を提供する

【解決手段】半導体メモリ装置200は、複数のメモリセルを含む第1のメモリチップないし第3のメモリチップ210〜230と、第1のリペアチップ240とを備え、第1のリペアチップ240は、第1のメモリチップないし第3のメモリチップ210〜230のそれぞれに含まれた複数のメモリセル212A,212B,・・・のうち、欠陥が発生した任意のメモリセルをリペアするための第1のヒューズ回路ないし第3のヒューズ回路241A,241B,243A,243B,245A,245Bと、メモリチップ210〜230毎に欠陥が発生した任意のメモリセルを代替するための、複数の第1のリダンダンシメモリセルないし第3のリダンダンシメモリセル242A,242B,244A,244B,246A,246Bとを含む。

(もっと読む)

半導体装置、及び半導体装置の制御方法。

【課題】簡便な半導体装置の評価試験を実現する。

【解決手段】半導体装置10は、それぞれ内部信号MAを生成する第1及び第2のコアチップCC0,CC1を備え、第1及び第2のコアチップCC0,CC1のそれぞれに、貫通電極を介して他方のコアチップとスパイラル接続された第2及び第3のノードN2,N3を設け、この第2及び第3のノードN2,N3を介して、観測対象の内部信号MAを外部に出力することを技術思想とするものである。こうして出力される複数の内部信号MAを外部のテスター等によって観測することで、各コアチップの評価試験を並列に行える。

(もっと読む)

半導体装置

【課題】とりわけ表面マークの下部に配線タングステンパッドがある場合でも、表面マークのコントラスト低下を抑制する。

【解決手段】メモリチップ31は、配線タングステン階層WTL、第1、第2、第3アルミニウム配線階層1AlL,2AlL,3AlLを備える多層配線構造を備える。各配線層の間には、第1、第2、第3層間絶縁膜315,316,317がそれぞれ形成され、第3アルミニウム配線階層3AlLとポリイミド膜PIとの間には、第4層間絶縁膜318が形成されている。第1のダミーパターンDP1は、第1アルミニウム配線階層1AlLに形成され、第2層間絶縁膜316に覆われている。第2のダミーパターンDP2は、第2アルミニウム配線階層2AlLに形成され、第3層間絶縁膜317に覆われている。第2ダミーパターンDP2は、第1ダミーパターンDP1よりも幅が長い。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜を用いたトランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を作製する。

【解決手段】酸化物半導体膜を用いた半導体装置であるトランジスタにおいて、酸化物半導体膜から水素を捕縛する膜(水素捕縛膜)、および水素を拡散する膜(水素透過膜)を有し、加熱処理によって酸化物半導体膜から水素透過膜を介して水素捕縛膜へ水素を移動させる。具体的には、酸化物半導体膜を用いたトランジスタのゲート絶縁膜を、水素捕縛膜と水素透過膜との積層構造とする。このとき、水素透過膜を酸化物半導体膜と接する側に、水素捕縛膜をゲート電極と接する側に、それぞれ形成する。その後、加熱処理を行うことで酸化物半導体膜から脱離した水素を、水素透過膜を介して水素捕縛膜へ移動させることができる。

(もっと読む)

半導体装置

【課題】積層型の半導体装置においてリードデータの有効幅(ウィンドウ幅)を十分に確保する。

【解決手段】積層された複数のコアチップCC0〜CC7と、コアチップを制御するインターフェースチップIFとを備える。コアチップのそれぞれは、メモリセルアレイ70と、データ用の貫通電極TSV1と、メモリセルアレイ70から読み出されたリードデータをデータ用の貫通電極TSV1に出力する出力回路RBUFOとを備える。コアチップにそれぞれ設けられたデータ用の貫通電極TSV1は互いに共通接続され、コアチップにそれぞれ設けられた出力回路RBUFOはインターフェースチップIFより供給されるリードクロック信号RCLKDDに応答して活性化される。これにより、各コアチップの動作速度にばらつきが存在する場合であってもデータバス上でリードデータの競合が生じることがない。

(もっと読む)

半導体装置

【課題】記憶内容に対する保持特性の改善を図ることが可能な半導体装置を提供する。また、半導体装置における消費電力の低減を図る。

【解決手段】チャネル形成領域に、トランジスタのオフ電流を十分に小さくすることができるワイドギャップ半導体材料(例えば、酸化物半導体材料)を用い、且つ、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能となる。また、ゲート電極用のトレンチを有することで、ソース電極とドレイン電極との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

21 - 40 / 222

[ Back to top ]