Fターム[5F083ZA23]の内容

Fターム[5F083ZA23]の下位に属するFターム

窓/開口を有するもの (5)

リードフレーム (23)

Fターム[5F083ZA23]に分類される特許

141 - 160 / 222

メモリセル、電子システム、メモリセルの形成方法、およびメモリセルのプログラミング方法

いくつかの実施形態は、誘電体材料によって互いにスペーシングされる、垂直に積層される電荷捕獲領域を有するメモリセルを含む。誘電体材料は、高k材料を含み得る。電荷捕獲領域のうちの1つ以上は、金属材料を含み得る。かかる金属材料は、ナノドット等の複数の個別の絶縁されたアイランドとして存在し得る。いくつかの実施形態は、メモリセルの形成方法を含み、トンネル誘電体上に2つの電荷捕獲領域が形成され、当該領域は互いに対して垂直に配置され、トンネル誘電体に最も近い領域は、もう1つの当該領域よりも深いトラップを有する。いくつかの実施形態は、メモリセルを含む電子システムを含む。いくつかの実施形態は、垂直に積層される電荷捕獲領域を有するメモリセルのプログラミング方法を含む。  (もっと読む)

(もっと読む)

半導体装置と半導体記憶装置

【課題】配線基板上に半導体素子を多段に積層して半導体装置を構成するにあたって、ワイヤボンディング性を維持しつつ、半導体素子の占有面積を低減する。

【解決手段】配線基板上2には第1の素子群11を構成する複数の半導体素子9A〜9Dが階段状に積層されている。第1の素子群11上には第2の素子群14を構成する複数の半導体素子9E〜9Hが第1の素子群11の階段方向とは逆方向に向けて階段状に積層されている。各半導体素子9は金属ワイヤ13、15を介して配線基板2の接続パッド7と電気的に接続されている。第2の素子群15を構成する複数の半導体素子9E〜9Hのうち、最下段の半導体素子9Eは他の半導体素子9F〜9Hより厚い厚さを有する。

(もっと読む)

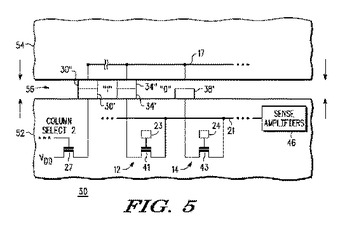

2つの結合された層を用いたプログラマブルROM及び動作方法

3D集積素子(10)として実施された読み出し専用メモリは、第1の層(10’)、第2の層(10’’)及び該第1の層を該第2の層に結合する結合層間接続(28、30、32、34、36、38)を有する。2つの層の間の物理的結合は、読み出し専用メモリのプログラミングを実施する。層はウエハ形式又はダイ形式であってもよい。第1の層は、機能能動素子(26、27、46、48、49)及び少なくとも1つの未プログラミング能動素子(40、41、42、43)を有する。第2の層は、少なくとも1つの未プログラミング能動素子に関連付けられる少なくとも導電性経路(16、17)を有する。結合層間接続は、少なくとも1つの未プログラミング能動素子をプログラミングするために及び導電性経路をプログラミング済み能動素子に提供するために、少なくとも1つの結合されたプログラマブル層間接続(32、34、36、38)を有する。従って、2つの層は、プログラミングされたROMを形成する。2つの層を結合することにより他の種類のプログラマブル記憶素子が実施されてもよい。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置

【課題】負領域に存在する複数の閾値分布を判別する読み出し方式を提案する。

【解決手段】本発明の例に係る不揮発性半導体記憶装置は、半導体領域と、半導体領域内に形成され、第1及び第2拡散層、電荷蓄積層及びコントロールゲート電極を有するセルトランジスタと、第1拡散層に接続されるビット線と、第2拡散層に接続されるソース線と、半導体領域、ビット線、及び、ソース線を制御する制御回路とを備える。制御回路は、ビット線を第1電位にプリチャージした後にビット線をフローティングにする手段と、ビット線がフローティングの状態で半導体領域及びソース線に第2電位を与えてビット線を第1電位から第3電位に変化させる手段と、ビット線を第3電位にした後にセルトランジスタのデータをビット線に読み出す手段とから構成される。

(もっと読む)

半導体デバイス中のノイズの減少

本開示は、半導体デバイス中のノイズを低減する方法、デバイス、モジュール、及びシステムを開示する。一方法の実施形態は、ある期間、半導体デバイスのコントロールゲートにリセット電圧を印加すること、を含む。方法はさらに、リセット電圧を印加した後に、半導体デバイスの状態を検知することを含む。  (もっと読む)

(もっと読む)

半導体メモリ

【課題】メモリセルの微細化と信頼性の向上とを図る。

【解決手段】本発明の例に係る半導体メモリは、アクティブエリアAA1,AA2,・・・と素子分離エリアとが第1方向に交互に配置される周期構造を備え、第1方向の最端部からn(nは奇数)番目のアクティブエリアAAnとn+1番目のアクティブエリアAAn+1とは、第1方向に直交する第2方向の最端部において互いに結合され、閉ループ構造を構成している。

(もっと読む)

不揮発性半導体メモリ・デバイスにおける欠陥を修復するための方法および装置

欠陥をなくすように不揮発性半導体メモリ・デバイスを修復する方法が、半導体パッケージ内に含まれる不揮発性半導体メモリ・デバイスに関するメモリ耐久性インジケータを監視するステップを含む。前記メモリ耐久性インジケータが規定の限度を超えているかどうか判断される。最後に、メモリ耐久性インジケータが規定の限度を超えているという判断に応答して、デバイスがアニール処理される。  (もっと読む)

(もっと読む)

NAND型不揮発性半導体メモリ

【課題】プログラム済みセルの閾値変動が生じないプログラム方法を提案する。

【解決手段】本発明の例に係るNAND型不揮発性半導体メモリは、互いに直列接続されるn個のメモリセル(nは3以上の整数)と、n個のメモリセルの一端とソース線との間に接続される第1セレクトゲートトランジスタと、n個のメモリセルの他端とビット線との間に接続される第2セレクトゲートトランジスタと、プログラミング時に、n個のメモリセルのうち、選択された第1メモリセルのコントロールゲート電極に第1電圧を印加し、第1メモリセルに隣接する第2メモリセルのコントロールゲート電極に第1電圧よりも低い第2電圧を印加し、第1及び第2メモリセル以外の第3メモリセルのコントロールゲート電極に第2電圧よりも低い第3電圧を印加するドライバとを備える。第1、第2及び第3電圧は、n個のメモリセルをそれらの閾値によらずオンにする値以上である。

(もっと読む)

フラッシュメモリ

【課題】電荷保持能力を回復することが可能なフラッシュメモリを提供する。

【解決手段】フラッシュメモリ10は、フラッシュメモリ回路が形成された半導体チップ16と、フラッシュメモリ回路に対してアニーリング処理を行うヒータ13と、を備える。また、フラッシュメモリ10は、フラッシュメモリ回路の温度を計測する温度センサ11と、温度センサの検出値に基づいて所定のアニーリング条件に従ってヒータを制御する制御部15と、を備えてもよい。

(もっと読む)

積層メモリ

【課題】特定領域の動作による温度分布の偏りと、それに特性変動を効果的に削減する積層メモリを提供する。

【解決手段】外部からの活性化信号4が第1層の貫通電極1−11に入力されると、この活性化信号4は、まずマット3−1を活性化した後、バンプ2−12を経て第2層の貫通電極1−22に流れてマット3−2を活性化し、バンプ2−23を経て第3層の貫通電極1−33に流れ、マット3−3を活性化し、バンプ2−34を経て第4層の貫通電極1−44に流れマット3−4を活性化する。つまり、活性化信号4は螺旋状に層間の貫通電極を流れ、マット3−1、3−2、3−3、3−4が順次活性化される。

(もっと読む)

半導体装置の製造方法

【課題】共通の構造を有していながら端子の配列が面対称の関係にある2つの半導体チップを有する半導体チップ及び半導体装置並びにこれらの製造方法、回路基板並びに電子機器を提供することにある。

【解決手段】第1の半導体チップ100の第1の端子T1の位置と、第2の半導体チップ200の第2の端子T2の位置とは、面対称の関係にある。第1の半導体チップ100の第1のバッファ回路C1,C2と、第2の半導体チップ200の第2のバッファ回路C1,C2とは、少なくとも設計上同一である。第1及び第2の内部回路(デコーダ11、制御回路21等)は、少なくとも設計上同一である。配線55,61は異なるパターンで形成されてなる。

(もっと読む)

抵抗変化メモリ装置及び集積回路装置

【課題】高速化と低消費電力化が可能な抵抗変化メモリ装置及び集積回路装置を提供する。

【解決手段】抵抗変化メモリ装置は、抵抗変化型メモリセルを用いたメモリチップと、このメモリチップに、メモリセルの状態変化を加速するための温度バイアスを与えるヒータと、を有する。

(もっと読む)

半導体装置及び半導体メモリテスト装置

【課題】動作用の電圧を供給するポンプ回路を各メモリチップから取り去り、ポンプチップとして別チップにしてMCPチップ内に同梱するようにして、メモリチップの出荷前試験を可能にする半導体装置を提供する。

【解決手段】本発明の一実施の形態に係る半導体装置は、複数の不揮発性半導体記憶装置と、前記複数の不揮発性半導体記憶装置を動作させる昇圧電圧を生成する昇圧回路と、前記複数の不揮発性半導体記憶装置の動作シーケンスに基づいて、前記昇圧回路における前記昇圧電圧の生成動作を制御する昇圧回路制御部と、を備える。

(もっと読む)

半導体記憶装置

【課題】歩留まりを向上できる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリチップ15−1〜15−8と、前記複数のメモリチップのいずれか1つが不良チップとなった場合に前記不良チップと置換される冗長用の予備チップ17と、前記複数のメモリチップおよび前記予備チップを同一のパッケージ内に封止する外囲器14とを具備する。

(もっと読む)

不揮発性半導体記憶装置

【課題】 ワイヤボンドを用いてチップ積層を行う場合の課題から解放され、且つ、積層されるチップコストの低減が可能でコスト優位性のある大容量の不揮発性半導体記憶装置を提供する。

【解決手段】 1または複数の少なくともメモリアレイ11と行選択回路12と列選択回路13,14を備えるメモリアレイチップ10と、少なくとも制御回路25〜28と電圧供給回路29と入力インターフェース回路21〜23と出力インターフェース回路24を備えメモリアレイチップ10に対する制御を行う制御チップ20を積層してなり、メモリアレイチップ上の第1貫通電極T1と制御チップ上の第2貫通電極T2が、対応する同士が同位置に整合するように配置され、メモリアレイチップの第1貫通電極と制御チップの第2貫通電極の対応する同士が積層方向に積み重なって相互に電気的に接続し、メモリアレイチップと制御チップの各チップが相互に電気的に接続している。

(もっと読む)

プログラム可能な感知検出器、ソフト・エラーを検出する方法及びDRAMアレイ(高速のDRAMソフト・エラー検出のためのプログラム可能な重イオン感知デバイス)

【課題】プログラム可能な感知検出器、ソフト・エラーを検出する方法及びDRAMアレイを提供する。

【解決手段】本発明の態様は、高速化されたDRAMソフト・エラー検出のためのプログラム可能な重イオン感知デバイスに関する。DRAMベースのアルファ・イオン粒子感知装置の設計は、高速化されたオン・チップSERテスト装置として使用されることが望ましい。多様な度合いのSER感度を達成するために、感知装置には、プログラム可能感知マージン、リフレッシュ率及び供給電圧が与えられる。更に、デュアル・モードのDRAMアレイが提案され、その結果、アレイの少なくとも一部が、ソフト・エラー検出(SED)モードの間、高エネルギー粒子の活動をモニタするために使用され得る。

(もっと読む)

半導体装置の作製方法

【課題】外部からの局所的押圧による非破壊の信頼性が高い半導体装置を歩留まり高く作製する方法を提供する。

【解決手段】単結晶半導体基板またはSOI基板を用いて単結晶基板またはSOI基板を用いて形成された半導体素子を有する素子基板を形成し、素子基板上に有機化合物または無機化合物の繊維体を設け、素子基板及び繊維体上から有機樹脂を含む組成物を塗布し、加熱することにより、素子基板上に有機化合物または無機化合物の繊維体に有機樹脂が含浸された封止層を形成して半導体装置を作製する。

(もっと読む)

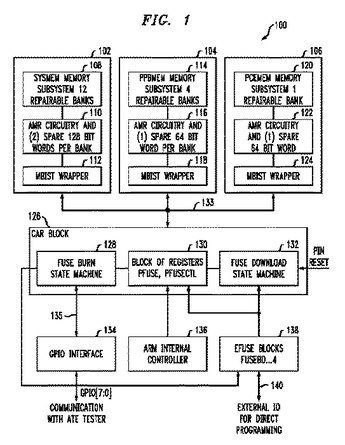

ヒューズ焼付け状態機械及びヒューズダウンロード状態機械に基づく内蔵メモリ修理方法

内蔵メモリ内の1以上の不良を修理するためのメモリ修理回路は少なくとも1つのヒューズレジスタ及び当該ヒューズレジスタに結合された状態機械回路を含む。状態機械回路は、(i)内蔵メモリ内の1以上の不良に関するステータス情報を受信し、(ii)ステータス情報に基づいてメモリが修理可能かを判断し、(iii)メモリが修理可能であるとみなされるときは、メモリの不良メモリセルに対応するアドレスを記憶し、(iv)メモリ修理回路に供給された電圧源を用いて、不良メモリセルに対応するアドレスをヒューズレジスタに焼き付け、及び(v)不良メモリセルに対応するアドレスがヒューズレジスタに焼き付けられたことを確認するように動作する第1の状態機械を実装する状態機械回路を備える。状態機械回路がさらに、(i)少なくとも1つのヒューズレジスタに記憶された情報を内蔵メモリに関連する少なくとも1つの修理レジスタにダウンロードし、及び(ii)アドレスが内蔵メモリ内の不良メモリ部分に対応する回路で受信されると、不良メモリ部分へのアクセスを少なくとも1つの修理レジスタに再ルーティングするように動作する第2の状態機械を実装する。  (もっと読む)

(もっと読む)

不揮発性メモリ素子、その製造方法及び半導体チップ

【課題】高集積化が容易であり、高い信頼性を持つ不揮発性メモリ素子及びその製造方法を提供する。

【解決手段】基板上105に形成され、第1導電型の第1ドーピング層115と、第1ドーピング層115から基板105の一面に対して上向きに伸長し、第1導電型と逆の導電性を有する第2導電型の半導体柱120と、半導体柱120の側壁を一回り取り囲む制御ゲート電極150aと、半導体柱120と制御ゲート電極150aとの間に介在された電荷保存層140aと、半導体柱120と電気的に連結されるように半導体柱120上に配置され、第1導電型の第2ドーピング層130と、を備える不揮発性メモリ素子。

(もっと読む)

不揮発性RAM

【課題】アプリケーションに頻繁にアクセスされるワーク領域と、プログラムコードを記憶させる領域とを、従来に比較して小型なチップサイズにて、1チップで構成することができる不揮発性RAMを提供する。

【解決手段】本発明の不揮発性RAMは、ランダムにデータの読み書きを行う不揮発性メモリであり、電源を切っても記憶内容が失われない不揮発性モード、及び電源を切ると記憶内容が失われる揮発性モードのデータ保持状態に、データ保持の状態を制御可能なメモリ素子からなるメモリ領域と、該メモリ領域において、不揮発性モード書込及び揮発性モード書込各々の対象となるアドレス範囲の領域が設定されるアドレス設定レジスタと、該アドレス設定レジスタを参照して、それぞれのアドレス範囲に対応したデータの書き込みを行うメモリ制御回路とを有する。

(もっと読む)

141 - 160 / 222

[ Back to top ]