Fターム[5F092AC04]の内容

Fターム[5F092AC04]の下位に属するFターム

異方性磁気抵抗効果素子(AMR) (102)

巨大磁気抵抗効果素子(GMR) (891)

トンネル磁気抵抗効果素子(TMR) (1,677)

超巨大磁気抵抗効果素子(CMR、ColossalMR) (23)

弾道磁気抵抗効果素子(BMR、BalisticMR) (35)

Fターム[5F092AC04]に分類される特許

21 - 40 / 145

メモリ装置およびそのプログラミング方法

【課題】磁気層を用いて選択することができるマルチビットメモリのための装置および関連する方法を提供する。

【解決手段】高保磁力を有する第1および第2の記憶層の間に配置される低保磁力を有する第1の選択層を配置し、第1の選択層の磁気飽和に応答して、第2の記憶層への論理状態のプログラミングが許可され、各ビットが選択的にプログラムされることにより、マルチビットメモリが達成され、データ記憶容量を増加することができる。

(もっと読む)

磁気ヘッド、およびこれを備えたディスク装置

【課題】ライトマージンを上げることにより、記録密度を向上させることが可能な磁気ヘッド、およびこれを備えたディスク装置を提供する。

【解決手段】ディスク装置の磁気ヘッドは、記録媒体12の記録層23に対し垂直な記録磁界を印加する主磁極66と、主磁極のトレーリング側にライトギャップを置いて対向し、主磁極とともに磁気回路を形成するリターン磁極68と、主磁極およびリターン磁極が形成する磁気回路に磁束を励起するコイル65と、それぞれ主磁極とリターン磁極との間に設けられ、磁気共鳴周波数の互いに異なる複数の磁性膜を有し、記録媒体に高周波磁界をそれぞれ印加する複数の高周波発振素子70a、70bと、高周波発振素子に通電するための電気回路80と、を備えている。

(もっと読む)

プラズマ処理方法

【課題】200〜500nmの厚さの磁性膜を高速エッチングし、良好な微細加工が可能なドライエッチング方法を提供することである。

【解決手段】本発明は厚さが200nmから500nmの磁性膜をドライエッチングするプラズマ処理方法において、レジスト膜と、前記レジスト膜の下層膜である非有機系の膜と、前記非有機系の膜の下層膜であるCr膜と、前記Cr膜の下層膜であるAl2O3膜とを含む積層膜を前記磁性膜の上に成膜した試料をドライエッチングすることを特徴とするプラズマ処理方法である。

(もっと読む)

長尺型磁気センサ

【課題】隣接する磁石同士の間隙部に生じる感度低下を抑制する。

【解決手段】磁気抵抗素子の感磁部20は、磁気抵抗層の上面に電極材料からなる複数のショートバーが形成されたものである。磁気抵抗部はショートバー22で覆われていない部分である。紙幣に印刷された磁性体が通過する際、その通過位置によって磁気抵抗素子の抵抗値の変化率(素子感度)が異なる。磁気抵抗素子の抵抗値の変化率は、感磁部における磁気抵抗部の密度が高いほど大きい。そのため、隣接する磁石同士の間隙部上または隣接する磁気抵抗素子の間隙部付近に位置する感磁部20の磁気抵抗部の密度をその他の領域に比べて相対的に高めることにより、磁石同士の間隙部での感度低下が抑制される。

(もっと読む)

半導体磁気センサ及びそれを用いた磁性体検出装置

【課題】ノイズの影響が低減され、かつ、増幅歪みの少ない半導体磁気センサ及びそれを用いた磁性体検出装置を提供すること。

【解決手段】直列接続された第1の半導体磁気抵抗素子11及び第2の半導体磁気抵抗素子12と、第1の半導体磁気抵抗素子11及び第2の半導体磁気抵抗素子12の接続ノードにゲート電極が接続された電界効果トランジスタ10とを備えている。電界効果トランジスタ10のゲート電極の幅を第1の半導体磁気抵抗素子11及び第2の半導体磁気抵抗素子12の各中心点を結んだ直線に投影した時の長さが、第1の半導体磁気抵抗素子11及び第2の半導体磁気抵抗素子12の各中心点の直線距離の略偶数倍であるように構成されている。

(もっと読む)

磁気検出装置およびその製造方法

【課題】回転センサの製造効率を向上する。

【解決手段】複数のリードフレーム30を支持部材71により支持してなる部材70の複数のリードフレーム30に磁気抵抗素子51をそれぞれ搭載し、リードフレーム30毎に磁気抵抗素子51およびリードフレーム30を断面U字状の永久磁石20の空所内に配置し、永久磁石20、リードフレーム30、および磁気抵抗素子51をリードフレーム30毎にモールド樹脂によって覆い、その後、支持部材71から複数のリードフレーム30をそれぞれ分離して複数の回転センサを得る。

(もっと読む)

スイッチ装置

【課題】永久磁石の磁界を検出する磁気抵抗素子からなる磁気センサを用いたスイッチ装置において、コストを低減することができると共に小型化を図ることができるスイッチ装置を提供する。

【解決手段】本発明のスイッチ装置1は、操作子4と、永久磁石13と、磁気抵抗素子からなる磁気センサと、制御回路とを備えている。操作子4は、第1操作位置と第2操作位置との間で移動可能に設けられている。磁気センサは、永久磁石13からの移動磁界が常に鎖交するように設けられ、鎖交磁界の強さまたは方向を示す信号を出力する。制御回路は、磁気センサからの信号に基づいてスイッチへオンオフ信号を出力する。運動変換手段としてのスリット20及び溝12により、操作子4の第1運動を、その移動距離よりも短い永久磁石13の第2運動に変換する。

(もっと読む)

磁気抵抗センサの電源回路、磁気検出ユニット、及び位置検出ユニット

【課題】少ない部品点数で、磁気抵抗センサの出力温度特性を改善する。あるいは、既製品を利用して、大幅な設計変更をせずに磁気抵抗センサの出力温度特性を改善する。あるいは、磁気抵抗センサについて多相出力がある場合に、それらの出力温度特性を一括して改善する。

【解決手段】磁気抵抗センサの電源回路101aは、磁気抵抗センサに電圧を印加する電源回路であって、磁気抵抗センサに印加する電圧を磁気抵抗センサの温度に応じて可変とすることにより、磁気抵抗センサの温度補償をする温度補償回路を備える。

(もっと読む)

三端子型磁気抵抗効果素子

【課題】 三端子型磁気抵抗効果素子に関し、一次元線状巨大磁気抵抗素子の特性や磁壁の移動を外部から制御する。

【解決手段】 第1の強磁性体層と、前記第1の強磁性体層より保磁力の大きな第2の強磁性体層と、前記第1の強磁性体層と前記第2の強磁性体層との間に設けられた膜厚が単調に変化する非磁性体と、前記第1の強磁性体層上にゲート絶縁膜を介して設けられたゲート電極とを設ける。

(もっと読む)

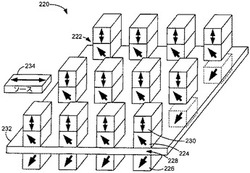

メモリにおける参照セルの書込み動作

磁気センサ

【課題】 無磁場を安定して検出しうる磁気センサを提供することである。

【解決手段】 磁気センサは、磁気抵抗効果素子11が、軟磁性材料からなる磁束吸収体12により覆われているから、この磁束吸収体12が、回路基板1に与えられる磁界の磁束を、その飽和磁束量まで吸収して、当該磁束が磁気抵抗効果素子11に与えられないようにすることができる。状態検出部2は、回路基板の出力電圧Voutに基づいて、回路基板1に与えられた磁界の磁束量が閾値以下である第1の状態と、当該磁界の磁束量が閾値より多い第2の状態とを検出する。ここで、磁束吸収体は、その飽和磁束量が当該閾値となるように定まった形状、または大きさを有する。したがって、磁束吸収体12の形状、または大きさを調整することによって、磁気センサの適用される環境条件に応じ、無磁場である第1の状態と、磁場が存在する第2の状態とのバランスを保つように当該閾値を好適に設定することができる。

(もっと読む)

磁性体検出器

【課題】A相/B相又はA相とZa相/Zb相又はZ相との位相差を小さくし、磁気抵抗効果素子を小型化して回転体の原点検出精度を向上させること。

【解決手段】A相/B相又はA相検出用の磁気抵抗効果素子21とZa相/Zb相又はZ相検出用の磁気抵抗効果素子22とは、同一基板上に同一形状で並設され、かつ運動体に対する配置方向が前記運動体の運動方向に垂直方向である。磁気抵抗効果素子21aと磁気抵抗効果素子21bとの中点の端子電極21AからはA相の信号が、磁気抵抗効果素子21cと磁気抵抗効果素子21dとの中点の端子電極21BからB相の信号が出力される。また、磁気抵抗効果素子22aと磁気抵抗効果素子22bとの中点の端子電極22AからZa相の信号が、磁気抵抗効果素子22cと磁気抵抗効果素子22dとの中点の端子電極22BからZb相の信号が出力される。

(もっと読む)

磁気検出素子、および、これを用いた回転角度検出装置ならびにストローク量検出装置

【課題】圧電効果によって生ずる出力変動を低減できる磁気検出素子を提供する。

【解決手段】磁気検出素子11にて、ダイリード51と各リードは基準平面S上に、第1チップ201と第2チップ202とは基準平面Sの上下に対称に配置される。これにより、それらの部品の熱膨張または熱収縮は、基準平面Sに対称に生じ、磁気検出素子11全体として厚さZ方向の反りを抑制できる。よって、チップ201、202に印加される応力を低減でき、圧電効果によって生ずる出力変動に伴う検出誤差を低減できる。また、この磁気検出素子11を回転角度検出装置ならびにストローク量検出装置に用いることにより、圧電効果の影響を補償するための温度特性補正手段を備える必要がなくなる。

(もっと読む)

磁性体の磁化反転方法、メモリ

【課題】磁性体の磁化の方向を反転させるために必要となる電流量を低減することが可能である、磁性体の磁化反転方法を提供する。

【解決手段】磁性体31と、この磁性体31に接して配置され、電圧の印加により磁性体31の磁気特性を直接的に、或いは、間接的に、変化させることが可能な絶縁体32とを含む素子40を構成する。そして、磁性体31の磁化Mの歳差運動の周期の2分の1の周期で変調させた電圧を、この素子40に対して印加して、素子40の磁性体31の磁化Mの方向を反転させる。

(もっと読む)

磁気抵抗デバイス

【課題】大きな出力信号強度を得られるEMRデバイスに、既存のスライダ形成技術を利用して磁気ヘッドスライダが形成できるような、デバイス構造とデバイス製造方法を提供すること

【解決手段】磁気抵抗デバイスは、基板(4;64)と、第一方向(14)に伸びた細長半導体チャネル(11)素子と、チャネルへの接点の組(27)を提供する少なくとも2つの導電性リード(26)とを含んでいる。デバイスは、チャネルと接続したオプションの半導体シャント(8)を含んでいる。オプションのシャント、チャネル及び接点の組は、第一方向及び基板の表面に対して垂直な第二方向(15)に向かって、基板に対して積重ねられる。デバイスは、チャネルに沿って伸びる側面(30)を有している。デバイスは、側面に対して一般的に垂直な方向の磁場(31)に対して反応する。

(もっと読む)

電子デバイス

【課題】グラフェン層を備えた電子デバイスの高性能化を図る。

【解決手段】電子デバイス100は、結晶性材料からなる下層108と、結晶性材料からなる上層110と、下層108と上層110との間に位置するn−グラフェン層102とを含み、下層108及び/又は上層110が4以上の比誘電率を有する高比誘電率材料からなる電子デバイスである。n−グラフェン層102は、グラフェンの単層構造、又は複数のグラフェン単層の積層構造である。

(もっと読む)

多重系磁気センサのセンサパターン配置構造及びその製造方法

【課題】オフセット電圧のバラツキを低く抑えることができる磁気センサのセンサパターン配置構造及びその製造方法を提供する。

【解決手段】基板2の表面には、センサエレメントをブリッジ状(ホイートストーンブリッジ)に組んだセンサパターン10が複数(本例は10a,10bの2つ)設けられている。第1センサパターン10aは、磁気抵抗11〜14からなる。第2センサパターン10bは、磁気抵抗21〜24からなる。本例の磁気センサ1は、基板2の中心線La,Lbに対して磁気抵抗11〜14,21〜24の基準線Ka1〜Ka4,Kb1〜Kb4が全て斜めを向く配置状態に形成される。

(もっと読む)

磁界センサ

【課題】 調整可能なグラフェンを用いた磁界センサを提供する。

【解決手段】 グラフェンセンス層を採用する磁界センサであって、センス層内を移動する電荷キャリアに作用するローレンツ力が、グラフェン層内を移動する電荷キャリアの経路に変化をもたらす。磁界の存在を示すこの経路の変化を検出することができる。センサは、非磁性の電気的絶縁材料によってグラフェン層から分離される1つまたは複数のゲート電極を含む。ゲート電極へのゲート電圧の印加により、グラフェン層の電気抵抗が変化し、このゲート電圧の印加を用いて、センサの感度および速度を制御することができる。

(もっと読む)

磁気センサの製造方法及び磁気センサ

【課題】少なくとも製造時のパッケージ工程においてセンサに熱が加えられたとしても、オフセット電圧のバラツキを軽減することができる磁気センサの製造方法及び磁気センサを提供する。

【解決手段】磁気センサの基板表面の絶縁層に、ブリッジ状に組んだ磁気抵抗10〜40を成膜する。磁気抵抗10〜40の成膜後、その表面に保護膜を成膜する。保護膜成膜後、その基板部品、即ち基板モジュールをアニールする。このアニール後、磁気抵抗10〜40の粗調部8をレーザトリミングによりカットすることで、磁気抵抗10〜40の抵抗値を調整する。そして、最後に基板モジュールをパッケージする。

(もっと読む)

磁界センサの診断動作モードを生成するための回路および方法

磁界センサは、磁界センサの中で使用される磁界検知素子のセルフテストを含めて磁界センサの回路の大部分またはすべてのセルフテストを可能にする診断回路を含む。磁界センサは、磁界センサが応答する診断磁界を発生することができる。  (もっと読む)

(もっと読む)

21 - 40 / 145

[ Back to top ]