Fターム[5F101BD03]の内容

不揮発性半導体メモリ (42,765) | 素子構造 (12,113) | メモリセル(センサ) (3,677) | MOSトランジスタ (3,641) | SD領域 (1,220)

Fターム[5F101BD03]の下位に属するFターム

S・D平面形状 (20)

S・D断面形状 (141)

S・D深さ (34)

LDD等高耐圧構造(メモリセルの) (599)

不純物ドープ、不純物濃度分布(SDの) (71)

ソースドレイン共用又は入れ替え (269)

Fターム[5F101BD03]に分類される特許

41 - 60 / 86

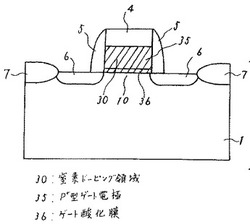

半導体装置及びその製造方法

【課題】ゲート電極中に含まれる不純物の拡散を防止することができ、さらに、ゲート絶縁膜の信頼性及びホットキャリア耐性を向上させることができる半導体装置及びその製造方法を得る。

【解決手段】N型シリコン基板1上にゲート酸化膜36およびP+型ゲート電極35を形成する。P+型ゲート電極35の両側にソース/ドレイン領域6を形成する。ゲート酸化膜36およびP+型ゲート電極35中には窒素がドープされ、窒素ドーピング領域30が形成される。

(もっと読む)

不揮発性半導体メモリ

【課題】選択ゲートトランジスタのGIDLに起因するホットエレクトロンによるメモリセルトランジスタの誤書き込みを低減できる。

【解決手段】本発明に関わる不揮発性半導体メモリは、第1のゲート間隔W1で直列に接続され、隣接するもの同士でソース/ドレイン拡散層6Aを共有する複数のメモリセルトランジスタMT1〜MTnと、メモリセルトランジスタMT1とソース/ドレイン拡散層6A,6Bを共有し、且つ、第2のゲート間隔W2で隣接する第1の選択ゲートトランジスタST1とを具備し、第2のゲート間隔W2は、第1のゲート間隔W1より広く、メモリセルトランジスタMT1と第1の選択ゲートトランジスタST1とで共有するソース/ドレイン拡散層6A,6Bは、メモリセルトランジスタ同士で共有するソース/ドレイン拡散層6Aよりも不純物濃度が高い領域6Bを含む。

(もっと読む)

半導体記憶装置およびその書き込み方法

【課題】同一半導体基板上にロジック回路と半導体不揮発性メモリとを安価に作成する。

【解決手段】メモリセル選択回路21とメモリセルアレイ22との間に第2昇圧回路26を設ける。こうすることによって、第1昇圧回路25によって電源電圧Vddを書き込み電圧である5V程度まで昇圧させた後、メモリセル選択回路21を通過することによって低下した電圧を、メモリセルアレイ22の直前で、第2昇圧回路26によって再度5Vに昇圧することができる。したがって、メモリセル選択回路21,第1昇圧回路25および第2昇圧回路26を構成する各トランジスタに掛る最大電圧は5V程度となる。その結果、通常トランジスタの耐圧を5Vを少し越える程度に設定すれば、製造工程の増加に繋がる高耐圧トランジスタを上記通常トランジスタとは別に作成する必要がなくなり、半導体記憶装置の製造工程が簡略化できると共に、低コストで作成することが可能になる。

(もっと読む)

不揮発性メモリ

【課題】不揮発性半導体メモリのメモリセル当たりの記録データ量を向上させることができる不揮発性メモリを提供する。

【解決手段】データを電気的に書き込み・消去可能なEEPROM等の不揮発性メモリにおいて、前記メモリを構成する各メモリセルが、半導体基板に形成されたソース/ドレイン領域23a、24a、23b、24bと、前記半導体基板のチャネル領域上に形成されるゲート電極27と、前記半導体基板と前記ゲート電極27との間に形成されるシリコン窒化膜を含む3層のゲート絶縁膜26とを備えている。そして、前記ゲート電極側27から平面的に見たときに、前記ソース/ドレイン領域23a、24a、23b、24bが前記チャネル領域から少なくとも3方向に延びる構成を採用する。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】ホットエレクトロンの速度オーバーシュートを抑制することにより、書き込み効率を向上させることのできるNOR型フラッシュメモリ及びその製造方法を提供する。

【解決手段】第1導電型の半導体基板(1)と、半導体基板表面に対峙して形成された第2導電型の不純物拡散領域である一対のソース(2)及びドレイン拡散領域(3)と、ソース及びドレイン拡散領域に挟まれた半導体基板表面のチャネル領域(10)上に順次形成された、ゲート絶縁膜(4)、電荷蓄積層(5)、層間絶縁膜(6)、制御ゲート(7)を備える積層構造とを具備し、ソース拡散領域とチャネル領域との接合位置が積層構造のソース拡散領域に近い端部と離れて形成されている。

(もっと読む)

四つのストレージノード膜を備える不揮発性メモリ素子及びその動作方法

【課題】四つのストレージノード膜を備える不揮発性メモリ素子及びその動作方法を提供する。

【解決手段】第1フィン105a及び第2フィン105bを備え、埋め込み絶縁膜115は、第1フィン105aと第2フィン105bとの間にあり、制御ゲート電極140は、埋め込み絶縁膜の反対側の第1及び第2フィンの側面を覆い、ゲート絶縁膜130は、第1、第2フィン及び制御ゲート電極の間にあり、第1ソース領域及び第1ドレイン領域は第1フィン105aの部分に、第2ソース領域及び第2ドレイン領域は第2フィン105bの部分に、制御ゲート電極から離隔されて形成され、第1ストレージノード膜160a1及び第2ストレージノード膜160a2は、制御ゲート電極を挟んで第1フィン105aの側面上に、第3ストレージノード膜160b1及び第4ストレージノード膜160b2は、制御ゲート電極を挟んで第2フィン105bの側面上に形成される。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】絶縁層の被覆不良によるゲート電極層と半導体層とのショート及びリーク電流などの不良が防止された信頼性の高い半導体装置、及びそのような半導体装置の作製方法を提供することを目的とする。

【解決手段】絶縁表面上に複数の半導体素子を形成するために、連続した一つの半導体層中に半導体素子として機能する素子領域と、PN接合の繰り返しにより素子領域間を電気的に分離する機能を有する素子分離領域を形成する。素子分離領域は、連続した一つの半導体層において、素子間を電気的に分離するために、選択的に酸素、窒素、及び炭素のうち少なくとも一種以上の不純物元素及び接する素子領域と逆導電型を付与する不純物元素を添加して形成する。

(もっと読む)

MOSFETゲート電極のランディング・パッドのための構造および方法

マイクロエレクトロニクス・トランジスタおよび製作方法の性能および製造可能性を強化するための新たな技術を提供する。

【課題】

【解決手段】トランジスタ装置およびそれを形成する方法であって、基板と、基板上の第1のゲート電極と、基板上の第2のゲート電極と、第2のゲート電極に重なり合うフランジ付き端部の対を備えるランディング・パッドとを備え、第2のゲート電極の構造は、ランディング・パッドの構造と不連続である。

(もっと読む)

不揮発性メモリデバイス

ソース領域およびドレイン領域、フィン本体、電荷トラップ積層、およびゲートを有する、半導体基板上のfinFETベース不揮発性メモリデバイスである。フィン本体は、接触部としてソース領域とドレイン領域との間に延在する。電荷トラップ積層は、フィン本体の一部を被覆し、ゲートは、フィン本体のこの位置で電荷トラップ積層を被覆する。フィン本体は、明確な結晶質表面およびこの結晶質表面の間の遷移ゾーンが欠如するフィン本体の外周の少なくとも3/4にわたり角部のない形状を有する。  (もっと読む)

(もっと読む)

不揮発性メモリを有する半導体素子及びその形成方法

【課題】不揮発性メモリを有する半導体素子及びその形成方法を提供する。

【解決手段】メモリセルは、基板上の選択トランジスタ(ST)の選択トランジスタゲート(STG)、STの両側の基板上の第1及び第2メモリセルトランジスタ(MT)の第1及び第2メモリセルトランジスタゲート(MTG)、STと第1及び第2MTGのそれぞれの間の基板内の第1及び第2浮遊接合領域及び第1及び第2MTGのそれぞれを間に挟んで第1及び第2浮遊接合領域のそれぞれの向い側の基板内の第1及び第2ドレイン領域を含むことができる。STGは、ゲート誘電膜パターン及びゲート誘電膜パターン上の選択ゲートを含むことができる。第1及び第2MTGのそれぞれはトンネル絶縁膜パターン、トンネル絶縁膜パターン上の電荷貯蔵膜パターン、電荷貯蔵膜パターン上のブロッキング絶縁膜パターン及びブロッキング絶縁膜パターン上の制御ゲートを含むことができる。

(もっと読む)

炭化ケイ素ベースのアモルファスシリコン薄膜トランジスタを有するスタック不揮発性メモリとその製造方法

スタック不揮発性メモリデバイスは、垂直に積層されたアモルファスシリコンベースの薄膜トランジスタ(301)を用いる。トランジスタもしくはセルの各層は、炭素濃度に応じて炭素豊富なシリコン膜もしくは炭化ケイ素膜を形成するために所定の炭素濃度を有する堆積a-Siチャネル領域層(315)から形成される。誘電体スタック(310)がチャネル領域層の上に形成される。一実施形態では、誘電体スタックはONO構造である。制御ゲート(311)が誘電体スタックの上に形成される。この構造はスタック構造を形成するように垂直方向に繰り返される。一実施形態では、チャネル領域層の炭素濃度は、続けて形成された層毎に減少する。薄膜トランジスタはフィンFETとなり得る。 (もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】書込み速度の向上を図ることができる不揮発性半導体記憶装置およびこの不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】本発明に係る不揮発性半導体記憶装置100は、半導体基板1と、半導体基板1の主表面上に第1絶縁膜15を介して形成されたフローティングゲートFGと、前記フローティングゲートFG上に第2絶縁膜13を介して形成されたコントロールゲートCGと、前記フローティングゲートFGと隣り合う前記半導体基板1の主表面上に形成されたソース領域およびドレイン領域とを備え、前記フローティングゲートの周面のうち、前記ドレイン領域側の側面と底面との境界領域が、前記半導体基板内方に向けて張り出すように湾曲する。

(もっと読む)

ソース/ドレインストレッサ、及び中間誘電体層ストレッサを統合する半導体の製造方法

半導体形成プロセスでは、絶縁構造(106)をトランジスタ領域の横方向のいずれの側にも形成し、ゲート構造(110)をトランジスタ領域の上に形成し、ソース/ドレイン領域(107)を除去してソース/ドレインリセス(120)を形成し、絶縁構造の一部分を除去して絶縁膜後退構造(126)を形成し、そしてソース/ドレインリセスに、エピタキシャル成長半導体のようなソース/ドレインストレッサを充填する。ソース/ドレインリセスの下側表面は、絶縁膜後退構造の上側表面よりも約10〜30nmだけ深いことが好ましい。ソース/ドレインリセスへの充填を行なう前に、または後に絶縁膜後退構造を形成する。次に、ILDストレッサ(140)を、ILDストレッサがソース/ドレイン構造の側壁に隣接するようにトランジスタ領域の上に堆積させることにより、ILDストレッサをソース/ドレインストレッサと組み合わせることができる。ILDストレッサは、圧縮応力または引っ張り応力を与える窒化シリコンであることが好ましく、そしてソース/ドレイン構造はシリコンゲルマニウムまたはシリコン炭素であることが好ましい。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】電荷保持能力の高いフローティングゲート電極を備えた不揮発性半導体記憶装置の製造方法を実現できるようにする。

【解決手段】不揮発性半導体記憶装置の製造方法は、酸素及び水素を含む雰囲気中で熱処理を行うことにより、基板内の半導体領域の上にシリコン酸化膜からなるトンネル絶縁膜を形成する工程(a)と、N2O又はNOを含む雰囲気中で熱処理を行うことにより、トンネル絶縁膜中に窒素を拡散させる工程(b)と、水素を含む雰囲気中で300℃から950℃の温度範囲で熱処理を行うことにより、トンネル絶縁膜中に水素を拡散させる工程(c)と、工程(c)の後、トンネル絶縁膜の上に、メモリゲート電極部8を形成する工程(d)と、半導体領域内のフローティングゲート電極の両側に位置する領域に不純物を導入して、半導体領域とは逆導電型の2つの不純物拡散領域30、31を形成する工程(e)とを含んでいる。

(もっと読む)

不揮発性半導体メモリ及びその製造方法

【課題】国際公開第2004/006337A1に開示された半導体装置を不揮発性半導体メモリに適用し、しかも、電荷を蓄積する浮遊ゲート電極を構成する微小粒子の粒径と密度を制御し得る構造を有する不揮発性半導体メモリを提供する。

【解決手段】不揮発性半導体メモリは、ソース/ドレイン電極17、チャネル形成領域18、第1絶縁層11、浮遊ゲート電極12、第2絶縁層15、並びに、制御電極16を備え、チャネル形成領域18は、導体又は半導体から成るチャネル形成領域構成微粒子21と、チャネル形成領域構成微粒子21と結合した有機半導体分子22とによって構成された導電路20を有し、浮遊ゲート電極12は、導体又は半導体から成る浮遊ゲート電極構成微粒子13と、浮遊ゲート電極構成微粒子を被覆する絶縁材料から成る保護膜14とから構成されている。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】 浮遊ゲート電極の加工形状不良に起因する信頼性、製造歩留まりの低下(ショート、ディスターブ)を防止する。

【解決手段】 補助ゲート4の側壁に形成するサイドウォールスペーサ8は、キャップ絶縁膜の一部を構成する酸化シリコン膜6よりも稠密な膜となるよう、ジクロロシラン(dichlorosilane)を原料として800℃程度の高温で堆積する、いわゆる高温酸化膜(HTO膜)で構成し、さらに成膜後に、成膜温度以上の高温で焼き締めを行う。また、制御ゲートと浮遊ゲートの加工(重ね切り)を、異方性ドライエッチとウェットエッチングとで行う。

(もっと読む)

一対のチャンネル領域に対応する単一ゲート電極を有する半導体素子及びランダムアクセスメモリ

【課題】一対のチャンネル領域に対応する単一ゲート電極を有する半導体素子及びランダムアクセスメモリを提供する。

【解決手段】半導体基板110の一対のフィン105a,105bに形成された一対のチャンネル領域と、一対のチャンネル領域に対応するゲート電極130と、一対のフィン105a,105bに形成されたソースに同時に接するソースコンタクトプラグ135及びドレインに同時に接するドレインコンタクトプラグ140と、を備え、ドレインコンタクトプラグ140上のストレージノードまたはチャンネル領域とゲート電極130との間のストレージノードをさらに備えうる半導体素子である。

(もっと読む)

不連続蓄積素子を含む電子デバイスを形成するための方法

電子デバイスを形成するためのプロセスは、基板(12)内に第1のトレンチ(22、23)を形成する段階を含むことができ、該トレンチは、壁部及び底部を含み且つ基板の主要面から延びる。プロセスはまた、不連続蓄積素子(64)を形成する段階と、不連続蓄積素子のうちの第1の不連続蓄積素子が第1のゲート電極(92)とトレンチの壁部との間に位置するようにトレンチ内に第1のゲート電極を形成する段階とを含むことができる。プロセスは更に、基板の主要面の上に重なる不連続蓄積素子を除去する段階を含むことができる。プロセスは更に、第1のゲート電極及び基板の主要面の上に重なる第2のゲート電極を形成する段階を含むことができる。 (もっと読む)

不連続な記憶要素群を含んだ電子デバイス

電子デバイスは、トレンチ(22、23)内に位置する不連続な記憶要素群(64)を含んでいる。この電子デバイスはトレンチを含む基板(12)を有し、このトレンチは壁部及び底部を含み且つ基板の主表面から延在している。電子デバイスはまた、不連続な記憶要素群を含んでおり、その第1部分は少なくともトレンチ内にある。電子デバイスは更に第1のゲート電極を含んでおり、第1のゲート電極と第1のトレンチの壁部との間に、不連続な記憶要素群の部分の少なくとも一部が位置している。この電子デバイスは更に、第1のゲート電極及び基板の主表面の上に第2のゲート電極を含んでいる。  (もっと読む)

(もっと読む)

トレンチ内にナノ結晶記憶要素を含むプログラム可能構造

記憶セルは、トレンチを画成する半導体基板、トレンチの内側を覆う底部誘電体、及び底部誘電体上の電荷格納層を有している。電荷格納層は複数の不連続な記憶要素(DSE)を含んでいる。制御ゲート及び頂部誘電体がDSEを覆っている。記憶セルはトレンチの下にソース/ドレイン領域を有している。DSEはシリコンナノ結晶であってもよく、制御ゲートはポリシリコンであってもよい。制御ゲートは半導体基板の上面の下方までリセス化され、最も上側のDSEは縦方向で制御ゲートの上面に揃えられている。記憶セルは、トレンチの側壁に隣接するシリコンナノ結晶に横方向で揃えられ、且つ最も上側のシリコンナノ結晶から基板の上面まで縦方向に延在している酸化物ギャップ構造を含んでいる。DSE群は少なくとも2つのプログラム可能な注入領域を含んでいる。  (もっと読む)

(もっと読む)

41 - 60 / 86

[ Back to top ]