Fターム[5F101BD32]の内容

不揮発性半導体メモリ (42,765) | 素子構造 (12,113) | アレイ (242) | 稠密アレイ構造 (233)

Fターム[5F101BD32]に分類される特許

61 - 80 / 233

不揮発性半導体記憶装置およびその製造方法

【課題】シリコンをエピタキシャル成長させて得られた単結晶シリコン層の結晶欠陥の部分にメモリセルを形成することなくメモリセルの積層を実現する不揮発性半導体記憶装置を提供する。

【解決手段】層間絶縁膜16上にシリコンをエピタキシャル成長させて得られた単結晶シリコン層200、204の結晶欠陥26bの部分にソース線コンタクトホールを形成する。これによって、結晶欠陥26bの部分に、接合リークにより特性の劣化したメモリセルを形成することなく、メモリセルを二層以上積層することができる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高集積化されたスプリットゲート型不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板1の表面に第1の柱状凸部2aと第2の柱状凸部2bが離間して形成され、第1、第2の柱状凸部2a,2bは、周辺部と先端部とにソースドレイン3,8の一方と他方とが形成され、周辺部と先端部との間の側壁の表面に、電荷蓄積膜4とメモリゲート線5とが積層された第1積層構造と、ゲート酸化膜6と制御ゲート線7とが積層された第2積層構造と、が形成されたスプリットゲート型の不揮発性メモリセルを、それぞれ含み、第1積層構造が第1、第2の柱状凸部2a,2bの間にも形成され、それによって、第1の柱状凸部2aと第2の柱状凸部2bとで、メモリゲート線5が共通に接続されている

(もっと読む)

不揮発性半導体記憶装置

【課題】チャネル界面付近の浅いエネルギー準位に捕獲された電荷を予め除去し、データ保持特性の良好な不揮発性半導体記憶装置を提供する。

【解決手段】メモリ部MUと、制御部CTUと、を備える不揮発性半導体記憶装置において、メモリ部は、第1方向に交互に積層された複数の電極膜WLと複数の電極間絶縁膜14とを有する積層構造体MLと、積層構造体MLを第1方向に貫通する半導体ピラーSPと、電極膜WLと半導体ピラーSPとの間に設けられた、内側絶縁膜42、記憶層及び外側絶縁膜と、半導体ピラーSPの一端と電気的に接続された配線と、を有す。制御部CTUは、消去動作の際に、配線を第1電位に設定しつつ、電極膜WLを第1電位よりも低い第2電位に設定する第1動作の後に、配線を第3電位に設定しつつ、電極膜WLを第3電位よりも高い第4電位に設定する第2動作を実施する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリホールの直径が均一な不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】シリコン基板10上にバックゲート電極13を形成し、バックゲート電極13の上面に凹部23を形成し、凹部23内に犠牲材を埋め込んだ後、絶縁膜14及び電極膜15を交互に積層して積層体11を形成する。次に、積層体11の中央部21にメモリホール24を形成し、その後、酸化処理を施す。これにより、メモリホール24の内面を起点として、電極膜15における絶縁膜14に接する部分が酸化され、その結果、中央部21において電極膜15が薄くなり、絶縁膜14が厚くなる。次に、積層体11の端部22において、電極膜15毎にステップ30を形成し、端部22を埋め込むように層間絶縁膜40を形成し、層間絶縁膜40中にステップ30に到達するようにプラグホール41を形成する。

(もっと読む)

ナノ線メモリ

【課題】単純な構造のナノ点を有するメモリを利用してマルチレベルを保存することができるメモリ素子を提供する。

【解決手段】ソース210及びソース210と対応するドレイン220と、ソース210とドレイン220との間を連結するように形成されているナノチャンネル230とを含み、ナノチャンネル230は、ソース210及びドレイン220の電圧によってソース210とドレイン220との間を電気的に連結するナノ線と、ナノ線上に吸着されて形成され、電荷を補集する複数のポテンシャルを有するナノ点とを含む。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】回路部の上部にメモリ部を形成し、回路部が高温にさらされても回路部の配線層やコンタクトが劣化しない不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板11と、メモリ部MUと、半導体基板とメモリ部との間の回路部CUと、を備える。メモリ部は、半導体基板の主面11aに垂直な第1方向に交互に積層された複数の電極膜WLと複数の絶縁膜14とを有する積層構造体MLと、積層構造体を第1方向に貫通する半導体ピラーSPと、電極膜と半導体ピラーとの交差部に対応して設けられた記憶部43と、を有す。回路部は、それぞれ第1、第2導電型のソース/ドレイン領域を有する第1、第2トランジスタ51n、51pと、シリサイドを含む第1配線W1と、ソース/ドレイン領域と同じ導電型のポリシリコンからなるコンタクトプラグC1、C2と、を有す。

(もっと読む)

半導体装置およびその製造方法

【課題】浮遊ゲート電極膜と制御ゲート電極膜との間に設ける電極間絶縁膜の絶縁特性をより一層改善することができる半導体装置およびその製造方法を提供する。

【解決手段】素子分離絶縁膜4の上面、浮遊ゲート電極膜6の側面及び浮遊ゲート電極膜6の上面に、シリコン窒化膜と同等以上の誘電率を有する高誘電率膜を含む複数層構造で構成された電極間絶縁膜7を形成し、この電極間絶縁膜7上に制御ゲート電極膜9を形成した半導体装置であって、浮遊ゲート電極膜6の上面と電極間絶縁膜7との間にシリコン酸化膜8を形成し、浮遊ゲート電極膜6の側面に電極間絶縁膜7の高誘電率膜を直接接触させるように構成した。

(もっと読む)

不揮発性半導体記憶装置

【課題】デポジッション膜を形成することなく、ゲートとコンタクトのショートを抑制する不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置1のコントロールゲート14を、フローティングゲート13側に位置する第1側面と、第1側面の反対に位置する第2側面と、コントロールゲート14の第1側面側の上部に形成されたシリサイド領域22と、コントロールゲート14の第2側面側の上部に形成された突出部8とを含むように構成する。そのサイドウォール絶縁膜21は、シリサイド領域22を覆うことなく突出部8の少なくとも一部を被覆する第1部分と、第1部分から連続的に設けられ、第2側面に接触して第2側面を被覆する第2部分とを含むものとする。

(もっと読む)

半導体装置

【課題】第1導電型の半導体層とトンネルウィンドウが対向する第2導電型の不純物拡散領域との高い接合耐圧を得ることができる、半導体装置を提供する。

【解決手段】各メモリセルにおいて、半導体基板2の表層部には、N型の第1不純物拡散領域3が形成されている。また、半導体基板2の表層部には、第1不純物拡散領域3に対して所定方向の一方側に、第1不純物拡散領域3と間隔を空けて、N型の第2不純物拡散領域4が形成されている。半導体基板2上には、第1絶縁膜6が形成されている。第1絶縁膜6には、第1厚膜部8が形成されており、第2不純物拡散領域4の全周縁は、第1厚膜部8の直下に位置している。

(もっと読む)

半導体装置とその製造方法

【課題】歩留まりと信頼性を高めるフラッシュメモリセルを備えた半導体装置とその製造方法を提供する。

【解決手段】半導体装置の製造方法は、シリコン基板1に素子分離絶縁膜6を形成する工程と、シリコン基板1の表面にトンネル絶縁膜を形成する工程と、素子分離絶縁膜6とトンネル絶縁膜の上に第1導電膜を形成する工程と、第1導電膜をパターニングして導電パターン13aにする工程と、導電パターン13aの表層部分をスパッタエッチングする工程と、導電パターン13aと素子分離絶縁膜6の上に中間絶縁膜16を形成する工程と、中間絶縁膜16の上に第2導電膜17を形成する工程と、導電パターン13a、中間絶縁膜16、及び第2導電膜17をパターニングすることによりフラッシュメモリセルFLを形成する工程とを有する。

(もっと読む)

不揮発性半導体記憶装置とその駆動方法および電子機器

【課題】周辺回路の増大を極力抑えつつ、データディスターブを改善する不揮発性半導体記憶装置を提供する。

【解決手段】第1ボディ領域100上に不純物拡散層104,124を、第1不純物拡散層104上に第2ボディ領域106を形成する。第1不純物拡散層104はメモリトランジスタMTのドレイン領域と選択トランジスタSTのソース領域、第1不純物拡散層124は選択トランジスタSTのドレイン領域をなす。第2ボディ領域106と第1不純物拡散層104に跨るように第2ボディ領域106上にメモリトランジスタMTのゲート部G_MTをMONOS構造で形成する。第1不純物拡散層104、第1ボディ領域100、第1不純物拡散層124に跨るように選択トランジスタSTのゲート部G_STをMOS型構造で形成する。両トランジスタMT,STは、バックゲートとなるボディ領域が電気的に分離される。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】ビット線コンタクト内の電気抵抗、およびビット線コンタクトとソース・ドレイン領域の接続部分の電気抵抗の小さい半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体記憶装置100は、素子分離領域3により区画された活性領域2を有する半導体基板1と、活性領域2上に形成され、直列接続されたスタックド・ゲート型の複数のメモリセルトランジスタと、活性領域2上に形成され、複数のメモリセルトランジスタの両端に接続された選択トランジスタと、活性領域2中の選択トランジスタに属するソース・ドレイン領域5に接続された、下部のチャネル幅方向の垂直断面の形状が裾引き形状であるビット線コンタクト8と、を有する。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】コンタクト抵抗の増大を防止できるようにする、記憶部と論理部とを混載する不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】半導体基板1の上にビット線コンタクト領域20と、ビット線コンタクト領域を含め、行方向に延伸する複数の第1のゲート絶縁膜11とを形成し、ビット線コンタクト領域20を挟んでビット線拡散層2を形成し、ビット線拡散層2及び第1のゲート絶縁膜11の上に導電膜4を形成し、導電膜4からビット線拡散層2と交差するコントロールゲート電極4aを形成し、少なくともビット線コンタクト領域20の第1のゲート絶縁膜11を除くと共に、ビット線コンタクト領域20に、その両側のビット線拡散層2同士を接続するように接続拡散層を形成する。コントロールゲート電極4aを形成する時に、ビット線コンタクト領域20の上及びその両側のビット線拡散層2の上にまたがるように導電膜4を残存させる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】MONOS型半導体記憶装置の電荷蓄積用のトラップ膜及びビット線拡散層を有する不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板101に形成され、それぞれ行方向に延伸する複数のビット線拡散層104と、半導体基板101上における互いに隣接する各ビット線拡散層104同士の間に形成され、それぞれが電荷トラップ膜102bを含む複数のONO膜102と、複数のビット線拡散層104の上にそれぞれ形成された複数のビット線絶縁膜105と、半導体基板101の上にそれぞれ複数のONO膜102及び複数のビット線絶縁膜105を覆うように形成され、各ビット線拡散層104と交差して列方向に延伸する複数のワード線106とを有している。ビット線絶縁膜105の膜厚はONO膜102の膜厚よりも小さく、且つビット線絶縁膜105の上面はONO膜102の上面と平行である。

(もっと読む)

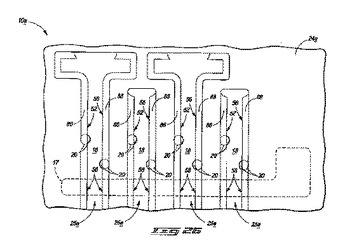

集積回路の製造において複数の導電線を形成する方法、導電線アレイを形成する方法、および集積回路

集積回路の製造において導電線対を形成する方法は、基板上に受けられるダマシン材料にトレンチを形成することを含み、導電性材料34a/35aが、そのダマシン材料を覆ってそしてトレンチ内へ蒸着されてそのトレンチを過充填する。その導電性材料は、少なくともダマシン材料へと戻すように除去されて、そのトレンチ内に残っている導電性材料の少なくともいくらかが残される。エッチングがトレンチ内で導電性材料を通って縦方向に処理されて、トレンチ内に少なくとも第1および第2の導電線の長さの大部分に沿って横断面図において互いにミラー像となる第1および第2の導電線が形成される。他の装いが考えられる。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセルを高集積度化することができるチャージトラップ型フラッシュ構造の不揮発性半導体記憶装置を提供する。

【解決手段】半導体記憶装置50は、接地線SUBLとしての半導体基板層1aの第1主面(表面)上に、素子分離層2、ソース電極3a、ソース電極3b、ドレイン電極4a、及びドレイン電極4bを柱状にエッチング開口した開口部5が互いに離間して複数設けられる。開口部5には、半導体基板層1b、積層膜6、及びゲート電極7が埋設され、開口部5の内側には半導体基板層1bが半導体基板層1aと接するように設けられる。半導体基板層1bの内側には、トンネル酸化膜、電荷蓄積膜、電流遮断膜から構成される積層膜6が設けられる。積層膜6の内側にはゲート電極7が埋設される。半導体基板層1bにはソース層8とドレイン層9が垂直方向に複数設けられ、チャネルが垂直方向に設けられるメモリトランジスタが積層形成される。

(もっと読む)

半導体装置の製造方法

【課題】不揮発性メモリを備える半導体装置において、不揮発性メモリを構成するメモリセルの加工精度を向上することができる技術を提供する。

【解決手段】ポリシリコン膜PF1とダミーゲート電極DMY1を覆うようにポリシリコン膜PF2を形成する。このとき、ポリシリコン膜PF2は、段差DIFおよびギャップ溝GAPの形状を反映して形成される。特に、ギャップ溝GAPを覆うポリシリコン膜PF2には凹部CONが形成される。続いて、ポリシリコン膜PF2上に反射防止膜BARCを形成する。このとき、流動性の高い反射防止膜BARCは、段差DIFの高い領域から低い領域に流出するが、凹部CONに充分な反射防止膜BARCが蓄積されているので、流出する反射防止膜BARCを補充するように凹部CONから反射防止膜BARCが供給される。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】メモリセル部のトランジスタのゲート構造と周辺回路部のトランジスタのゲート構造とが異なる半導体装置において、加工途中でメモリセル部の高さと周辺回路部の高さをほぼ揃える。

【解決手段】半導体基板1上に周辺回路部用のゲート絶縁膜10、12を形成する工程と、ゲート絶縁膜10、12上に周辺回路部用のポリシリコン膜11を形成する工程と、ポリシリコン膜11及びゲート絶縁膜10のうちのメモリセル部に対応する部分を除去する工程と、半導体基板1上にメモリセル部用のトンネル絶縁膜6、チャージトラップ膜7およびパッドシリコン酸化膜15を積層形成する工程と、パッドシリコン酸化膜15上にパッドアモルファスシリコン膜16を形成する工程と、パッドアモルファスシリコン膜16のうちの周辺回路部に対応する部分を除去する工程とを備え、パッドアモルファスシリコン膜16を除去したときに、メモリセル部の高さと周辺回路部の高さがほぼ等しくなるように、ポリシリコン膜11の膜厚を設定した。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリセルを3次元的に配置した、良質な構造を有する不揮発性半導体装置及びその製造方法を提供する。

【解決手段】基板100上にノンドープのアモルファスシリコン層とボロンを含むアモルファスシリコン層106とを交互に形成する工程と、アモルファスシリコン層をエッチングしてスリットを形成する工程と、スリット内に犠牲膜を形成する工程と、アモルファスシリコン層をエッチングしてホールを形成する工程と、ノンドープのアモルファスシリコン層をエッチングして、空隙を形成する工程と、空隙内及びホール内に層間絶縁膜107を形成する工程と、ホール内に形成された層間絶縁膜107をエッチングしてホール115を形成する工程と、ホール115内にブロック絶縁膜を形成する工程と、電荷蓄積絶縁膜を形成する工程と、トンネル絶縁膜を形成する工程と、半導体領域を形成する工程とを含む。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】中空円筒型の半導体ピラーに適用でき、高濃度で位置制御性の高いソースドレイン拡散層を低製造コストで実現する不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】第1方向に交互に積層された複数の絶縁膜14及び複数の電極膜WLを有する積層構造体MLと、積層構造体MLの上に積層された選択ゲート電極SG及び絶縁層16と、半導体ピラーSPと、芯部68と、第1導電層18と、を備える。半導体ピラーSPは、積層構造体ML、選択ゲート電極SG及び絶縁層16を第1方向に貫通し、第1方向に直交する平面で切断した時の断面が環状である。芯部68は、半導体ピラーSPの内側に埋め込まれ、絶縁層16の上面から後退している。第1導電層18は、芯部68の上に、芯部68に接触して設けられる。

(もっと読む)

61 - 80 / 233

[ Back to top ]