Fターム[5F101BD32]の内容

不揮発性半導体メモリ (42,765) | 素子構造 (12,113) | アレイ (242) | 稠密アレイ構造 (233)

Fターム[5F101BD32]に分類される特許

141 - 160 / 233

半導体装置の製造方法

【課題】分離した電荷蓄積層を有する半導体装置において、ゲート電極中央下にゲート絶縁膜を形成する際のゲート電極の倒れ込みを抑制する製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板10上に第1絶縁膜22とゲート電極24を形成する工程と、開口部46から第1絶縁膜を22除去してゲート電極中央下にゲート絶縁膜22を形成する工程と、フッ酸によるウエットエッチング法を用いて、ゲート電極24下に形成された第1絶縁膜22を除去し、ゲート電極24の両端下に、アンダーカット部が形成する工程と、第1絶縁膜22を除去したアンダーカット部にトンネル絶縁膜12と、ポリシリコン膜による電荷蓄積層14と、トップ絶縁膜16を形成する工程と、を有する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】消去ゲートとコントロールゲートとの間のシリサイド・ショートの発生確率を低減させる消去ゲートを備えた不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板1上に形成されたフローティングゲート3と、フローティングゲート3上に形成された消去ゲート10と、半導体基板表層のチャネル領域上にフローティングゲート3と並設され、フローティングゲート3及び消去ゲート10の一方の側面に形成されたコントロールゲート22と、消去ゲート10の上面に形成された第1シリサイド膜27と、コントロールゲート22の上面に形成された第2シリサイド膜26と、を備え、コントロールゲート22の上面の高さは、消去ゲート10の上面の高さと同じ若しくはそれよりも下方に位置することを特徴とする。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】高速化を図ることのできる不揮発性の半導体記憶装置と、その製造方法を提供する。

【解決手段】ウェル領域3の表面上に制御ゲート絶縁膜4を介在させて制御ゲート電極5aが形成されている。制御ゲート電極5aの一方の側面上にONO膜6を介在させてメモリゲート電極7aが形成されている。そのウェル領域には、ドレイン領域Dとしての低濃度不純物領域10aおよび高濃度不純物領域12aと、ソース領域Sとしての低濃度不純物領域10bおよび高濃度不純物領域12bとが形成されている。その制御ゲート電極5aおよびメモリゲート電極7aを覆うように、引張り応力の比較的強い膜として、シリコン窒化膜14が形成されている。さらに、そのシリコン窒化膜14を覆うように層間絶縁膜20が形成されている。これにより、チャネル領域に引張り応力が作用して電子の移動度が大きくなり、トランジスタの電流を増加させることができる。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】下から順に、制御ゲート電極、ゲート間絶縁膜、浮遊ゲート電極、トンネル絶縁膜の各層を形成した構造において、トンネル絶縁膜の膜質を向上できるようにした不揮発性半導体装置の製造方法を提供する。

【解決手段】シリコン基板1上にシリコン酸化膜2を介して、制御ゲート電極CGとして機能する導電膜3、高誘電体膜を含有した導電膜間絶縁膜4、リン、砒素またはボロンによる不純物を添加した多結晶シリコンから構成され、浮遊ゲート電極FGとして機能する導電膜5を順に形成する。その後、400℃以上600℃以下の温度範囲内の低温条件下でプラズマ酸化処理によって導電膜5上にシリコン酸化膜7を形成する。シリコン酸化膜7および8上には、シリコン層9が形成されている。ソース/ドレイン領域が積層ゲート電極6のY方向両脇で且つシリコン酸化膜8の上側に形成されている。

(もっと読む)

逆転構造の不揮発性メモリ素子、そのスタックモジュール及びその製造方法

【課題】逆転構造の不揮発性メモリ素子、そのスタックモジュール及びその製造方法を提供する。

【解決手段】少なくとも一つの底ゲート電極は、基板上に提供され、少なくとも一層の電荷保存層は、少なくとも一つの底ゲート電極上に提供され、少なくとも一層の半導体チャンネル層は、少なくとも一層の電荷保存層上に提供される不揮発性メモリ素子である。少なくとも一層の半導体チャンネル層の両側に電気的にそれぞれ連結された少なくとも一つのソース電極及び少なくとも一つのドレイン電極をさらに備える。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】電荷保持膜の損傷が抑制され、良好な電荷捕獲能力を有し、高い信頼性を有する不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板内1を列方向に延伸する第1の拡散層ビット線2aと、第1の埋め込み絶縁膜3aと、第1の電荷保持膜4aと、半導体基板1の上方を行方向に延伸するワード線5とを有するメモリセル領域と、メモリセル領域と列方向に隣接し、注入拡散層7を有するコンタクト領域とを備えている。メモリセル領域とコンタクト領域の境界領域では、ワード線5と平行に延伸するダミーワード線12と、第2の電荷保持膜4bと、第2の拡散層ビット線2bと、ダミーワード線12及び第2の電荷保持膜4bの側面に接する第2の埋め込み絶縁膜3bとが備えられている。

(もっと読む)

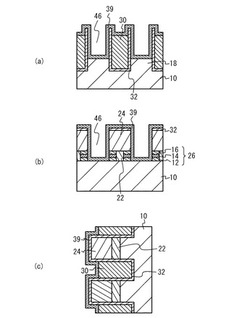

半導体装置及びその製造方法

【課題】メモリセルの高密度化が容易な半導体装置及びその製造方法を提供すること。

【解決手段】本発明は、半導体基板10内に設けられた溝部30と、溝部30の両側面に設けられた絶縁膜からなる電荷蓄積層20と、溝部30内に電荷蓄積層を介し埋め込まれたワード線22と、溝部30の両側の半導体基板10内に設けられたソース・ドレイン領域12と、溝部30の両側に設けられたソース・ドレイン領域12のうち一方SD13に接続する第1配線層ML1と、ソース・ドレイン領域12のうち他方SD12に接続する第2配線層ML2と、を具備する半導体装置及びその製造方法である。

(もっと読む)

MOS型半導体メモリ装置

【課題】優れたデータ保持特性と、高速でのデータ書換え性能と、低消費電力での動作性能と、高い信頼性と、を同時に兼ね備えた不揮発性MOS型半導体メモリ装置を提供する。

【解決手段】MOS型半導体メモリ装置601は、大きなバンドギャップを持つ第1の絶縁膜111および第5の絶縁膜と、最も小さなバンドギャップを持つ第3の絶縁膜113との間に、両者の中間の大きさのバンドギャップを持つ第2の絶縁膜112および第4の絶縁膜114を備えている。このようなエネルギーバンド構造を有することにより、データ書き込み時には第1の絶縁膜111を介した電荷の移動が起こりやすく、書き込み動作速度を高速化することが可能で、かつ絶縁膜積層体に電荷を注入するために必要な書き込み電圧を小さく抑えることができる。

(もっと読む)

不揮発性半導体記憶装置

【課題】不揮発性半導体記憶装置において、選択メモリセルのドレイン側で発生した2次電子が隣接する非選択メモリセルへ到達することを抑制し、非選択メモリセルへ2次電子が誤書き込みされることを防止する。

【解決手段】不揮発性半導体記憶装置は、ビット線方向に延伸するように形成され、ソース・ドレインとして機能する一対の拡散ビット線101と、一対の拡散ビット線101間に形成されたゲート絶縁膜105と、ゲート絶縁膜105上にワード線方向に延伸するように形成され、ゲート電極として機能するワード線102とを備える。拡散ビット線101の下方に拡散ビット線101から離間するように形成され、拡散ビット線101の導電型と同一導電型の高濃度埋込層103を備える。

高濃度埋込層103は引き出し電極に接続され、独立に電位制御可能であり、これに正電位を印加することで、発生した2次電子が高濃度埋込層103に捕捉される。

(もっと読む)

半導体装置の作製方法

【課題】大面積基板に、高性能な半導体素子、及び集積回路を高スループットで生産性よく作製することを目的とする。

【解決手段】単結晶半導体基板(ボンドウエハー)より単結晶半導体膜を転置する際、単結晶半導体基板を選択的にエッチング(溝加工ともいう)し、作製する半導体素子の大きさに複数に分割された複数の単結晶半導体層を、異種基板(ベース基板)に転置する。従って、ベース基板には、複数の島状の単結晶半導体層(SOI層)を形成することができる。

(もっと読む)

不揮発性半導体記憶素子

【課題】データ消去動作によりメモリセルにホールトラップやゲート酸化膜の欠陥を生じさせにくく、素子特性の変動を抑制して動作の安定化を図った不揮発性半導体記憶素子を提供する。

【解決手段】単層のポリシリコン層を有する断面構造を有する不揮発性半導体記憶素子は、互いに絶縁分離されるメモリセル部a、データ消去部b、及びコントロールゲート部cを含む。メモリセル部a及びデータ消去部bはMOSトランジスタで構成され、コントロールゲート部cは、MOSキャパシタで構成される。これら3つの部位は、前記単一のポリシリコン層で構成される共通のフローティングゲートを有する。フローティングゲート6cの電位を制御してメモリセルaをオンにすることにより、フローティングゲート6aにデータを書き込み、フローティングゲート6cの電位を制御してデータ消去部bをオンにすることにより、フローティングゲート6bを通じてデータを消去する。

(もっと読む)

半導体記憶装置の製造方法

【課題】信頼性に優れた半導体記憶装置の製造方法を提供する。

【解決手段】半導体記憶装置の製造方法は、凹凸部を有する半導体基板10の凹部に素子分離領域12を形成する工程と、凹凸部を有する半導体基板10の凸部、及び素子分離領域12を覆うようにゲート電極材からなる層を形成する工程と、ゲート電極材からなる層の表面に形成するマスクを、凸部の上面から前記マスクの表面までの高さが記素子分離領域12の表面から凸部の上面までの高さより高くなるように形成し、ゲート電極材からなる層をパターニングしてゲート電極14を形成する工程と、ゲート電極14の側面であり、凹凸部を有する半導体基板の凸部と接する面の少なくとも一方に電荷蓄積層16を形成する工程と、電荷蓄積層16の少なくとも一部にサイドウォール34を形成する工程と、を含む。

(もっと読む)

半導体記憶装置の製造方法

【課題】フローティングゲートを有するスプリットゲート型不揮発性半導体記憶装置において、コントロールゲートの側壁に、シリサイド・ショートを防止できるのに十分な高さの側壁絶縁膜を形成することができる製造方法を提供する。

【解決手段】半導体記憶装置の製造方法は、半導体基板1に形成したPウエル4上にゲート絶縁膜2を介してフローティングゲート用の導電体層16を形成する工程と、導電体層16上にTEOS−NSG等の第1のシリコン酸化膜から構成される第1のスペーサ10と、第1のスペーサ10と隣接し第1のシリコン酸化膜10よりもエッチングレートが遅い第2の高温シリコン酸化膜から構成される第2のスペーサ11と、を形成する工程と、第1及び第2のスペーサ10,11をマスクにして導電体層16を選択的に除去する工程と、第1のスペーサ10を除去して導電体層16の一部を露出させる工程と、を含む。

(もっと読む)

不揮発性半導体メモリ及びその製造方法

【課題】従来のMONOSは、高い誘電率の物質をブロック層として用いると、電子障壁が足りず、消去時にメモリ電極側からの電子注入書き込みが発生してしまう。

【解決手段】半導体基板にチャネル領域となる間隔を空けて設けられるソース領域及びドレイン領域と、チャネル領域上に順次形成される第1の絶縁層と、電荷蓄積層と、第2の絶縁層(ブロック層)と、制御電極とを有し、第2の絶縁層は、第1の絶縁層よりも十分に誘電率の高い物質を母体材料中に高価数物質が適量添加されて形成され、電子をトラップできる局在状態によりブロック層中に多量の負電荷を蓄積でき、ブロック層の高誘電率と高電子障壁を両立する不揮発性半導体メモリである。

(もっと読む)

不揮発性半導体記憶装置のメモリセル

【課題】駆動電流を増加させることにより、読み取り精度を向上させることができる不揮発性半導体記憶装置のメモリセルを提供する。

【解決手段】ゲート酸化膜13と、ゲート酸化膜13上に形成されたゲート電極14と、ゲート酸化膜13の下方に形成されたチャンネル領域と、チャンネル領域の両側に形成された一対のドレイン・ソース領域と、チャンネル領域およびドレイン・ソース領域を挟む一対の絶縁分離領域20と、を含み、絶縁分離領域20の少なくとも一方においてチャンネル領域およびドレイン・ソース領域に沿って延在する窒化膜等の電荷蓄積層21が設けられている。荷蓄積層21をドレイン・ソース領域およびチャンネル領域と近接して設けることによって、チャンネル領域内に発生したホットエレクトロンは、電荷蓄積層21内部に注入され保持される。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】浮遊ゲート電極間の制御ゲート電極の空乏化を大幅に抑制できて、読み出しエラーが起こりにくい多値型を含むNOR型のフラッシュメモリ等の不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】複数のメモリセル4を、互いに一方向に間隔をおくように配置する。制御ゲート電極2のONO膜22の側面に上記一方向に重なる部分24を、不純物がドープされた多結晶シリコンで形成する。制御ゲート電極2の上記一方向に重なる部分24において、多結晶シリコンの不純物濃度を、1020/cm3以上かつ1021/cm3以下に設定することで、浮遊ゲート電極10間の制御ゲート電極2の空乏化を大幅に抑制でき、隣接セルの浮遊ゲート電極10間の容量結合による閾値変動を急激に小さくする事ができ、隣接セルの閾値の干渉を受けないようにできる。

(もっと読む)

不揮発性メモリ装置及びその製造方法

【課題】ビットラインコンタクトとゲートパターンの上部との電気的短絡を防止することができる不揮発性メモリ装置及びその製造方法を提供する。

【解決手段】半導体基板上に素子分離膜を形成するステップと、半導体基板上に、浮遊ゲート電極と、浮遊ゲート電極と素子分離膜上に延長された制御ゲートラインとを含む不揮発性メモリセルトランジスタのゲートパターンを形成するステップと、マスクパターンを用いて少なくともゲートパターンの第1側壁の第1部分を覆い、制御ゲートラインの上部角部を露出させるステップと、マスクパターンをエッチングマスクとして用い、素子分離膜を第1エッチング率で選択的にエッチングして素子分離膜内に少なくとも部分的な開口部を規定し、同時に制御ゲートラインの上部角部を第1エッチング速度よりエッチング速度が低い第2エッチング率でエッチバックするステップとを有する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】拡散層の熱拡散が生じにくく且つワード線の微細加工が容易な不揮発性半導体記憶装置を実現できるようにする。

【解決手段】不揮発性半導体記憶装置は、半導体基板11に行列状に配置された複数のメモリセル部11と、列方向に延びる拡散層からなる複数のビット線12と、埋め込み絶縁膜16と、埋め込み絶縁膜16の上に形成され、行方向に延びる複数のワード線13とを備えている。各メモリセル部11は、選択トランジスタ21と、選択トランジスタ21の両側方にそれぞれ形成された2つのメモリトランジスタ21、23を有している。メモリトランジスタ21、23は、それぞれ、順次形成された側方ゲート絶縁膜21A、23A及び中央ゲート電極22Bと絶縁された側方ゲート電極21B、23Bを有する。

(もっと読む)

フラッシュメモリ素子及びその製造方法

【課題】高額な露光装備を要せずとも、既存の露光設備を利用することによって誘電体膜コンタクトホールを微細化して形成することができるフラッシュメモリ素子とその製造方法を提供する。

【解決手段】半導体基板100上に第1導電膜104のパターンと素子分離膜106を形成し、誘電体膜108を形成する。誘電体膜108上には第1開口部を有するフォトレジストパターン110を形成し、第1開口部よりもサイズが小さい第2開口部となるように、フォトレジストパターン110を溶解し、開口部110a方向にフォトレジストの一部が流れるようにする原理を活用することで、開口部110aのサイズを小さくするようにする。フォトレジストパターン110に沿って誘電体膜108をパターニングして誘電体膜コンタクトホールを形成し、フォトレジストパターンを除去する。誘電体膜108と第1導電膜104上に第2導電膜を形成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】動作速度の高速化を実現することができる不揮発性半導体記憶装置を提供する。

【解決手段】NAND型フラッシュメモリ1において、データ線50の延在方向に隣接する複数個のメモリセルユニット20の第1の選択トランジスタ22の各々の制御電極を一体化し第1の選択信号線71を構成し、第2の選択トランジスタ23の各々の制御電極を一体化し第2の選択信号線72を構成する。第1の選択信号線71に対して、第2の選択信号線は、データ線50の延在方向に半配列ピッチ分ずれている。

(もっと読む)

141 - 160 / 233

[ Back to top ]