Fターム[5F101BD32]の内容

不揮発性半導体メモリ (42,765) | 素子構造 (12,113) | アレイ (242) | 稠密アレイ構造 (233)

Fターム[5F101BD32]に分類される特許

221 - 233 / 233

半導体装置及び半導体記憶装置の製造方法

【課題】 狭小ピッチで配線パターンを形成し、該配線パターンに接続するプラグを高い裕度で形成する。

【解決手段】 導電膜上に第1パターン11を形成し、該第1パターン11をトリムエッチングで細らせる。微細な第1パターン11aの周囲に自己整合的に閉ループの第2パターン12を形成する。第2パターン12を一部で分断して第3パターン12aを形成する。第3パターン12aをマスクとして導電膜をエッチングすることにより、配線パターン13を形成する。配線パターン13を層間絶縁膜で覆った後、配線パターン13の屈曲した端部が露出するように開口14を層間絶縁膜内に形成する。開口14内に導電膜を埋め込みプラグを形成する。

(もっと読む)

半導体装置

【課題】 微細化できるとともに、配線抵抗を低くすることができる半導体装置を得る。

【解決手段】 半導体基板上にゲート絶縁膜を介して行列状に配置されたフローティングゲートと、フローティングゲート上に行方向に形成された制御ゲートと、半導体基板のフローティングゲート間の領域に列方向に形成されたトレンチと、トレンチを埋め込む絶縁膜と、絶縁膜中に列方向に形成された補助ゲートとを有し、補助ゲートにバイアスを印加することにより補助ゲートの近傍の半導体基板中に生じる反転層を配線として用いる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】 製造が容易であり、かつ動作の信頼性が高い半導体記憶装置を提供する。

【解決手段】 セルトランジスタ11は、p型シリコン基板、コントロールゲートCG、及び電気的に孤立した一対のフローティングゲートFG1,FG2からなる。シリコン基板には、コラム方向に延在した帯状の凸部13が形成されており、ソース又はドレインとして機能する一対の帯状のn型拡散領域14a,14bが凸部13を挟む表層に形成されている。コントロールゲートCGは、凸部13及びフローティングゲートFG1,FG2の上に絶縁膜を介して形成され、帯状にロウ方向に延在している。コラム方向に関するフローティングゲートFG1,FG2の幅W1はコントロールゲートCGの幅W2より大きい。フローティングゲートFG1,FG2及びコントロールゲートCGは、技術的課題のあるコラム方向におけるセルフアラインプロセスを用いずに簡単に形成することができる。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の書込方法、読出方法、消去方法

【課題】pチャネルMONOSメモリセルにおいて、データ書込時のデータ転送レートの高速化を実現する。

【解決手段】ビットラインをGND〜VCCで動作させるために、プログラム時にセルウェルに4Vのバックゲート電圧を印加する。プログラムモードとベリファイモードとの切り換えを高速化するために、ベリファイも4Vのバックゲート電圧が印加されたままの状態で行う。このため、ベリファイ時にはワードライン(ゲート)に−5Vの読出モード時よりも大きい(絶対値)電圧を印加する。

(もっと読む)

半導体記憶装置及び電子機器

【課題】 リードディスターブによるリファレンスセルの特性変動を防止する。

【解決手段】 メモリセル27m及びリファレンスセル27rは、共に、複合ゲート絶縁膜8の第3の絶縁膜3に、電荷または分極を保持する機能を有する2つの記憶領域を備える。メモリセル27mは、2つの記憶領域27mr、27mlにおいて、夫々独立した情報の記憶及び読出しが可能である。一方、リファレンスセル27rは、片側の記憶領域に記憶された情報のみがセンスアンプ22で参照される。

(もっと読む)

マルチレベルの仮想接地メモリのための読出方法

この発明は、両面ONOフラッシュメモリセル(500)におけるビットのレベルを決定するための技術(800)に関する。この場合、両面ONOフラッシュメモリセルのビットの各々は複数のレベル(540、542、544)にプログラミング可能である。この発明の1つ以上の局面は、1つのビット上の電荷のレベルが相補ビット妨害として公知である他のビットに及ぼす恐れのある影響を考慮に入れている。相互コンダクタンスとして公知の測定基準が、より高い解像度および精度をもたらすようビットレベルを決定する際に用いられる。この態様では、この発明の1つ以上の局面に従ったビットレベルの決定により、偽のまたは誤った読出が軽減される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体基板主面上の段差に起因するフローティングゲート材のエッチング不足による残渣の発生を防止する。

【解決手段】 半導体基板主面上にアシストゲート及びキャップ絶縁膜を積層した半導体装置において、前記アシストゲートのゲート長よりも小さな長さで前記キャップ絶縁膜を形成し、前記半導体基板主面上から前記アシストゲート及びキャップ絶縁膜の側面にわたってフローティングゲートを形成する。また、その製造方法では、前記アシストゲートのゲート長よりも小さな長さで前記キャップ絶縁膜を形成する工程と、前記半導体基板主面上から前記アシストゲート及びキャップ絶縁膜の側面にわたってフローティングゲートを形成する工程とを有する。

(もっと読む)

縦型スプリット・ゲート不揮発性メモリ・セルおよび製造方法

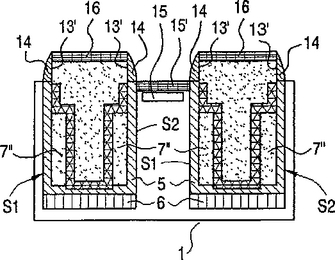

半導体基板上に、少なくとも1つのビットを記憶する縦型スプリット・ゲート不揮発性メモリ・セルを備え、基板上に、トレンチと、第1の活性領域と、第2の活性領域と、トレンチの側壁に沿って延びるチャネル領域とを含み、このトレンチは、第1の方向に延びる長さと、それに垂直な第2の方向に延びる幅を有し、トンネル酸化物によって側壁が覆われており、少なくとも1つの浮遊ゲートおよび制御ゲートのゲート・スタックを含み、制御ゲートがトレンチの底部まで延び、第1の浮遊ゲートが、制御ゲートと共に第1のスタックを形成するようにトレンチの左壁に位置するとともに、第2の浮遊ゲートが、制御ゲートと共に第2のスタックを形成するようにトレンチの右壁に位置する半導体デバイス。  (もっと読む)

(もっと読む)

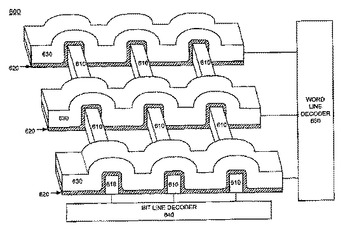

密集したメモリゲートを有するNANDフラッシュメモリ及び製作方法

【課題】 半導体メモリ素子、NANDフラッシュメモリとその製作方法を提供する。

【解決手段】 メモリゲート及び電荷蓄積層を有するセルが密集し、隣接セル内のメモリゲートが互いに部分的に重なるか又は互いに自己整列するNANDフラッシュメモリセルアレイ及び製造方法。メモリセルは、ビット線拡散部と共通ソース拡散部の間で列状に配置され、電荷蓄積層は、セル内のメモリゲートの下に位置決めされる。プログラミングは、負電荷を電荷蓄積ゲートに蓄積させるためにシリコン基板から電荷蓄積ゲートまでのホットエレクトロン注入、又は正電荷を電荷蓄積ゲートに蓄積させるためにシリコン基板から電荷蓄積ゲートまでのホットホール注入により行われる。消去は、プログラミング方法により電荷蓄積ゲートからシリコン基板まで又はその逆のチャンネルトンネリングにより行われる。

(もっと読む)

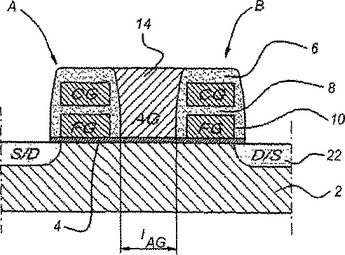

自己整合型の2ビット「ダブル・ポリCMP」フラッシュ・メモリ・セル

第1の浮遊ゲート・スタック(A)と、第2の浮遊ゲート・スタック(B)と、中間アクセス・ゲート(AG)とを含むメモリ・セルの製作。浮遊ゲート・スタック(A、B)は、第1のゲート酸化物(4)と、浮遊ゲート(FG)と、制御ゲート(CG;CGl、CGu)と、ポリ間誘電体層(8)と、キャッピング層(6)と、側壁スペーサ(10)とを含む。メモリ・セルはさらに、ソースおよびドレイン接触部(22)を含む。このメモリ・セルの製作は、浮遊ゲート・スタックを等しい高さにするために同じ処理工程で画定すること、ポリSi層(12)を浮遊ゲート・スタックの高さよりも大きな厚みで浮遊ゲートを覆って堆積させること、ポリSi層(12)を平坦化すること、浮遊ゲート・スタック間のポリSi層上にアクセス・ゲート・マスクを使用するマスキング工程およびポリSiエッチング工程によって、平坦化されたポリSi層(14)内に中間アクセス・ゲート(AG)を画定することを含む。  (もっと読む)

(もっと読む)

電荷トラップ不揮発性メモリおよびこれを作動させるための方法

【課題】容易に製造され、高密度適用をサポートする不揮発性メモリに対するメモリ技術を提供すること。

【解決手段】マルチゲートメモリセルが、半導体本体と、この半導体本体に並列配置された複数ゲートとを備える。半導体本体の電荷保存構造が、複数ゲートのゲート下部に電荷トラップ場所を含む。列内の第1ゲートおよび最終ゲート近傍の半導体本体にソース・ドレーンバイアス電圧を導通するための回路と、複数ゲートにゲートバイアス電圧を導通するための回路とが含まれる。マルチゲートメモリセルは、ゲートの一部、または全ゲート間の電荷保存場所で、列内の複数ゲート下部に連続マルチゲートチャネル領域を含む。

(もっと読む)

ラテラルサイリスタ及びトラッピング層を有するシリコン‐オン‐インシュレータ読み取り‐書き込み不揮発性メモリ

改善した、サイリスタに基づくメモリセルを提供する。一例では、シリコン‐オン‐インシュレータ(SOI)技術を用いて、セル(10)をフローティング基板内に形成する。セルには、第2ワードラインによりゲート駆動されるとともに完全にフローティング基板内に形成されたラテラルサイリスタ(20)を有するのが好ましい。このサイリスタのカソードは、アクセストランジスタ(18)のソースをも有し、このアクセストランジスタのドレインは装置のビットラインに接続されており、このアクセストランジスタは第1ワードライン(14)によりゲート駆動される。フローティング基板内にはトラッピング層が形成され、セルに書き込みを行う場合、パルスを加えて、論理状態“1”に対し正孔をトラッピング層にトラッピングさせ、論理状態“0”に対し電子をトラッピング層にトラッピングさせる。トラッピング層に電荷をトラッピングさせることにより、記憶されたデータ状態に追加の余裕度を加え、これらデータ状態の劣化を回避し、セルを不揮発性とする。  (もっと読む)

(もっと読む)

不揮発性メモリデバイス

不揮発性メモリデバイス(100)は、基板(110)、絶縁層(120)、フィン(210)、複数の誘電層(310〜330)及び制御ゲート(510/520)を備える。絶縁層(120)は、基板(110)上に形成され、フィン(210)は、絶縁層(120)上に形成される。誘電層(310〜330)は、このフィン(210)を覆うように形成され、制御ゲート(510/520)は、誘電層(310〜330)上に形成される。誘電層(310〜330)は、メモリデバイス(100)の電荷格納構造として機能する酸化物−窒化物−酸化物層を備える。  (もっと読む)

(もっと読む)

221 - 233 / 233

[ Back to top ]