Fターム[5F102GB04]の内容

接合型電界効果トランジスタ (42,929) | 主電流経路 (2,759) | 基板表面に垂直(縦型FET) (311)

Fターム[5F102GB04]の下位に属するFターム

メサ側面を流れるもの (36)

埋込ドレイン、ソース(基板表面取出し) (8)

Fターム[5F102GB04]に分類される特許

141 - 160 / 267

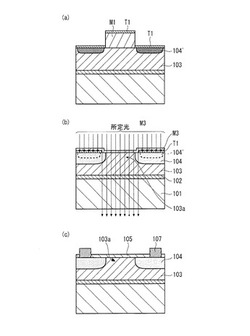

半導体装置の製造方法

【課題】デバイスの性能や信頼性を低下させることなく、注入した不純物を熱処理することができる半導体装置の製造方法を提供する。

【解決手段】下地層であるpGaN層103に形成された注入領域104’上に、GaNのバンドギャップエネルギーよりも小さいバンドギャップエネルギーを有する物質よりなる光吸収膜T1を形成し、この状態で基板101上面から赤外光や赤色光など、pGaN層103のバンドギャップエネルギーよりも小さいエネルギーの所定光を用いてアニールを行う。pGaN層103と比較して光吸収膜T1の方がアニールで使用される光の吸収係数が大きいため、光吸収膜T1直下もしくは近傍の領域(注入領域104’)を選択的に熱処理することが可能となる。

(もっと読む)

スイッチング回路

【課題】、接合型電界効果トランジスタ(JFET)の高温動作時のオン抵抗を低減して、高温時の動作特性を改善すること。

【解決手段】出力切替回路34は、温度検出装置33によって検出された温度が所定の閾値温度以上であるとき、第2の駆動回路32に出力切替指示を与える。これにより、第2の駆動回路は、MOSFET35を駆動して、JFET10に立ち上がり電圧(順方向降下電圧)VF以上のゲート電圧VGSが印加され、JFETはバイポーラ動作される。これにより、高温時のJFET10のオン抵抗の増加を抑制できる。

(もっと読む)

III族窒化物半導体装置とその製造方法

【課題】 縦型のIII族窒化物半導体の製造過程において、半導体構造の表面を平坦化する処理を利用することができるとともに、その後の工程で電極等を形成する際に半導体構造に対して高い精度で位置合わせできる製造方法を提供する。

【解決手段】 n型の窒化ガリウム基板2の表面の一部にアライメントマーク4を形成する。次に、窒化ガリウム基板2の表面とアライメントマーク4を覆うようにn型の第1の窒化ガリウム層6を結晶成長させる。次に、第1の窒化ガリウム層6の一部をアライメントマーク4に達しない深さまでエッチングする。次に、第1の窒化ガリウム層6の表面にp型の第2の窒化ガリウム層8を形成する。次に、第1の窒化ガリウム層6の凸部6aが露出するまで表面を平坦化する。第1の窒化ガリウム層6の表面を平坦化した後の工程でも、アライメントマークを認識することができる。

(もっと読む)

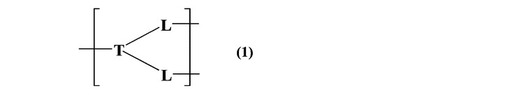

分岐型化合物、これを用いた有機薄膜及び有機薄膜素子

【課題】電荷輸送性に優れる両極性の有機半導体として利用可能な分岐型化合物の提供。

【解決手段】コア部と、該コア部に結合した少なくとも1つの側鎖部と、末端と、から構成される分岐型化合物であって、上記側鎖部の少なくとも1つは、下記一般式(1)で表される繰返し単位が1又は2以上繰り返しており(但し、コア部と結合する前記繰返し単位においては、Tがコア部に結合しており、2以上繰り返す前記繰返し単位においては、LがTに結合している。)、Lは、共役形成単位が複数連結して構成され、上記共役形成単位として少なくとも一つのチエニレン単位を含み、Lの末端(Tと結合していない側のLの末端)に存在する基は、少なくとも2つがアクセプター性の基である、分岐型化合物。

(式中、Lは置換基を有していてもよい2価の有機基を示し、Tは置換基を有していてもよい3価の有機基を示す。)

(もっと読む)

多環縮環化合物、多環縮環重合体及びこれらを含む有機薄膜

【課題】高い電荷輸送性と、溶媒への溶解性に優れる多環縮環重合体を提供する。

【解決手段】式(1)及び又は式(2)の構造単位を有する多環縮環重合体。

[式中、X1及びX2は、酸素原子、硫黄原子又はセレン原子を示す。]

(もっと読む)

半導体装置の製造方法

【課題】ドライエッチングで加工したp型の窒化物半導体の表面に低コンタクト抵抗のオーミック電極を形成する。

【解決手段】 半導体装置の製造方法は、窒化物半導体のp型領域をドライエッチングによって露出させる工程と、ドライエッチングで露出させたp型領域の表面にマグネシウムを含む被覆層を形成する被覆層形成工程と、被覆層が形成されている窒化物半導体を加熱処理するアニール工程と、被覆層を形成したp型領域の表面に、オーミック電極を形成する電極形成工程を備える。

(もっと読む)

III族窒化物半導体を有する半導体素子

【課題】III族窒化物半導体を有する半導体素子の耐圧を高くすること。

【解決手段】半導体素子は、AlGaNで構成された第1層32と、GaNで構成された第2層42と、ゲート電極34と、ソース電極38と、ドレイン電極28を有する。第1層32は、ゲート電極34と第2層42の間に形成された領域32aを有する。第1層32と第2層42の境界部24付近にチャネルが形成される。第2層42の導電型はp型であり、p型不純物であるMgがドーピングされている。第2層42は、ソース電極38に接している。

(もっと読む)

チップ内隣接構成デュアル静電誘導トランジスタ及びこれを用いたオーディオ用パワーアンプ回路

【課題】解決しようとする課題は、差動増幅器の入力段の対構成の差動トランジスタに最適な特性の揃ったディュアル静電誘導トランジスタを提供して、トランジスタ製造上の選別を容易にし、対形成不良を少なくし、回路製作上の調整作業を容易にすることである。

【解決手段】本発明では、半導体の1ウェーハ内の隣同士に隣接して、対構成の同一導電型、同一サイズの静電誘導トランジスタを構成して、差動増幅器の入力段用には、1チップとして組立し提供したものである。

(もっと読む)

電界効果トランジスタ

実施の形態に係る自己修復型電界効果トランジスタ(FET)装置は、各々がヒューズリンクを有する複数のFETセルを含む。ヒューズリンクは、対応するセルにおける高電流イベント時に飛ぶように調節される。 (もっと読む)

有機電子デバイス及びその作製方法

【課題】高い移動度を有し光起電力を利用する有機電子デバイス、該デバイスを容易なプロセスで作製する方法を提供する。

【解決手段】従来とは異なる特定の環状構造のビシクロ化合物を溶媒に溶解した溶液を基板上に塗布することにより膜を製膜し、次いで加熱等の外部作用を加えることで、該ビシクロ化合物からエチレン誘導体を脱離させることにより基板上で変換された化合物を有機半導体として用いてなる光起電力を利用する有機電子デバイス、及びその作製方法。

(もっと読む)

半導体装置及びその製造方法

【課題】製造が容易で、超高周波数、高速特性、低雑音性のノーマリオフ型のHEMT半導体装置及び製造方法を提供する。

【解決手段】第1の窒化物半導体からなる第1の層130と、該層の上に設けられ、窒化物半導体からなる第2の層140と、前記第1の層130と前記第2の層140との界面のうち、前記第1の層130のc軸210に対して平行な第1の領域250において、前記第2の層140の上に設けられたゲート電極150と前記c軸210に対して非平行な第2の領域260における前記第2の層140の上、及び、ソース電極160と、前記第1の層130と前記第2の層140との前記界面のうち、前記c軸210に対して非平行な第3の領域270における前記第2の層140の上、及び、前記第3の領域270の端部のいずれかに設けられたドレイン電極170と、を備えた半導体装置。

(もっと読む)

GaN系電界効果トランジスタ

【課題】簡易な製造工程によって形成可能なノーマリーオフ型のGaN系FETを提供すること。

【解決手段】本発明においては、ソース電極S直下およびドレイン電極D直下にそれぞれn−AlGaN層16を形成し、さらにn−AlGaN層16の間に位置するチャネル層であるp−GaN層14上に形成される絶縁膜17の上にゲート電極Gを形成することによって、ソース電極Sおよびドレイン電極Dとn−AlGaN層16との接触抵抗を低下させたノーマリーオフ型のGaN系のFET1を実現することができる。

(もっと読む)

窒化物半導体素子および窒化物半導体素子の製造方法

【課題】オン抵抗が低減された窒化物半導体素子およびその製造方法を提供すること。

【解決手段】この窒化物半導体素子は、n型層3、p型層4およびn型層5を有する窒化物半導体積層構造部2を備えている。窒化物半導体積層構造部2には、トレンチ6が形成されている。トレンチ6の壁面7の全域を覆うように、n型チャネル層8が形成されている。トレンチ6において、n型チャネル層8の内側には、p型不純物を含むGaNからなるp型ゲート層9が埋設されており、p型ゲート層9の最表面15には、ゲート電極10が形成されている。また、n型層5の最表面16には、ソース電極11が形成され、基板1の他方面には、ドレイン電極12が接触形成されている。

(もっと読む)

半導体素子の製造方法

【課題】III 族窒化物半導体からなる半導体装置の製造方法において、p型のIII 族窒化物半導体の正孔濃度を減少しないようにすること。

【解決手段】III 族窒化物半導体からなる半導体素子の製造方法であって、MgをドープしたIII 族窒化物半導体層の形成後に、400度以上の温度での熱処理工程を複数有した半導体素子の製造方法において、最終以外の400度以上の温度での熱処理工程では、アンモニア雰囲気中において熱処理を行い、最終の400度以上の温度での熱処理工程では、窒素雰囲気中において熱処理を行う。このように熱処理を行えば、p型のIII 族窒化物半導体層の正孔濃度を減少させずに半導体素子を製造することができる。

(もっと読む)

縦型有機トランジスタ、その製造方法及び発光素子

【課題】電流変調が容易で、製造コストを抑えた縦型有機トランジスタ及びその製造方法を提供する。

【解決手段】上部電極(エミッタ電極1)と、下部電極(コレクタ電極2)と、両電極間に設けられた有機半導体3と、その有機半導体3内に設けられた層状連続体4とを有し、その層状連続体4が、連続する絶縁性金属化合物4bと、絶縁性金属化合物4b内に分布する粒状金属4aとを有するように構成して、上記課題を解決する。その製造方法は、下部電極(エミッタ電極1)が形成された基板10上に下側有機半導体層3bを形成する工程と、下側有機半導体層3b上に、連続する絶縁性金属化合物4bとその絶縁性金属化合物4b内に分布する粒状金属4aとを有する層状連続体4を形成する工程と、層状連続体4上に上側有機半導体層3aを形成する工程と、上側有機半導体層3a上に上部電極(エミッタ電極1)を形成する工程とを有するように構成する。

(もっと読む)

炭化ケイ素静電誘導トランジスタの制御装置及び制御方法

【課題】電力用変換器の過電流においてオン抵抗損失の著しい増大を抑制して、電力用変換器の小型・軽量化および低価格化をはかる。

【解決手段】定格電流容量の5倍ないし20倍のサージ電流が流れる電力用変換器に炭化ケイ素を素材とした静電誘導トランジスタを適用するにあたり、該静電誘導トランジスタのオン時のゲート電圧を定格電流以下の正常動作時にはゲート接合のビルトイン電圧以下として高速、低損失、高効率の電力変換を行い、定格を超える過電流が流れた場合にかぎりゲート電圧をビルトイン電圧以上に昇圧することにより過電流による素子破壊を防止する制御方法によって変換器に使用される炭化ケイ素静電誘導トランジスタの電流容量を変換のそれを大幅に超えない小容量とする。

(もっと読む)

選択的エピタキシまたは選択的注入の使用による、炭化ケイ素におけるセルフアライントランジスタおよびダイオードトポロジー

【課題】SiC内に縦型ダイオードおよびトランジスタを作る方法が提供される。

【解決手段】この発明に従った方法は、マスク(たとえば機構を素子にエッチングするために以前使用されたマスク)を選択的エピタキシャル成長または選択的イオン注入用に使用する。このように、静電誘導トランジスタおよびバイポーラ接合トランジスタのゲート領域およびベース領域が、セルフアラインプロセスで形成可能である。プレーナダイオードおよびプレーナエッジ終端構造(たとえばガードリング)を作る方法も提供される。

(もっと読む)

窒化物半導体素子および窒化物半導体素子の製造方法

【課題】ノーマリオフタイプの窒化物半導体素子およびその製造方法を提供すること。

【解決手段】このCAVETは、n+型GaN基板1と、この基板の主面1aに形成された開口部3を有する絶縁膜2と、窒化物半導体積層構造部4とを備えている。窒化物半導体積層構造部4は、その平行面7、+c軸側傾斜面8および−c軸側傾斜面9に平行な面を積層界面15として順に積層されたn−型GaN層5およびn−型GaN層5と格子定数の異なるn+型AlGaN層6を備えている。ゲート電極10は、−c軸側傾斜面9に対向して形成され、ソース電極11は、n+型AlGaN層6と電気的に接続されている。ドレイン電極は、n+型GaN基板1と電気的に接続されている。

(もっと読む)

窒化物半導体装置とその製造方法

【課題】 窒化物半導体基板を利用する半導体装置に関し、特に、窒化物半導体基板に含まれていたp型不純物が、基板表面に結晶成長する窒化物半導体に移動することを抑制する技術を提供する。

【解決手段】 Mg(p型不純物)を含むp型のGaN層40の表面41に、n型のGaN層50を結晶成長させる工程が、前半工程と後半工程を有しており、前半工程では、第1温度範囲内で、p型のGaN層40の表面41に、低温結晶成長層52(n型のGaN層50)を結晶成長させ、後半工程では、第1温度範囲よりも高温の第2温度範囲内で、前半工程で結晶成長した低温結晶成長層52(n型のGaN層50)の表面に、高温結晶成長層51(n型のGaN層50)をさらに結晶成長させる。

(もっと読む)

半導体装置

【課題】ゲートへのノイズマージンが大きい接合FETを提供する。

【解決手段】接合FET1は、炭化珪素からなるn+基板12の主面に形成された接合FET1のドリフト領域のn−層11と、ドリフト領域のn−層11に接合して形成されたゲート領域のp+層9と、n+基板12の上層に設けられたゲート電極14と、を有している。この接合FET1は、さらに、n+基板12の主面に形成され、ゲート領域のp+層9とゲート電極14とを電気的に接続するpnダイオード2、3を内蔵している。

(もっと読む)

141 - 160 / 267

[ Back to top ]