Fターム[5F102GB04]の内容

接合型電界効果トランジスタ (42,929) | 主電流経路 (2,759) | 基板表面に垂直(縦型FET) (311)

Fターム[5F102GB04]の下位に属するFターム

メサ側面を流れるもの (36)

埋込ドレイン、ソース(基板表面取出し) (8)

Fターム[5F102GB04]に分類される特許

61 - 80 / 267

半導体装置およびその製造方法

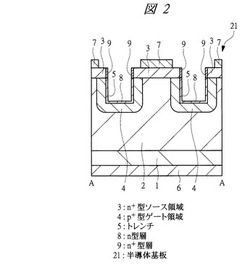

【課題】炭化珪素基板を用いた接合型FETにおいて、ゲート・ソース間のpn接合領域において生じるリーク電流を低減する。

【解決手段】炭化珪素基板を用いたトレンチ型接合FETにおいて、トレンチ5の側壁および底面に窒素を導入することにより、トレンチ5の表面にn型層8およびn+型層9を形成する。これによりp+型ゲート領域4とn+型ソース領域3との接合領域であるpn接合領域はダメージの多いトレンチ5の側壁ではなく半導体基板21の主面において露出し、また、その露出する領域は狭まるため、pn接合領域におけるリーク電流を低減することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 チャネルの高い移動度と、優れた縦方向耐圧とを得た上で、安定して低いオン抵抗を確保することができる、半導体装置等を提供する。

【解決手段】本発明の半導体装置は、n型ドリフト層4/p型層6/n型表層8を含むGaN系積層体15、に形成され、GaN系積層体には、開口部5が設けられ、再成長層27と、ゲート電極11と、ソース電極31と、ドレイン電極39とを備え、再成長層27は電子走行層22および電子供給層26を含み、チャネルが二次元電子ガスであり、p型層6とn型表層8との間、および開口部を囲むGaN系積層体の端面と再成長層との間、の少なくとも一方に、GaNよりも格子定数が小さいエピタキシャル層が挿入されていることを特徴とする。

(もっと読む)

電界効果トランジスタ

【課題】 第1半導体層と第2半導体層とのヘテロ接合により第1半導体層に二次電子ガス層を生じさせつつ、ソース電極とドレイン電極との間の通電状態を切り換えるためのゲート電圧のしきい値を所定の値に調整することができる電界効果トランジスタを提供する。

【解決手段】 電界効果トランジスタ10では、サファイア基板11上に、i型のGaNからなるGaN層13と、i型のGaNと格子定数が異なるi型のAlGaNからなるAlGaN層14と、i型のAlGaNよりもエッチングレートが小さいi型のAlInNからなるAlInN層15とが順に形成されている。AlInN層15の上端から途中まで伸びている溝25が形成されており、その溝25の底部の少なくとも一部にゲート電極26がショットキー接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】 サージ電圧等に対するバイパス用の保護部を備え、耐圧性能および低いオン抵抗(低いオン電圧)を実現し、かつ、構造が簡単な、大電流用の、半導体装置およびその製造方法を提供する。

【解決手段】 支持基体上にオーミック接触するGaN層を有するn+型GaN基板1と、第1領域R1上におけるn−型GaNドリフト層2を有するFETと、第2領域R2においてn−型GaNドリフト層2にショットキー接触するアノード電極を有するSBDとを備え、FETとSBDとは並列配置されており、n+型GaN基板1の裏面に、FETのドレイン電極DおよびSBDのカソード電極Cを備えることを特徴とする。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート電圧が閾値近傍に近づくときに発生する過剰なドレイン電流を抑制する。

【解決手段】トレンチ6の先端部に形成されたn-型チャネル層7がトレンチ6の長辺に位置する部分よりも膜厚が厚くなるため、そのトレンチ6の先端部においてJFET構造が構成されないようにする。例えば、トレンチ6の先端部の周辺を含めてn+型SiC基板1の外縁部においてn+型ソース領域4が除去されると共に、トレンチ6の先端部においてn-型チャネル層7および第2ゲート領域8が除去された凹形状とする。これにより、トレンチ6の先端部のJFET構造の閾値がトレンチ6の長辺に位置する部分のJFET構造の閾値からずれることによる影響を受けることがない。したがって、ゲート電圧が閾値近傍に近づくときに発生する過剰なドレイン電流を抑制できる構造のSiC半導体装置とすることが可能となる。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】高耐圧および高電流のスイッチング動作が可能で、かつ製造が容易なFETを提供する。

【解決手段】半導体薄体の一の主表面に設けられた、第1導電型のソース領域(1)と、第1導電型のチャネル領域(10)と、チャネル領域を限定する第2導電型の限定領域(5)と、他の主表面に設けられた第1導電型のドレイン領域(3)と、厚さ方向に連続する第1導電型のドリフト領域(4)とを備え、ドリフト領域(4)およびチャネル領域(10)の不純物濃度は、ソース領域(1)、ドレイン領域(3)および限定領域(5)の不純物濃度よりも低く、チャネル領域(10)の不純物濃度はドリフト領域(4)の不純物濃度よりも低い。

(もっと読む)

打込みされた側壁を有する半導体デバイスを製造する方法およびそれによって製造されたデバイス

半導体デバイスおよびそのデバイスを製造する方法が提供される。デバイスは、接合型電界効果トランジスタ(JFET)、または接合型バリアショットキー(JBS)ダイオードまたはPiNダイオードのようなダイオードであり得る。デバイスは、打込みマスクを用いる選択的イオン注入を使用して製造される。デバイスは、打込みマスクからの通常の入射イオンの散乱によって形成された打込み側壁を有する。長いチャネル長の縦型接合型電界効果トランジスタが記載される。デバイスは、シリコンカーバイド(SiC)のようなワイドバンドギャップ半導体材料から製造されることができ、高温および高出力の用途において使用することができる。 (もっと読む)

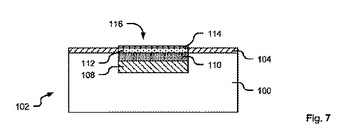

縦型パワートランジスタ装置、半導体チップ、および縦型パワートランジスタ装置の製造方法

縦型トランジスタ装置は、III−V族半導体材料から形成される基板(100)と、少なくとも部分的に基板内に収容される多層スタック(116)とを備える。多層スタックは、基板(100)に隣接して配置される半絶縁層(108)と、第1のIII−V族半導体材料から形成されており、半絶縁層に隣接して配置される第1の層(110)とを備える。多層スタック(116)はまた、第2のIII−V族半導体材料から形成されて、第1の層(110)に隣接する第2の層(112)と、第1の層と第2の層との界面に形成されるヘテロ接合部とを備える。  (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】小型かつ高性能な半導体装置を提供すること。

【解決手段】SiC基板11上に形成された第1のGaN層12と、第1のGaN層12上に形成されたソースパッド23と、第1のGaN層12上に形成された複数の円柱状のGaN層14と、これらの円柱状のGaN層14の上端に接するように形成された第2のGaN層16と、第2のGaN層16上に形成されたドレインパッド25と、を具備する半導体装置であって、複数の円柱状のGaN層14は、それぞれ下から順にソース領域18、ゲート領域19、ソース領域よりも径が細いドレイン領域17からなり、ソース領域18の周囲には第1の絶縁膜20、ゲート領域19の周囲にはゲート電極21、ドレイン領域17の周囲には所定の空間を介して第2の絶縁膜22がそれぞれ形成される。

(もっと読む)

III族窒化物積層基板

【課題】割れの発生を抑制することに加え、結晶性も向上させたIII族窒化物半導体を提供する。

【解決手段】シリコン基板と、該シリコン基板上に形成した歪超格子積層体と、該歪超格子積層体上に成長したIII族窒化物積層体とを具えるIII族窒化物積層基板であって、前記歪超格子積層体は、少なくとも前記シリコン基板側から順に第1超格子積層体と第2超格子積層体とを有し、前記第1超格子積層体は、AlN層とGaN層とを交互に積層してなり、前記第2超格子積層体は、AlN層とAlxGa1-xN(0<x<1)層とを交互に積層してなり、かつ前記第1超格子積層体の総厚が1μmを超えることを特徴とする。

(もっと読む)

異なる半導体材料の半導体相互接続層及び半導体チャネル層を備えたトランジスタ

トランジスタが、第1の半導体材料の半導体ドリフト層と、この半導体ドリフト層上の半導体チャネル層とを含むことができる。半導体チャネル層は、第1の半導体材料とは異なる第2の半導体材料を含むことができる。半導体ドリフト層と半導体チャネル層の間には、第1及び第2の半導体材料とは異なる第3の半導体材料を含むことができる半導体相互接続層を電気的に結合することができる。また、半導体チャネル層上には、制御電極を設けることができる。 (もっと読む)

半導体装置およびその製造方法

【課題】オン抵抗を低く、移動度を高く、かつピンチオフ特性を良好にした上で、ドレイン電圧を増大させてもキンク現象が生じない、大電流用の、半導体装置およびその製造方法を提供する。

【解決手段】開口部28が設けられたGaN系積層体15と、チャネルを含む再成長層27と、ゲート電極Gと、ソース電極Sと、ドレイン電極Dとを備え、再成長層27は電子走行層22および電子供給層26を含み、GaN系積層体には再成長層に開口部でその端面が被覆されるp型GaN層6が含まれ、そのp型GaN層にオーミック接触するp部電極11を備えることを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】小型化とこれに伴う装置の特性の劣化の抑制とが同時に可能な半導体装置を提供すること。

【解決手段】SiC基板11上に形成された第1のGaN層12と、第1のGaN層12上に形成されたソースパッド23と、第1のGaN層12上に形成された複数の円柱状のGaN層14と、これらの円柱状のGaN層14の上端に接するように形成された第2のGaN層16と、第2のGaN層16上に形成されたドレインパッド25と、を具備する半導体装置であって、複数の円柱状のGaN層14は、それぞれ下から順にソース領域18、ゲート領域19、ドレイン領域17からなり、ソース領域18の周囲には第1の絶縁膜20、ゲート領域19の周囲にはゲート電極21、ドレイン領域17の周囲には第2の絶縁膜22がそれぞれ形成される。

(もっと読む)

有機トランジスタ、回路素子及びそれらの製造方法

【課題】低電圧で作動するとともに大きなベース電圧を印加した場合でも耐電圧が高く、各種の回路素子への応用が容易で、製造コストを抑えた有機トランジスタ及び回路素子を提供する。

【解決手段】コレクタ電極1とエミッタ電極2と両電極間に設けられた有機半導体層3と有機半導体層3内に設けられたベース電極4とを有する縦型トランジスタ部、及び、ベース電極4とベース電圧電源端子7との間に設けられた抵抗部6、を有する。抵抗部6は、コレクタ電極1と同じ材料からなりベース電圧電源端子7に接続する第1電極21と、エミッタ電極2と同じ材料からなりベース電極4に接続する第2電極22と、有機半導体層3と同じ材料からなり第1電極21及び第2電極22間に挟まれた抵抗層24とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネルにおけるキャリア移動度が高く、ノーマリオフを実現する半導体装置を提供する。

【解決手段】 n型GaNキャップ層18の開口部28との界面(開口部境界面)は、複数のほぼ鉛直な面S1と、各面S1の間を補完するように形成された傾斜した面S3により構成されている。傾斜面はドライエッチングにより形成し、異方性エッチングによりダメージ層を除去する。縦型FET1では、GaN基板10上に、六方晶のGaN、AlGaNを、{ 0 0 0 1}面を成長面として、エピタキシャル成長させており、n型GaNキャップ層18における鉛直な面S1は、{ 1-1 0 0}面(m面)となる。m面は、C面とは異なり無極性面であるので、m面を成長面として、GaN電子走行層22、AlGaN電子供給層26を再成長させると、ピエゾ電荷等の分極電荷がAlGaN/GaNヘテロ界面に生じない。よって、縦型FET1においては、よりノーマリオフに近づけることが可能となる。

(もっと読む)

新規な有機半導体材料とそれを用いた電子デバイス

【課題】塗工や印刷あるいは蒸着等の簡便なプロセスで、二次元的に結晶成長することにより連続膜が成膜できる、特性の優れた有機半導体材料を提供する。

【解決手段】下記一般式(I)で表わされることを特徴とする有機半導体材料。

(一般式(I)中、R1からR10はそれぞれ独立に、水素、置換若しくは無置換のアルキル基、置換若しくは無置換のアルコキシ基又は置換若しくは無置換のアルキルチオ基、置換若しくは無置換のアリール基を表わし、R1からR10は互いに結合して環を形成してよく、Xは炭素又は窒素を表す)

(もっと読む)

電気回路中にて静電気放電保護素子として用いるためのゲート制御されたフィン型抵抗素子、および、電気回路内部を静電気放電から保護するための保護装置

【課題】電気回路中にて静電気放電保護を確実化しながら小型化を実現する。

【解決手段】電気回路において静電気放電保護素子として使用するためのゲート制御されたフィン型抵抗素子は、第1端子領域、第2端子領域、および、第1端子領域と第2端子領域との間に形成されたチャネル領域を有するフィン構造体を備えている。さらに、フィン型抵抗素子は、チャネル領域の上面の一部上に少なくとも形成されたゲート領域を備えている。ゲート領域は、ゲート制御部に電気的に結合されており、ゲート制御部は、ゲート領域に印加される電気的な電位を制御することにより、電気回路が第1動作状態である間は、ゲート制御されたフィン型抵抗素子の電気抵抗を高くし、静電気放電現象の開始によって特徴付けられている第2動作状態では、電気抵抗をより低くする。

(もっと読む)

半導体装置

【課題】耐圧が安定するとともにオン抵抗を低減することが可能な半導体装置を提供する。

【解決手段】半導体装置であるMOSFETは、導電型がn型であるSiCウェハと、SiCウェハの第1の主表面20Aを含むように形成された導電型がp型の複数のpボディ21と、平面的に見て複数のpボディ21のそれぞれに取り囲まれる領域内に形成された導電型がn型のn+ソース領域22とを備えている。pボディ21は、平面的に見て円形形状を有しており、n+ソース領域22は、平面的に見てpボディ21と同心に配置された円形形状を有している。そして、複数のpボディ21は、平面的に見て正六角形の各頂点に位置するように配置されている。

(もっと読む)

化合物半導体装置の製造方法

【課題】基板の付け替えに際して基板を適切に分離することができる化合物半導体装置の製造方法を提供する。

【解決手段】基板の上方に、第1のバンドギャップのAlxGa1-xN(0≦x<1)を含む第1の化合物半導体層を形成する。前記第1の化合物半導体層上に、前記第1のバンドギャップよりも広い第2のバンドギャップのAlyInzGa1-y-zN(0<y<1、0<y+z≦1)を含む第2の化合物半導体層を形成する。前記第2の化合物半導体層の上方に、化合物半導体積層構造を形成する。前記第1のバンドギャップと前記第2のバンドギャップとの間のエネルギを有する光を前記第1の化合物半導体層に照射しながら前記第1の化合物半導体層を除去して、前記基板を前記化合物半導体積層構造から分離する。

(もっと読む)

半導体装置およびその製造方法

【課題】 サージ電圧等に対するバイパス用の保護部を備え、耐圧性能および低いオン抵抗(低いオン電圧)を実現し、かつ、構造が簡単な、大電流用の、半導体装置およびその製造方法を提供する。

【解決手段】 支持基体上にオーミック接触するGaN層を有するn+型GaN基板1と、第1領域R1上におけるn−型GaNドリフト層2を有するFETと、第2領域R2においてn−型GaNドリフト層2にショットキー接触するアノード電極を有するSBDとを備え、FETとSBDとは並列配置されており、n+型GaN基板1の裏面に、FETのドレイン電極DおよびSBDのカソード電極Cを備えることを特徴とする。

(もっと読む)

61 - 80 / 267

[ Back to top ]