Fターム[5F102GK09]の内容

接合型電界効果トランジスタ (42,929) | バッファ層(中間層) (2,318) | 格子定数のずれ、格子歪の利用 (111)

Fターム[5F102GK09]に分類される特許

41 - 60 / 111

半導体装置

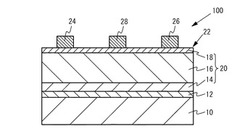

【課題】GaN系半導体層のグレインサイズを大型化することが可能な半導体装置を提供すること。

【解決手段】本発明は、(111)面から0.1度以下のオフ角度で傾斜した面を主面とするSi基板10と、Si基板10の主面に接して設けられ、(002)面のX線回折におけるロッキングカーブの半値幅が2000sec以下であるAlN層12と、AlN層12上に設けられたGaN系半導体層20と、を備える半導体装置100である。

(もっと読む)

窒化物半導体装置及び窒化物半導体装置の製造方法

【課題】高耐圧化した窒化物半導体装置を提供する。

【解決手段】窒化物半導体装置200は、シリコン基板201上に形成されたバッファ層220と、バッファ層220上に形成された第1の窒化物超格子層204aと、第1の窒化物超格子層204a上に形成された活性領域層230とを備え、バッファ層220は、不純物がドープされた第2の窒化物超格子層204bと、第2の窒化物超格子層204b上に形成され、不純物がドープされた第1の窒化物半導体層205と、第1の窒化物半導体層205上に形成され、第1の窒化物半導体層205よりもAl組成及び不純物の濃度が高い第2の窒化物半導体層206とを有する。

(もっと読む)

窒化物半導体素子

【課題】 発光効率が高く信頼性の高い窒化物半導体発光素子を提供する。

【解決手段】本発明の実施の形態の窒化物半導体素子は、第1の主面上の面内方向に形成された複数の凸部1aと、隣接する前記凸部の間の凹部1bと、を有する基板1と、前記基板1の前記凹部1a及び前記凸部1b上に形成されたAlx1Ga1−x1N(0≦x1≦1)第1埋込層2と、前記第1埋込層2上に形成されたInyAlzGa1−y−zN(0<y≦1、0≦z≦1)埋込層3と、前記埋込層3上に形成されたAlx2Ga1−x2N(0≦x2≦1)第2埋込層4と、を備える。前記第1埋込層2の前記凹部1bの上に形成された部分と、前記第1埋込層2の前記凸部1aの上に形成された部分とは、互いに結合しない。前記埋込層3の前記凹部1bの上に形成された部分と、前記埋込層3の前記凸部1aの上に形成された部分とは、互いに結合している。

(もっと読む)

窒化物半導体基板

【課題】

しきい値電圧をより向上させることのできる、中間層とデバイス活性層の間にノーマリ

ーオフ作用をもつ窒化物半導体層を形成する。

【解決手段】

Si単結晶基板上に形成され窒化物半導体の積層構造からなる中間層と、中間層上に形成され、組成AlxGa1−xN(0≦x≦0.05)、厚さ200nm以上2000nm以下、炭素濃度1´1018atoms/cm3以上1´1021atoms/cm3以下の窒化物半導体からなる領域1と、領域1上に形成され、組成AlyGa1−yN(0.1≦y≦1)、厚さ0.2nm以上100nm以下、炭素濃度1´1018atoms/cm3以上1´1021atoms/cm3以下の窒化物半導体からなる領域2と、領域2上に形成される窒化物半導体のデバイス活性層からなる窒化物半導体基板。

(もっと読む)

半導体素子およびその製造方法

【課題】バッファで改善された結晶性および平坦性を有効に機能積層体に引き継がせることにより、機能積層体の平坦性および結晶性を向上させた半導体素子をその製造方法とともに提供する。

【解決手段】基板1上に、バッファ2と、複数の窒化物半導体層を含む機能積層体3とを具える半導体素子100であって、機能積層体3は、バッファ2側にn型またはi型である第1のAlxGa1−xN層4(0≦x<1)を有し、バッファ2と機能積層体3との間に、第1のAlxGa1−xN層4とAl組成が略等しいp型不純物を含むAlzGa1−zN調整層5(x−0.05≦z≦x+0.05、0≦z<1)を具え、バッファ2は、少なくとも機能積層体3側にAlαGa1−αN層(0≦α≦1)を含み、該AlαGa1−αN層のAl組成αと、第1のAlxGa1−xN層4のAl組成xとの差が、0.1以上であることを特徴とする。

(もっと読む)

窒化物半導体素子

【課題】 リーク電流の増加を抑制しつつ、基板上のIII族窒化物半導体の超格子構造の周期数を増やした場合でもクラックの発生を抑制できる窒化物半導体素子を提供する。

【解決手段】 基板2上に、GaN層10およびAlN層11が複数対交互に積層された第1GaN/AlN超格子層8を形成し、この第1GaN/AlN超格子層8に接するように、GaN層12およびAlN層13が複数対交互に積層された第2GaN/AlN超格子層9を形成する。第2GaN/AlN超格子層9上には、GaN電子走行層6およびAlGaN電子供給層7からなる素子動作層を形成する。これにより、HEMT1を構成する。このHEMT1において、第1GaN/AlN超格子層8のc軸平均格子定数LC1と、第2GaN/AlN超格子層9のc軸平均格子定数LC2と、GaN電子走行層6のc軸平均格子定数LC3とが、式(1)LC1<LC2<LC3を満たすようにする。

(もっと読む)

窒化物半導体素子

【課題】Si基板の上に形成した窒化物半導体素子の生産性及び動作特性を向上させる。

【解決手段】窒化物半導体素子は、シリコン基板101の上に初期層102を介して形成された歪み抑制層110と、歪み抑制層の上に形成された動作層120とを備えている。歪み抑制層110は、第1のスペーサ層111と、第1のスペーサ層の上に接して形成された第2のスペーサ層112と、第2のスペーサ層の上に接して形成された超格子層113とを有している。第1のスペーサ層は、格子定数が第2のスペーサ層よりも大きい。超格子層は、第1の層113A及び第1の層よりも格子定数が小さい第2の層113Bが交互に積層されている。超格子層の平均の格子定数は、第1のスペーサ層の格子定数よりも小さく且つ第2のスペーサ層の格子定数よりも大きい。

(もっと読む)

多重構造窒化物半導体構造

【課題】基板上に窒化物半導体をエピタキシャル成長する場合、窒化物半導体素子厚さに依存しない反りの制御が可能になる多層構造窒化物半導体素子の構造を提供する。

【解決手段】多重構造窒化物半導体は、基板1上に、窒化物半導体が1層かまたは複数層積層されたバッファ層2と、バッファ層2上に窒化物半導体が形成された多層構造バッファ層3と、多層構造バッファ層3上に窒化物半導体が1層かまたは複数層積層された半導体層4とから構成される。多層構造バッファ層3は多層構造バッファ層5と多層構造バッファ層5上に接したバッファ層6とが1層かまたは複数層積層されることで成り、多層構造バッファ層5は、バッファ層7とバッファ層7上に接したバッファ層8から成り、バッファ層7とバッファ層8は複数層積層されている。バッファ層7およびバッファ層8のすくなくとも一方の3族材料の組成を変化させることで窒化物半導体素子の反りの制御を可能にした。

(もっと読む)

電界効果トランジスタ、電界効果トランジスタの製造方法、および電子装置

【課題】 高い閾値電圧と、低いオン抵抗とを両立可能であり、かつ、パラレル伝導を抑制できる電界効果トランジスタを提供する。

【解決手段】

基板601上に、III族窒化物のバッファ層602、チャネル層603、障壁層605、およびキャップ層606が、前記順序で積層され、

各半導体層の上面は、(0001)結晶軸に垂直なIII族原子面であり、

バッファ層602は、格子緩和され、

障壁層605は、引っ張り歪みを有し、

チャネル層603およびキャップ層606が圧縮歪みを有するか、または、チャネル層603が格子緩和され、キャップ層606が引っ張り歪みを有し、

障壁層605上の一部の領域に、キャップ層606、ゲート絶縁膜607、およびゲート電極608が、前記順序で積層され、他の領域に、ソース電極609とドレイン電極610が形成されていることを特徴とする電界効果トランジスタ。

(もっと読む)

窒化物半導体素子およびその製造方法

【課題】Al含有率が低いAlGaN層やGaN層を用いた超格子歪緩衝層を平坦性良く形成すると共に、該超格子歪緩衝層上に平坦性および結晶性が良好な窒化物半導体層を形成した窒化物半導体素子を提供する。

【解決手段】基板と、基板上に形成されたAlNからなるAlN歪緩衝層と、AlN歪緩衝層上に形成された超格子歪緩衝層と、超格子歪緩衝層上に形成された窒化物半導体層とを備える窒化物半導体素子であって、超格子歪緩衝層は、AlxGa1−xN(0≦x≦0.25)よりなり、且つ、p型不純物を含む第1の層と、AlNよりなる第2の層とを交互に積層して超格子構造を形成したものであることを特徴とする、窒化物半導体素子である。

(もっと読む)

半導体装置およびその製造方法

【課題】 チャネルの高い移動度と、優れた縦方向耐圧とを得た上で、安定して低いオン抵抗を確保することができる、半導体装置等を提供する。

【解決手段】本発明の半導体装置は、n型ドリフト層4/p型層6/n型表層8を含むGaN系積層体15、に形成され、GaN系積層体には、開口部5が設けられ、再成長層27と、ゲート電極11と、ソース電極31と、ドレイン電極39とを備え、再成長層27は電子走行層22および電子供給層26を含み、チャネルが二次元電子ガスであり、p型層6とn型表層8との間、および開口部を囲むGaN系積層体の端面と再成長層との間、の少なくとも一方に、GaNよりも格子定数が小さいエピタキシャル層が挿入されていることを特徴とする。

(もっと読む)

モノリシック集積複合III−V族及びIV族半導体デバイス、並びにその製造方法

【課題】単一のダイの上にIII−V族半導体デバイスをIV族半導体デバイスと共に集積する、複合デバイスの製造方法を提供する。

【解決手段】IV族半導体基板202上にIII−V族半導体本体274a,274bを形成するステップと、III−V族半導体本体にトレンチを形成し、トレンチ内にIV族半導体本体232を形成するステップとを有する。この方法は、IV族半導体本体内に少なくとも1つのIV族半導体デバイス272を製造するステップと、III−V族半導体本体内に少なくとも1つのIII−V族半導体デバイス274を製造するステップも含む。III−V族半導体本体の上面とIV族半導体本体の上面とを平坦化して、それぞれの上面をほぼ同一平面にするステップをさらに含む。一実施形態では、トレンチの側壁に隣接する、前記IV族半導体本体の欠陥領域に、少なくとも1つの受動デバイスを製造するステップをさらに含む。

(もっと読む)

高電子移動度トランジスタ及びその製造方法

【課題】トランジスタ中の電子移動度を向上させる上、デバイスの性能を向上させる高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】高電子移動度トランジスタは、基板110と、基板110上に形成したバッファ層120と、複数のInGaAs薄膜と複数のInAs薄膜とを交互に積層して形成した超格子構造を含み、バッファ層120上に形成したチャネル層130と、チャネル層130上に形成したスペーサ層140と、スペーサ層140上に形成したショットキー層160と、ショットキー層160上に形成したキャップ層170とを備える。

(もっと読む)

高移動度チャネル(High−MobilityChannels)を有する装置のソース/ドレイン工学

【課題】高移動度チャネルを有する装置のソース/ドレイン工学を提供する。

【解決手段】集積回路構造は、基板及び基板の上方のチャネルを備える。チャネルは、III族元素とV族元素から構成される第一III-V族化合物半導体材料からなる。ゲート構造はチャネルの上方に設置される。ソース/ドレイン領域はチャネルに隣接し、本質的に、シリコン、ゲルマニウム、及び、それらの組み合わせからなる群から選択されるドープされたIV族半導体材料から形成されるIV族領域を含む。

(もっと読む)

III族窒化物積層基板

【課題】割れの発生を抑制することに加え、結晶性も向上させたIII族窒化物半導体を提供する。

【解決手段】シリコン基板と、該シリコン基板上に形成した歪超格子積層体と、該歪超格子積層体上に成長したIII族窒化物積層体とを具えるIII族窒化物積層基板であって、前記歪超格子積層体は、少なくとも前記シリコン基板側から順に第1超格子積層体と第2超格子積層体とを有し、前記第1超格子積層体は、AlN層とGaN層とを交互に積層してなり、前記第2超格子積層体は、AlN層とAlxGa1-xN(0<x<1)層とを交互に積層してなり、かつ前記第1超格子積層体の総厚が1μmを超えることを特徴とする。

(もっと読む)

化合物半導体エピタキシャルウェハ及びその製造方法、並びにHEMT素子

【課題】化合物半導体エピタキシャルウェハ外周部より得られたHEMT素子であってもリーク電流の急激な増加がなく、良好な耐圧を持つHEMT素子が得られる化合物半導体エピタキシャルウェハ及びその製造方法、並びにこのような化合物半導体エピタキシャルウェハを用いて得られるHEMT素子を提供する。

【解決手段】基板1上に、バッファ層3と、下部電子供給層4と、電子走行層5と、上部電子供給層6と、を有する化合物半導体エピタキシャルウェハ10において、前記バッファ層3はAlGaAsからなり、前記下部電子供給層4及び前記上部電子供給層6はAlGaAsからなり、前記下部電子供給層4及び前記上部電子供給層6のAl組成が0.2

0以上0.27以下であり、かつ前記バッファ層3のAl組成が前記下部電子供給層4の

Al組成より小さい。

(もっと読む)

半導体素子用エピタキシャル基板、半導体素子、および半導体素子用エピタキシャル基板の製造方法

【課題】反りが抑制された、半導体素子用のエピタキシャル基板を提供する。

【解決手段】下地基板1の上にIII族窒化物層群を積層形成した半導体素子用のエピタキシャル基板10において、III族窒化物層群が、少なくとも2層以上のIII族窒化物層が積層された緩衝層2と、Inx1Aly1Gaz1N(0≦x1≦1、0≦y1≦1、0<z1≦1、x1+y1+z1=1)なる組成のIII族窒化物からなるチャネル層3と、Inx2Aly2Gaz2N(0≦x2≦1、0<y2≦1、0≦z2≦1、x2+y2+z2=1)なる組成のIII族窒化物からなる障壁層4と、を備え、緩衝層2の少なくとも1つが、格子空孔を有する格子空孔内在層23であるようにする。

(もっと読む)

半導体装置

【課題】AlNを含む基板上において、電気特性に優れた横型デバイスを得ること。

【解決手段】化学式Ala’Ga1−a’N(0<a’≦1)で表される組成をもつ基板(11、12a)上に、緩衝層(12a、12b)を介して、化学式Alm’Ga1−m’N(0≦m’<1)で表される組成をもつ能動層(13、14)が形成され、前記能動層上に離間して第1及び第2の主電極(15、16)が形成された構成を備え、前記能動層において前記第1及び第2の主電極間に電流が流されて動作する半導体装置(10)であって、

前記緩衝層は、化学式AlbGa1−bN(0<b<1、a’>b>m’)で表される組成を有することを特徴とする半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】基板と能動層との間に導電性半導体層を挿入した構成をもつGaN系デバイスにおいて、導電性半導体層中のドーパントの悪影響を抑制する。

【解決手段】このHEMT素子10においては、基板11としてn−GaN(n型のGaNウェハ)が用いられる。この上に、リーク電流の低減及び電流コラプス抑制等のためにp型GaN層(導電性半導体層)12が形成される。p型GaN層12の上に、ノンドープAlN層(半絶縁性半導体層)13が形成され、その上に、半絶縁性GaNからなる電子走行層(能動層)14、n−AlGaNからなる電子供給層(能動層)15が、MBE法、MOVPE法等によって順次形成される。

(もっと読む)

電子デバイス用エピタキシャル基板およびその製造方法

【課題】横方向リーク電流の低減と横方向耐圧特性を両立させ、縦方向耐圧を向上させる電子デバイス用エピタキシャル基板を提供する。

【解決手段】Si基板1上のバッファ3上にIII族窒化物層をエピタキシャル成長させた、チャネル層4aおよび電子供給層4bを有する主積層体4を具え、前記バッファは、Si基板と接する初期成長層5および初期成長層上の超格子多層構造からなる超格子積層体6を有し、初期成長層はAlN材料からなり、前記超格子積層体はBa1Alb1Gac1Ind1N材料からなる第1層6aおよび第1層とはバンドギャップの異なるBa2Alb2Gac2Ind2N材料からなる第2層6bを積層してなり、前記超格子積層体と、前記主積層体を構成するチャネル層のバッファ側の部分は、C濃度が1×1018/cm3以上であり、チャネル層の電子供給層側の部分は、C濃度が4×1016/cm3以下であることを特徴とする。

(もっと読む)

41 - 60 / 111

[ Back to top ]