Fターム[5F102GR09]の内容

接合型電界効果トランジスタ (42,929) | 素子構造 (2,911) | 半導体基体内に付加領域を設けたもの (876) | 絶縁領域(高抵抗領域を含む) (273)

Fターム[5F102GR09]に分類される特許

21 - 40 / 273

半導体素子の構造、半導体抵抗素子の製造方法およびFETスイッチ回路

【課題】薄膜抵抗又は基板抵抗によって数kΩから数十kΩの抵抗値を持つゲート抵抗のサイズが基板長さ、基板幅に比べて大きい。

【解決手段】能動層10を有する半導体基板11と、半導体基板の能動層10にオーミック接触するソース電極13及びドレイン電極14と、能動層10の上方に設けられたゲート電極15と、半導体基板11に設けられた非活性領域16と、非活性領域16上にゲート電極15の一部が引出されて接触する導体17と、非活性領域16上で直流電圧が印加されるパッド電極18と、パッド電極18及び導体17にオーミック接触し、非活性領域16に設けられたゲート抵抗領域19とを備え、ゲート抵抗領域19は半導体基板11へボロンイオンを注入することによって形成され、ボロンイオンの注入量によりゲート抵抗領域19上のシート抵抗値を高めたことを備えたことを特徴とする半導体素子の構造が提供される。

(もっと読む)

半導体装置およびその製造方法

【課題】 JFET等のような低ノイズ特性が要求される半導体装置において、発生するノイズを低減すると共に、半導体装置を小さい寸法で製造する。

【解決手段】 半導体装置は、半導体層(101)に形成された素子分離(102)、第1導電型の不純物層(104)、第1導電型のソース領域(106)、第1導電型のドレイン領域(107)、第2導電型のゲート領域(105)、絶縁膜(108)を介して形成された制御電極(109)を備える。制御電極(109)に電圧を印加すると、半導体装置の動作中に制御電極(109)の下の不純物層(104)に空乏層を発生させることができ、キャリアは絶縁膜(108)と不純物層(104)の界面から離れて流れる。

(もっと読む)

半導体装置

【課題】窒化物半導体を用いた半導体装置のオン抵抗を低減できるようにする。

【解決手段】半導体装置は、アンドープのAlGaN層104と、該AlGaN層104の上に形成され、AlGaN層104とオーミック接触するソース電極107及びドレイン電極108とを有している。AlGaN層104の上部における少なくとも各電極107、108と接触する部分には、不純物拡散層110が形成されている。不純物拡散層110は、AlGaN層104に対しアクセプタ性を示す不純物が拡散し、且つ、AlGaN層104における窒素空孔と不純物とが結合してなる不純物準位が、AlGaN層104の伝導帯端の近傍に形成される。

(もっと読む)

半導体基板、電界効果トランジスタ、半導体基板の製造方法および電界効果トランジスタの製造方法

【課題】DWB法における貼り合わせ時にIII-V族化合物半導体層が受けるダメージを小さくするとともに、受けたダメージの影響および界面準位の影響を低く抑え、高いキャリアの移動度を有するIII-V族MISFETを提供する。

【解決手段】ベース基板102と第1絶縁体層104と半導体層106とを有し、ベース基板102、第1絶縁体層104および半導体層106が、ベース基板102、第1絶縁体層104、半導体層106の順に位置し、第1絶縁体層104が、アモルファス状金属酸化物またはアモルファス状金属窒化物からなり、半導体層が、第1結晶層108および第2結晶層110を含み、第1結晶層108および第2結晶層110が、ベース基板102の側から、第1結晶層108、第2結晶層110の順に位置し、第1結晶層108の電子親和力Ea1が、第2結晶層110の電子親和力Ea2より大きい半導体基板を提供する。

(もっと読む)

半導体装置

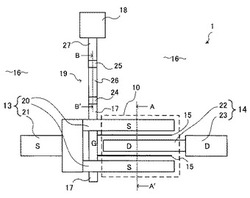

【課題】半導体装置内に保護ダイオードをレイアウトする。

【解決手段】半導体装置は、電界効果トランジスタ11と、電界効果トランジスタ11の形成領域30に隣接するダイオード形成領域12とを備え、ダイオード形成領域12はトランジスタの形成領域30と半導体基板上で絶縁され、ダイオード形成領域12内において、電界効果トランジスタ11のゲート電極1がバス配線7を介して半導体基板とショットキー接合とオーミック接合のいずれか又は両方の接合をする第1のダイオード電極20と、電界効果トランジスタ11のソース電極2がパッド5を介して半導体基板とオーミック接合とショットキー接合のいずれか又は両方の接合をする第2のダイオード電極21とを備えることによってゲート電極1とソース電極2間にダイオードが形成されたことを特徴とする。

(もっと読む)

トランジスタの制御回路、トランジスタの制御システム、およびトランジスタの制御方法

【課題】ゲートとフィールドプレートとを有するトランジスタのスイッチング速度を速くする。

【解決手段】ゲートとフィールドプレートとを有するトランジスタ4を制御する制御回路2であって、トランジスタを駆動するタイミングを検出する検出回路38と、駆動するタイミングに応答してゲートを駆動する第1の駆動タイミングとフィールドプレートを駆動する第2の駆動タイミングとを制御するタイミング制御回路40と、第1の駆動タイミングに応答してゲートを駆動し第2の駆動タイミングに応答してフィールドプレートを駆動する駆動回路42とを有する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】バッファ層の結晶成長時に高抵抗化の不純物をドーピングすることなく上層の化合物半導体の結晶品質を保持するも、バッファ層を高抵抗化してオフリーク電流を確実に抑制し、信頼性の高い高耐圧の化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2の裏面から、化合物半導体積層構造2の少なくともバッファ層2aに不純物、例えばFe,C,B,Ti,Crのうちから選ばれた少なくとも1種類を導入し、バッファ層2aの抵抗値を高くする。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】良好なノーマリ・オフ動作を可能とすることに加え、アバランシェ耐量が大きく、外部のダイオードを接続することを要せず、確実に安定動作を得ることができる信頼性の高い高耐圧のHEMTを得る。

【解決手段】化合物半導体積層構造2に形成された電極用リセス2Cを、ゲート絶縁膜6を介して電極材料で埋め込むようにゲート電極7を形成すると共に、化合物半導体積層構造2に形成された電極用リセス2Dを、少なくとも電極用リセス2Dの底面で化合物半導体積層構造2と直接的に接するように電極材料で埋め込み、化合物半導体積層構造2とショットキー接触するフィールドプレート電極8を形成する。

(もっと読む)

半導体装置

【課題】III族窒化物半導体を主材料として含むFETにおいて、ゲート−ドレイン間に高電圧を印加した場合でも、素子の劣化が発生し難くし、より信頼度を高くしたFETの提供。

【解決手段】基板上10に、[0001]または[000−1]結晶軸に平行な成長モードにて、格子緩和したバッファ層11、チャネル層12、電子供給層13をこの順にそれぞれIII族窒化物半導体を用いて形成された積層構造にあって、バッファ層11と電子供給層13の内、チャネル層12のIII族原子面側にある層は、チャネル層12のV族原子面側にある層よりもa軸長が大きく、電子供給層13は、チャネル層12よりもバンドギャップが大きい、電界効果トランジスタを備える。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート電極の電界集中を緩和して耐圧の更なる向上を実現することに加え、デバイス動作速度を向上させ、アバランシェ耐量が大きく、サージに対して強く、例えばインバータ回路等に適用する場合に外部のダイオードを接続することを要せず、ホールが発生しても安定動作を得ることができる信頼性の高い高耐圧の化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2に形成された電極用リセス2Cを、ゲート絶縁膜6を介して電極材料で埋め込むようにゲート電極7を形成すると共に、化合物半導体積層構造2に形成されたフィールドプレート用リセス2Dをp型半導体で埋め込み、化合物半導体積層構造2とp型半導体層8aで接触するフィールドプレート8を形成する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】材料の熱膨張係数の差に起因する反り等を抑制することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基板1と、基板1上方に形成された電子走行層2と、電子走行層2上方に形成された電子供給層3と、が設けられている。基板1の表面に、電子走行層2よりも熱膨張係数が小さい第1の領域1bと、電子走行層2よりも熱膨張係数が大きい第2の領域1aと、が混在する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート動作に関与する結晶表面における表面電荷蓄積を大幅に低減し、ピンチオフ特性が得られる、高性能のInN系FETを提供すること。

【解決手段】チャネル層としてInN系半導体を含む電界効果トランジスタである半導体装置であって、InN系半導体でなるチャネル層2の表面(c面)に、段差を形成して窒化物半導体の六方晶結晶のa面もしくはm面でなる側壁面2aを形成し、この側壁面2aにゲート電極6が配置され、ゲート電極6を挟むようにソース電極3とドレイン電極4がc面上に形成されている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】工程増を最小限とした簡便な手法で、素子形成領域における化合物半導体と同時に、しかもその結晶性を損なうことなく確実な素子分離を実現し、信頼性の高い化合物半導体装置を実現する。

【解決手段】Si基板1上の素子分離領域に初期層3を選択的に形成し、初期層3上を含むSi基板1上の全面に化合物半導体の積層構造4を形成して、積層構造4は、素子分離領域では初期層3と共に素子分離構造4Bとなり、素子形成領域ではソース電極5、ドレイン電極6及びゲート電極7が形成される素子形成層4Aとなる。

(もっと読む)

半導体基板、半導体装置、および半導体基板の製造方法

【課題】GaN系半導体は、面方位が(111)のシリコン基板上にエピタキシャル成長される。GaNの格子定数と、とシリコン(111)面の格子定数の差が、約17%と大きいのでめ、成長されたGaNには1010cm−2を超える転位が導入される。転位により、GaNを用いたトランジスタのリーク電流が増大する。また、トランジスタの移動度が低下する。

【解決手段】シリコン基板と、シリコン基板の(150)面上に、エピタキシャル成長された窒化物半導体層と、を備える半導体基板を提供する。

(もっと読む)

半導体装置及びその製造方法、電源装置

【課題】耐湿性及び耐電圧性を確保しながら、デバイス特性が劣化しないようにする。

【解決手段】半導体装置を、キャリア走行層及びキャリア供給層を含む窒化物半導体積層構造を備える半導体チップ1と、半導体チップの表面を覆い、カップリング剤を含有する第1樹脂層5と、第1樹脂層の表面を覆い、界面活性剤を含有する第2樹脂層6と、第1樹脂層及び第2樹脂層で覆われた半導体チップを封止する封止樹脂層7とを備えるものとする。

(もっと読む)

p型のIII族窒化物半導体層を含む半導体装置とその製造方法

【課題】p型のIII族窒化物半導体層を含む積層構造を利用して複数個の半導体装置を製造し、エッチング等して個々の半導体装置に分割すると、個々の半導体装置の側面に露出するp型のIII族窒化物半導体層の表面に沿ってリ−ク電流が流れてしまう。

【解決手段】p型のIII族窒化物半導体層8を含む積層構造の表面または裏面からp型のIII族窒化物半導体層8に達しない深さまでエッチングまたはダイシングし、残った厚みをへき開して個々の半導体装置に分割する。半導体装置の側面に露出するp型のIII族窒化物半導体層8の表面はへき開面となり、結晶欠陥が少なく、側面に沿ってリ−ク電流が流れることを防止する。

(もっと読む)

半導体素子

【課題】低オン抵抗および高信頼性を有する半導体素子を提供する。

【解決手段】半導体素子1Aは、第1導電形層11が表面に選択的に設けられた半絶縁性基板10と、前記半絶縁性基板および前記第1導電形層の上に設けられたノンドープAlXGa1−XN(0≦X<1)を含む第1半導体層15と、前記第1半導体層上に設けられたノンドープもしくは第2導電形のAlYGa1−YN(0<Y≦1、X<Y)を含む第2半導体層16とを備える。半導体素子は、前記第2導電形層11に接続された第1主電極20と、前記第2半導体層16に接続された第2主電極と21、前記第1主電極と、前記第2主電極と、のあいだの前記第2半導体層の上に設けられた制御電極30とを備える。前記第1導電形層11は、前記制御電極30の下に設けられている。

(もっと読む)

半導体装置、及びその製造方法

【課題】低消費電力・低電圧動作で、高利得・低歪特性を有し、かつ低コスト化が実現可能な半導体装置とその製造方法を提供する。

【解決手段】本発明に係る半導体装置のpチャネルFET2は、ソース/ドレインを形成する高濃度p型半導体層33と、その直下層に配設された低濃度p型半導体層32と、高濃度p型半導体層33上に形成された第1電極層41と、低濃度p型半導体層32の下方に形成され、ゲートとなる高濃度n型半導体層22と、その上に形成された第2電極層42とを備える。nチャネルFET3は、ソース/ドレインを形成する高濃度n型半導体層22と、ゲートを形成する高濃度p型半導体層33と、その下方に形成された低濃度n型半導体層21と、第1電極層42と、第2電極層42とを備える。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート電圧が閾値近傍に近づくときに発生する過剰なドレイン電流を抑制する。

【解決手段】トレンチ6の先端部に形成されたn-型チャネル層7がトレンチ6の長辺に位置する部分よりも膜厚が厚くなるため、そのトレンチ6の先端部においてJFET構造が構成されないようにする。例えば、トレンチ6の先端部をp+型領域20にて埋め尽くすようにする。これにより、トレンチ6の先端部のJFET構造の閾値がトレンチ6の長辺に位置する部分のJFET構造の閾値からずれることによる影響を受けることがない。したがって、ゲート電圧が閾値近傍に近づくときに発生する過剰なドレイン電流を抑制できる構造のSiC半導体装置とすることが可能となる。

(もっと読む)

半導体デバイスの製造方法およびエピタキシャル成長用の支持基板

【課題】中間層の一部が露出している支持基板であっても、それに適切な処理を加えることにより、半導体デバイスを歩留まりよく製造することができる半導体デバイスの製造方法およびエピタキシャル成長用の支持基板を提供する。

【解決手段】本半導体デバイスの製造方法は、少なくとも1層のIII族窒化物半導体層40をエピタキシャル成長させることができる下地基板10と、下地基板10上に全面的に配置された中間層20と、中間層20上に部分的に配置されたGaN層30aとを含み、GaN層30aと中間層20の一部とが露出している支持基板2を形成する工程と、支持基板2の中間層20が露出している部分20p,20q,20rを選択的に除去することにより、下地基板10の一部を露出させる工程と、GaN層30a上に、III族窒化物半導体層をエピタキシャル成長させる工程と、を備える。

(もっと読む)

21 - 40 / 273

[ Back to top ]