Fターム[5F102GR09]の内容

接合型電界効果トランジスタ (42,929) | 素子構造 (2,911) | 半導体基体内に付加領域を設けたもの (876) | 絶縁領域(高抵抗領域を含む) (273)

Fターム[5F102GR09]に分類される特許

41 - 60 / 273

半導体装置

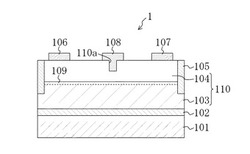

【課題】電流コラプスの発生を抑制できるIII族窒化物半導体トランジスタおよびその製造方法を提供する。

【解決手段】FET1では、第1窒化物半導体層103の上に第2窒化物半導体層104が設けられ、少なくとも一部が第2窒化物半導体層104に接するようにソース電極106およびドレイン電極107が設けられている。第2窒化物半導体層104の上面においてソース電極106とドレイン電極107との間に位置するように凹部110aが形成されており、ゲート電極108が凹部110aの開口を覆うように凹部110aの上方に設けられている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】耐圧が高く破壊等が生じにくい、信頼性の高い半導体装置を提供する。

【解決手段】基板上に形成された第1の半導体層12と、前記第1の半導体層上に形成された第2の半導体層14と、所定の領域の前記第2の半導体層の一部または全部を除去することにより形成されているゲートリセス22と、前記ゲートリセス及び第2の半導体層上に形成されている絶縁膜31と、前記ゲートリセス上に絶縁膜を介して形成されているゲート電極32と、前記第1の半導体層または前記第2の半導体層上に形成されているソース電極33及びドレイン電極34と、を有し、前記ゲートリセスの底面は、中央部分23aが周辺部分23bに対し高い形状であることを特徴とする半導体装置。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート絶縁膜における電荷トラップを大幅に低減し、信頼性の高い化合物半導体装置を実現する。

【解決手段】化合物半導体層2と、化合物半導体層2上でゲート絶縁膜6を介して形成されたゲート電極7とを備えており、ゲート絶縁膜6は、SixNyを絶縁材料として含有しており、SixNyは、0.638≦x/y≦0.863であり、水素終端基濃度が2×1022/cm3以上5×1022/cm3以下の範囲内の値とされたものである。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】GaN系の材料により形成されるHEMT(高電子移動度トランジスタ)をノーマリーオフ化させる。

【解決手段】基板11上に形成された第1の半導体層12と、前記第1の半導体層上に形成された第2の半導体層13と、所定の領域の前記第2の半導体層の一部または全部を除去することにより形成されているゲートリセス22と、前記ゲートリセス及び第2の半導体層上に形成されている絶縁膜31と、前記ゲートリセス上に絶縁膜を介して形成されているゲート電極32と、前記第1の半導体層または前記第2の半導体層上に形成されているソース電極33及びドレイン電極34と、を有し、前記ゲートリセスが形成されている領域における前記第2の半導体層、または、前記第2の半導体層及び前記第1の半導体層にはフッ素が含まれているフッ素を含む領域24を有する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート絶縁膜のダングリングボンドを確実に低減させて閾値電圧の変動を抑えて安定化させ、高いトランジスタ特性を得ることができる信頼性の高い化合物半導体装置を実現する。

【解決手段】ゲート電極7は、化合物半導体層2に形成された電極溝2C内に、ゲート絶縁膜6を介して一部が電極材料で埋め込まれて形成されており、ゲート絶縁膜6は、電極溝2C内において、少なくとも化合物半導体層2との界面に形成されたフッ素化合物を含有するAl−F化合物の複合層13aを有している。

(もっと読む)

半導体装置及びその製造方法、電源装置

【課題】半導体装置において、セルフターンオンが発生しないようにし、安定した動作を実現する。

【解決手段】半導体装置を、基板1と、基板の上方に設けられ、電子走行層6及び電子供給層7を含む半導体積層構造2と、半導体積層構造の上方に設けられたゲート電極3、ソース電極4及びドレイン電極5と、ゲート電極、ソース電極及びドレイン電極の上方に設けられ、ゲート電極、ソース電極及びドレイン電極のそれぞれに接続されたゲートパッド10、ソースパッド11及びドレインパッド12と、ゲートパッド、ソースパッド及びドレインパッドの下方に設けられた導電層1とを備えるものとし、ゲートパッドとソースパッドとの間の距離を、ゲートパッドとドレインパッドとの間の距離よりも小さくする。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】化合物半導体層の表面におけるダングリングボンドを確実に低減させて閾値電圧の変動を抑えて安定化させ、高いトランジスタ特性を得ることができる信頼性の高い化合物半導体装置を実現する。

【解決手段】電極溝2Cの内壁面を含む化合物半導体層2の表面は、電極溝2Cを形成する際のドライエッチングによるエッチング残渣物12a及び変質物12bが除去されて、化合物半導体がフッ素(F)で終端されており、この電極溝2Cをゲート絶縁膜6を介してゲートメタルで埋め込み、或いは電極溝2Cを直接的にゲートメタルで埋め込んで、ゲート電極7が形成される。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】化合物半導体層を加工することなく、比較的簡素な構成で確実なノーマリ・オフ動作を得ることができる信頼性の高い化合物半導体装置を実現する。

【解決手段】化合物半導体層2上にAlN等の第1の膜6及びAl2O3等の第2の膜7を順次に積層形成し、第2の膜7のゲート電極の形成予定部位に開口7aを形成し、開口7aをゲートメタルの一部で埋め込むように、ゲート電極8を形成し、ゲート電極のオフ時には、化合物半導体層2の電子走行層2bの2DEGがゲート電極8下の領域のみで消失する。

(もっと読む)

へテロ接合電界効果型トランジスタ及びその製造方法

【課題】本発明は、電流コラプスを抑制し、且つゲートリーク電流を低減するヘテロ接合電界効果型トランジスタとその製造方法の提供を目的とする。

【解決手段】本発明のヘテロ接合電界効果型トランジスタは、バリア層4及びバリア層4上に形成されたキャップ層5を含む窒化物半導体層と、前記窒化物半導体層に下部を埋没するようにして窒化物半導体層上に設けられたゲート電極10と、ゲート電極10の両側に離間して夫々設けられたドレイン電極8及びソース電極9とを備える。ゲート電極10のドレイン電極8側端面とソース電極9側端面のうち少なくともドレイン電極8側端面は、キャップ層5と少なくとも部分的に乖離しており、当該乖離部分が空隙である。

(もっと読む)

窒化物半導体装置

【課題】ゲート電極から染み出した金属がドレイン電極に到達することを抑制して、ドレイン−ゲート間の絶縁破壊を抑制する窒化物半導体装置を提供する。

【解決手段】ゲート電極5の直下に位置するAlGaN層22と、このAlGaN層22の直上に位置する絶縁膜30との間の界面Sに、ゲート電極5とドレイン電極1との間に位置するように、溝50を設けている。ゲート電極5から界面Sを伝ってドレイン電極1側へ染み出した金属を、溝50によって、堰き止めることができる。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】BiFETデバイスに含まれるFETのオン抵抗の悪化を抑制する。

【解決手段】共通基板1上に第1SL10及び第2SL20積層体が順に形成された半導体装置であって、第2積層体が除去されて残存する第1積層体は、電界効果型トランジスタを構成し、第1積層体上に積層された第2積層体は、電界効果型トランジスタとは異なる素子(バイポーラトランジスタ)を構成し、電界効果型トランジスタを構成する第1積層体は、第1積層体に形成されるリセスの停止位置を規定し、かつInGaPから成るエッチング停止層10と、リセス内に配置されるゲート電極25の下方に配置され、かつAlGaAsから成る下部化合物半導体層8と、エッチング停止層10と下部化合物半導体層8との間に挿入され、エッチング停止層に含まれるリンが下部化合物半導体層まで熱拡散し、下部化合物半導体層を構成する元素と化合することを抑止するスペーサ層9とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】 開口部が設けられ、当該開口部に二次元電子ガスで形成されるチャネルを備える縦型半導体装置の耐圧性能を向上させることを目的とする。

【解決手段】 GaN系積層体15は、n−型GaNドリフト層4/p型GaNバリア層6/n+型GaNコンタクト層7、を有し、開口部28は表層からn−型GaNドリフト層4内にまで届いていて、開口部の壁面および底部を覆うように位置する、電子走行層22および電子供給層26を含む再成長層27と、開口部の周囲に位置するソース電極Sと、開口部の再成長層上に位置するゲート電極Gと、開口部の底部に位置する底部絶縁膜37とを備えることを特徴とする。

(もっと読む)

高周波スイッチおよび高周波モジュール

【課題】挿入損失およびチップサイズの増大を生じることなく、歪特性に優れた高周波スイッチおよび高周波モジュールを提供する。

【解決手段】高周波スイッチであって、高周波信号を入出力するための複数の入出力端子101〜103と、2つの入力端子101、103間に設けられた基本スイッチ部104、105と、基本スイッチ部104、105の導通および遮断を制御するための制御電圧が入力される制御端子106、107とを備え、基本スイッチ部104、105は、メアンダ形状のゲート電極を有するメアンダ型のFET110〜113及びFET120〜123が多段に接続されて形成され、FET110〜113、及び120〜123のうち、入出力端子103からの電気的距離が最も短いFET113、及び120のフィンガー長は、他のFET110〜112、及び121〜123のフィンガー長よりも短い。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ファインゲート構造を採用してゲート電極の微細化を図るも、ゲート電極の周辺における電界集中によるデバイス特性の変動・劣化を防止する、信頼性の高い化合物半導体装置を実現する。

【解決手段】ゲート電極8は、ファインゲート構造の幹状の下方部分8aと、下方部分8aの上端から当該上端よりも幅広に傘状(オーバーハング形状)に拡がる上方部分8bとが一体形成されており、下方部分8aは、下端を含む第1の部分8aaと、第1の部分8aa上の第2の部分8abとを有し、保護壁7は、第1の部分8aaの両側面のみを覆うように形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】開口部にチャネルを備える縦型半導体装置において、高周波特性を向上することができる半導体装置およびその製造方法を提供する。

【解決手段】 n型GaN系ドリフト層4/p型GaN系バリア層6/n型GaN系コンタクト層7、を有し、開口部28は表層からn型GaN系ドリフト層内にまで届いており、該開口部を覆うように位置する電子走行層22および電子供給層26を含む再成長層27と、ソース電極Sと、ドレイン電極Dと、再成長層上に位置するゲート電極Gとを備え、ソース電極を一方の電極とし、またドレイン電極を他方の電極としてコンデンサを構成するとみて、該コンデンサの容量を低下させる容量低下構造を備えることを特徴とする。

(もっと読む)

半導体装置

【課題】化合物半導体上のp型チャネルFETにおいてオン抵抗を低くすることの可能な半導体装置を提供する。

【解決手段】化合物半導体からなる基板10上に、n型チャネルFET領域2とp型チャネルFET領域3とが併設されている。p型チャネルFET領域3において、チャネル層16の下面に接するバッファ層15が、チャネル層16よりも広いバンドギャップを有する第2バッファ層15Bだけで構成された単層構造となっている。さらに、第2バッファ層15Bは、チャネル層16と電子走行層13との間に設けられている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】比較的短い製造時間で容易且つ確実に反りのない基板を得ることを可能とし、低コストで信頼性の高い高耐圧及び高出力の化合物半導体装置を実現する。

【解決手段】Si基板10上に、AlNからなる第1のバッファ層2と、AlGaNのAl組成比率が均一となるように形成された均一組成領域3aと、第2のバッファ層3の上面に近づくにつれてAlGaNのAl組成比率が徐々に高くなるように形成された傾斜組成領域3bとが積層されてなる第2のバッファ層3とが形成され、第2のバッファ層3上に電子走行層4及び電子供給層6等が形成されてAlGaN/GaN・HEMTが構成される。

(もっと読む)

半導体装置

【課題】本発明は、オーバーシュートの発生を減少することができ、素子破壊を防止することができるとともに、スイッチング動作速度の高速化を実現することができるスイッチング素子を備えた半導体装置を提供する。

【解決手段】半導体装置1は、第1の半導体層31と、第2の半導体層32と、二次元キャリアガス層33と、第1の主電極41と、第2の主電極42と、第1のゲート電極51と、第2のゲート電極52とを備える。第1のゲート電極51は、第1の主電極41の一部と対向する第2の主電極42の一部との間に配設される。第2のゲート電極52は、第1の主電極41の他の一部と対向する第2の主電極42の他の一部との間において、第1のゲート電極51との間に分離領域6を介在し配設され、第1のゲート電極51に対して独立に制御される。

(もっと読む)

熱スペーサを有する半導体デバイス

【課題】放熱スペースが短縮された、複数のユニットセルを有する高出力高周波半導体デバイスを提供する

【解決手段】ユニットセルは各々、制御電極24と、第1及び第2の被制御電極20,22とを有する。熱スペーサ(すなわち、電気的に不活性な領域)40が、これらのユニットセルのうち少なくとも1つを第1の活性部分及び第2の活性部分50に分割し、第2の活性部分は、この熱スペーサにより第1の部分から離隔される。ユニットセルの制御電極ならびに第1及び第2の被制御電極は、第1の熱スペーサを横切っている。

(もっと読む)

半導体装置

【課題】オフ時のリーク電流を低減し、パワースイッチング素子に適用可能なノーマリーオフ型の半導体装置を提供する。

【解決手段】基板101と、基板101の上に形成されたアンドープGaN層103と、アンドープGaN層103の上に形成されたアンドープAlGaN層104と、アンドープGaN層103又はアンドープAlGaN層104の上に形成されたソース電極107及びドレイン電極108と、アンドープAlGaN層104の上に形成され、ソース電極107とドレイン電極108との間に配置されたp型GaN層105と、p型GaN層105の上に形成されたゲート電極106とを備え、アンドープGaN層103は、チャネルを含む活性領域113と、チャネルを含まない不活性領域112とを有し、p型GaN層105は、ソース電極107を囲むように配置されている。

(もっと読む)

41 - 60 / 273

[ Back to top ]