Fターム[5F102GS09]の内容

接合型電界効果トランジスタ (42,929) | ゲート電極構造 (2,097) | 平面形状 (492) | 櫛歯状、蛇行状 (270)

Fターム[5F102GS09]に分類される特許

101 - 120 / 270

半導体装置およびその製造方法

【課題】 チャネルの高い移動度を得ながら、かつ、縦方向耐圧およびゲート電極端における耐圧の両方の耐圧性能を確実に得ることができる、半導体装置およびその製造方法を提供する。

【解決手段】 n型ドリフト層および該n型ドリフト層上に位置するp型層を含むGaN系積層体に、開口部が設けられ、開口部を覆うように位置する、チャネルを含む再成長層と、再成長層に沿って該再成長層上に位置するゲート電極とを備え、開口部はn型ドリフト層に届いており、ゲート電極の端は、平面的に見てp型層から外れた部分がないように位置していることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 サージ電圧等に対するバイパス用の保護部を備え、耐圧性能および低いオン抵抗(低いオン電圧)を実現し、かつ、構造が簡単な、大電流用の、半導体装置およびその製造方法を提供する。

【解決手段】 支持基体上にオーミック接触するGaN層を有するn+型GaN基板1と、第1領域R1上におけるn−型GaNドリフト層2を有するFETと、第2領域R2においてn−型GaNドリフト層2にショットキー接触するアノード電極を有するSBDとを備え、FETとSBDとは並列配置されており、n+型GaN基板1の裏面に、FETのドレイン電極DおよびSBDのカソード電極Cを備えることを特徴とする。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】複数に分割された接続部とこれらの接続部の間に形成された抵抗体とが、電極パッドにより良好に接続される半導体装置の製造方法を提供すること。

【解決手段】複数のFET12が化合物半導体基板11上に並列に形成され、ゲートパッド27が複数に分割された半導体装置の製造方法であって、化合物半導体基板11上に抵抗体22を形成する工程と、抵抗体22上にこの抵抗体22を保護する保護パターン23を形成する工程と、複数のFET12、抵抗体22および保護パターン23を含む化合物半導体基板11上に保護膜24を形成する工程と、複数のFET12の各電極13、14、15をそれぞれ接続する電極接続部17、18、21上および保護パターン23上の保護膜24をエッチングにより除去する工程と、エッチングにより除去した位置に電極パッド25、26、27を形成する工程と、を具備する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】本発明は、化合物半導体素子の動作に関係なく、リーク電流を防止することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置1は、2DEG310を有する第1の化合物半導体層31と、第1の化合物半導体層31上に配設され、キャリア供給層として機能する第2の化合物半導体層32と、2DEG310上に配設された第1の電極61と、2DEG310上において第1の電極61から離間して配設された第2の電極42と、を備えた化合物半導体素子10と、化合物半導体素子10の周囲を取り囲む領域の一部において2DEG310上に配設され、この2DEG310のキャリア濃度を低減させる外周電極62を有する外周領域11とを備える。

(もっと読む)

電界効果トランジスタ

【課題】蛇行した形状に形成されたリセス部を備えることにより、オン抵抗を低減することができる電界効果トランジスタを提供することを目的とする。

【解決手段】電界効果トランジスタ1は、チャネル層11と、チャネル層11とヘテロ接合を構成するキャリア供給層12と、キャリア供給層12の表面から掘り下げて形成されたリセス部13と、リセス部13に沿って形成された第1絶縁層31と、第1絶縁層31の上に形成された第1ゲート電極23と、リセス部13に対してチャネル長方向の一方側に形成されたソース電極21と、リセス部13に対してチャネル長方向の他方側に形成されたドレイン電極22とを備える。リセス部13は、ソース電極21とドレイン電極22とが平面視で平行に対向するチャネル長の範囲内において、蛇行しながらチャネル長方向と交差する方向に延長されている。

(もっと読む)

半導体装置及びその製造方法

【課題】放熱性に優れ、製造歩留まりの向上を図ることができる半導体装置及びその製造方法を提供することを目的とする。

【解決手段】

半導体装置は、基板1の上方に設けられた化合物半導体層2,3,4と、化合物半導体層2,3,4の上方に設けられた複数のソース電極7及び複数のドレイン電極9と、化合物半導体層2,3,4を貫通し、複数のソース電極7のそれぞれに接続される複数のビア配線22と、化合物半導体層2,3,4を貫通し、複数のドレイン電極9のそれぞれに接続される複数のビア配線23と、複数のビア配線22に接続され、基板1に埋め込まれたソース共通配線18と、複数のビア配線23に接続され、基板1に埋め込まれたドレイン共通配線20とを有する。

(もっと読む)

半導体装置

【課題】静電破壊対策においてペレットサイズに影響を与えず、かつレイアウトに影響されない構成とする。

【解決手段】FET領域200に形成されたFETと、周囲領域202において、基体表面に形成された第1の不純物拡散領域106aと、それぞれ第1の不純物拡散領域106aの一端107aおよび他端107b上に形成された第1のオーミックメタル端子114aおよび第2のオーミックメタル端子114dとを含むゲート抵抗107と、平面視において、ゲート抵抗107の一端107aとゲート電極122との間には、ドレイン不純物拡散領域106bおよびドレイン電極114bの組合せ、またはソース不純物拡散領域106cおよびソース電極114cの組合せの一方が存在し、当該組合せの一方は、ゲート抵抗107の一端107aと他端107bとを結ぶ直線を遮るように、FET領域200から延在して形成された遮断部134を含む。

(もっと読む)

半導体素子およびその製造方法

【課題】より高いブレークダウン電圧に適した半導体素子構造およびその製造方法を提供する。

【解決手段】半導体基板構造(100)は、半導体基板(1)と、半導体基板(1)の上部にGaNタイプの層スタック(20)とを備える。GaNタイプ層スタック(20)は、少なくとも1つのバッファ層(21,22)と、第1活性層(2)と、第2活性層(3)とを備え、第1活性層と第2活性層の界面において、能動素子領域が規定可能である。半導体基板(1)は、絶縁層(12)の上に存在しており、所定のパターンに従って溝(14)を規定するようにパターン化され、そのパターンは、こうした能動素子領域の下地となる少なくとも1つの溝(14)を含み、前記溝(14)は、絶縁層(12)から、GaNタイプ層スタック(20)の少なくとも1つのバッファ層(21,22)の中まで延びて、前記少なくとも1つのバッファ層(22)の範囲で過成長しており、第1および第2活性層(2,3)は、少なくとも能動素子領域の範囲で連続している。

(もっと読む)

半導体装置及びその製造方法

【課題】放熱性に優れ、高周波高出力で使用可能な、化合物半導体高電子移動度トランジスタを提供する。

【解決手段】支持基板20の第1の主表面20a上に、チャネル層40及びバリア層50が積層されて構成される、化合物半導体高電子移動度トランジスタであって、ソース電極62が形成された領域を含む、支持基板の領域部分が金属部22であり、ドレイン電極64が形成された領域を含む、支持基板の他の領域部分がシリコン部24で構成される。

(もっと読む)

半導体装置

【課題】ソースフィールドプレート電極を形成することによる性能の劣化を抑制することができる半導体装置を提供すること。

【解決手段】SiC基板11上にGaN層12およびAlGaN層13がこの順で形成され、AlGaN層13上にドレイン電極14、ソース電極15およびゲート電極16が形成された半導体装置であって、ゲート電極16の下方には、SiC基板11を貫通するように第1の開口23が形成されている。さらに、GaN層12上に形成され、ソース電極15に接続されるソースパッド19の一部が、SiC基板11の裏面側から露出するように、第2の開口24が形成されている。そして、第1の開口23内にソースフィールドプレート電極25−1を形成すると同時に、第2の開口24から露出するソースパッド19に接触するようにSiC基板11の裏面に接地導体25−2を形成する。

(もっと読む)

窒化物半導体装置

【課題】パッシベーション膜を形成した場合にも、界面リーク電流が抑制された窒化物半導体装置を実現できるようにする。

【解決手段】窒化物半導体装置は、基板101の上に形成された半導体層積層体102と、半導体層積層体102の上に互いに間隔をおいて形成された第1のオーミック電極131及びショットキー電極132と、半導体層積層体102の上を覆うパッシベーション膜141とを備えている。半導体層積層体102は、基板101の上に順次形成された第1の窒化物半導体層122、第2の窒化物半導体層123及びp型の第3の窒化物半導体層124を含む半導体層積層体102と有している。第3の窒化物半導体層141は、p型の不純物を含み第1のオーミック電極131とショットキー電極132との間に形成され且つショットキー電極132と接するように選択的に形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】気泡の発生を防止し、熱抵抗を低減化する半導体装置を提供する。

【解決手段】基板10表面上に配置された窒化物系化合物半導体層12と、窒化物系化合物半導体層上に配置された活性領域AAと、活性領域上に配置され、それぞれ複数のフィンガーを有するゲート電極24、ソース電極20およびドレイン電極22と、ゲート電極、ソース電極およびドレイン電極が延伸する方向の窒化物系化合物半導体層上に配置され、ゲート電極、ソース電極およびドレイン電極ごとにフィンガーをそれぞれ束ねて形成したゲート端子電極GE、ソース端子電極SEおよびドレイン端子電極DEと、ソース端子電極の下部に配置されたVIAホールCSと、基板10裏面に配置され、ソース端子電極に対してVIAホールを介して接続された裏面金属層BEと、基板の裏面のVIAホールからソース端子電極が配置される基板端に渡って設けられた溝SCとを備える。

(もっと読む)

化合物半導体装置の製造方法

【課題】基板の付け替えに際して基板を適切に分離することができる化合物半導体装置の製造方法を提供する。

【解決手段】基板の上方に、第1のバンドギャップのAlxGa1-xN(0≦x<1)を含む第1の化合物半導体層を形成する。前記第1の化合物半導体層上に、前記第1のバンドギャップよりも広い第2のバンドギャップのAlyInzGa1-y-zN(0<y<1、0<y+z≦1)を含む第2の化合物半導体層を形成する。前記第2の化合物半導体層の上方に、化合物半導体積層構造を形成する。前記第1のバンドギャップと前記第2のバンドギャップとの間のエネルギを有する光を前記第1の化合物半導体層に照射しながら前記第1の化合物半導体層を除去して、前記基板を前記化合物半導体積層構造から分離する。

(もっと読む)

半導体装置およびその製造方法

【課題】 サージ電圧等に対するバイパス用の保護部を備え、耐圧性能および低いオン抵抗(低いオン電圧)を実現し、かつ、構造が簡単な、大電流用の、半導体装置およびその製造方法を提供する。

【解決手段】 支持基体上にオーミック接触するGaN層を有するn+型GaN基板1と、第1領域R1上におけるn−型GaNドリフト層2を有するFETと、第2領域R2においてn−型GaNドリフト層2にショットキー接触するアノード電極を有するSBDとを備え、FETとSBDとは並列配置されており、n+型GaN基板1の裏面に、FETのドレイン電極DおよびSBDのカソード電極Cを備えることを特徴とする。

(もっと読む)

電界効果トランジスタ、電界効果トランジスタの製造方法及び通信装置

【課題】オン抵抗の上昇を抑制し、かつ、オフ容量を低減することができる電界効果トランジスタ、電界効果トランジスタの製造方法及び通信装置を提供する。

【解決手段】化合物半導体基板10の一面側に、バッファ層11、下部ドーピング層12、下部スペーサ層13、チャネル層14、上部スペーサ層15、上部ドーピング層16、拡散層17をこの順に積層し、拡散層17上の一部にゲート電極18、ソース電極19及びドレイン電極20を形成する。また、ゲート電極18とソース電極19及びドレイン電極20との間の領域にそれぞれ所定の間隔d2,d3を空けてp型半導体層21を形成すると共に、拡散層17のうちゲート電極18直下の部分にゲート領域23を形成する。

(もっと読む)

半導体装置

【課題】本発明は、絶縁領域において破壊が起こるのを防止できる半導体装置を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、半導体基板と、前記半導体基板の上面側に設けられた不純物添加領域と、前記半導体基板の上面側において、イオン注入によって前記不純物添加領域の周囲に設けられた絶縁領域と、前記不純物添加領域上に設けられたゲート電極と、前記ゲート電極を挟むように前記不純物添加領域上に設けられた第1の電極及び第2の電極と、前記絶縁領域上に設けられ、前記ゲート電極に接続した第1のパッドと、前記絶縁領域上において前記不純物添加領域を挟んで前記第1のパッドと対向するように設けられ、前記第2の電極に接続した第2のパッドと、前記絶縁領域上において、前記第1の電極と前記第2のパッドの間に設けられた導体と、を備えることを特徴とするものである。

(もっと読む)

電力変換装置

【課題】電流コラプスを十分に緩和し、GaNトランジスタが本来有している低いオン抵抗を利用した高効率の電力変換装置を実現できるようにする。

【解決手段】電力変換装置は、電源が接続される入力端Vin1と、電源から供給された電力をスイッチングする第1のスイッチング素子10とを備えている。第1のスイッチング素子10は、基板11の上に形成された窒化物半導体からなる半導体層積層体13と、半導体層積層体13の上に形成されたゲート電極18、第1のオーミック電極16及び第2のオーミック電極17と、基板11の裏面に形成された裏面電極20とを有している。裏面電極20には第2のオーミック電極17との間の電位差が小さくなるように入力端Vin1に接続された電源から電位が供給される。第1のスイッチング素子10がオン状態の場合には、裏面電極20に正電圧のバイアスが印加される。

(もっと読む)

電界効果トランジスタ、及び電界効果トランジスタの製造方法

【課題】電界効果トランジスタの局所的な温度を測定することが可能な電界効果トランジスタを提供することである。

【解決手段】本発明にかかる電界効果トランジスタは、半導体層5と、半導体層5とオーミック接合したソース電極1と、半導体層5とオーミック接合したドレイン電極2と、半導体層5とショットキ接合したゲート電極3と、ソース電極1の一部に形成された空隙に設けられた、半導体層5とショットキ接合したショットキ電極4と、を有する。また、本発明にかかる他の態様の電界効果トランジスタは、半導体層5と、半導体層5とオーミック接合したソース電極1と、半導体層5とオーミック接合したドレイン電極2と、半導体層5とショットキ接合したゲート電極1と、ドレイン電極2の一部に形成された空隙に設けられた、半導体層5とショットキ接合したショットキ電極4と、を有する。

(もっと読む)

窒化物半導体素子

【課題】本発明は、過電圧印加時に電圧クランプ機能を有する窒化物半導体素子を提供することを目的とする。

【解決手段】第1の窒化物半導体からなる第1の層と、第1の層の上に設けられ、第1の窒化物半導体よりもバンドギャップが大なる第2の窒化物半導体からなる第2の層と、第2の層に電気的に接続された第1の電極と、第2の層の上に設けられ、第1の方向において第1の電極と並設された第2の電極と、第2の層の上に設けられたフローティング電極と、を備え、フローティング電極は、第1の方向に直交する第2の方向において第2の電極に挟まれた部分と、第1の電極に向けて第2の電極よりも突出した部分と、を有することを特徴とする窒化物半導体素子。

(もっと読む)

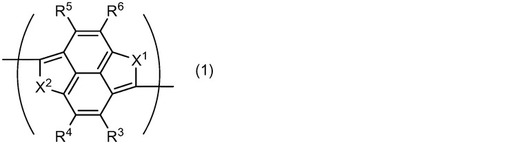

有機薄膜トランジスタ、面状光源及び表示装置

【課題】優れた電界効果移動度を得ることができる有機薄膜トランジスタを提供する。

【解決手段】下式で表される繰り返し単位を有する高分子化合物を含む有機半導体層を備える、有機薄膜トランジスタ。 (もっと読む)

(もっと読む)

101 - 120 / 270

[ Back to top ]