Fターム[5F102GS09]の内容

接合型電界効果トランジスタ (42,929) | ゲート電極構造 (2,097) | 平面形状 (492) | 櫛歯状、蛇行状 (270)

Fターム[5F102GS09]に分類される特許

81 - 100 / 270

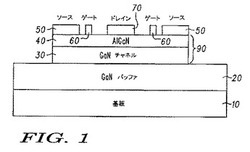

ハイパワーGaNベースFET用のレイアウトデザイン

【課題】FETを提供する。

【解決手段】FETは、基板と、基板上に配置されたバッファ層と、バッファ層上に配置されたチャネル層と、チャネル層上に配置された障壁層とを含む。ソース、ゲート及びドレイン電極は障壁層上に配置されて長手方向に延伸する。チャネル及び障壁層の一部分は長手方向に延伸するメサ部を形成し、ソース及びドレイン電極がメサ部の縁を超えて延伸する。ゲート電極はメサ部の縁側壁に沿って延伸する。導電性ソース相互接続部は障壁層上に配置されソース電極に電気的に接続された第一の端部を有する。第一の誘電体層はバッファ層及びソース相互接続部上に配置される。ゲートビアは第一の誘電体層に形成される。導電性ゲートノードがバッファ層に沿って延伸して前記メサ部の側壁に沿って延伸するゲート電極の一部分に電気的に接続する。ゲートパッドはメサ部に隣接する第一の誘電体層上に配置される。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート電極の電位の位相差を抑制することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基板と、基板上方に形成された電子走行層と、電子走行層上方に形成された電子供給層と、電子供給層上方に形成された複数のゲート電極5gと、複数のゲート電極5gが接続されたゲートパッド8gと、が設けられている。ゲート電極5gのゲート幅がゲートパッド8gから離間するほど小さくなっている。

(もっと読む)

半導体装置

【課題】高周波モジュール中におけるスイッチング素子として用いられるHEMT素子を小型化する。

【解決手段】GaAsからなる基板1の主面上の素子分離部9で規定された活性領域内において、ゲート電極17は、1本で形成し、ソース電極13とドレイン電極14との間では紙面上下方向に延在し、それ以外の部分では左右方向に延在するようにパターニングすることにより、活性領域外に配置されるゲート電極17の割合を減じ、ゲートパッド17Aの面積を減じる。

(もっと読む)

接合型電界効果トランジスタ、その製造方法及びアナログ回路

【課題】外部ノイズの影響を低減できるJFETを提供する。

【解決手段】本発明に係るJFET50は、p型半導体基板1と、p型半導体基板1の表面に形成されているn型チャネル領域3と、n型チャネル領域3内に形成されており、n型チャネル領域3よりも不純物濃度の高いn型埋め込み領域4と、n型チャネル領域3の表面に形成されているp型ゲート領域6と、n型チャネル領域3の表面に、p型ゲート領域6を挟むように形成されているn型ドレイン/ソース領域7及びn型ドレイン/ソース領域8とを備え、n型埋め込み領域4は、n型ドレイン/ソース領域7及びn型ドレイン/ソース領域8の一方の下方に形成されており、他方の下方に形成されていない。

(もっと読む)

III族窒化物系高電子移動度トランジスタを含む低雑音増幅器

【課題】高い入力電力耐性と、低い雑音指数の両者を達成する低雑音増幅器を提供すること。

【解決手段】低雑音増幅器は、第一のIII族窒化物系トランジスタと、第一のIII族窒化物系トランジスタに結合された第二のIII族窒化物系トランジスタとを含んでいる。第一のIII族窒化物系トランジスタは、入力信号に対する第一増幅段を提供するように構成され、第二のIII族窒化物系トランジスタは、入力信号に対する第二増幅段を提供するように構成される。

(もっと読む)

電界効果トランジスタ、電界効果トランジスタの製造方法および電子装置

【課題】ゲートリーク電流の増加が抑制された信頼性の高い電界効果トランジスタを提供する。

【解決手段】 ゲート電極は、第1金属層16および第2金属層17を含み、

第2金属層17は、第1金属層16よりも導電率が高く、

第1金属層16の上方に、第2金属層17が積層され、

ソース電極18およびドレイン電極19は、半導体層12〜14上にオーム性接触し、

ゲート電極は、ソース電極18およびドレイン電極19の間に配置され、かつ、第1金属層16により半導体層上にショットキー性接触し、

半導体層上におけるソース電極18およびゲート電極の間、ならびに、ゲート電極およびドレイン電極19の間は、絶縁膜15Aにより覆われ、

かつ、

第2金属層17下面の全体が第1金属層16上面の上方に重なっているか、または、第1金属層16の厚みが絶縁膜15Aの厚み以上であることを特徴とする電界効果トランジスタ。

(もっと読む)

電界効果トランジスタ

【課題】スイッチング速度を向上でき、動作不良品を低減できる、横型の電界効果トランジスタを提供する。

【解決手段】ゲート配線43は、基部44と、基部44から突出する複数の指状部45と、隣接する指状部45の先端部46を接続する接続部47と、を有する。ゲート配線43の指状部45は、ソース配線23の指状部25とドレイン配線33の指状部35と、の間に配置されている。ゲート配線43の基部44は、ソース配線23の基部24とドレイン配線33の指状部35との間に配置され、かつ、ソース配線23の指状部25との間に絶縁膜を介在させて指状部25と交差している。

(もっと読む)

電界効果トランジスタ

【課題】ゲート電極を挟んで、一方にソース電極が形成され、他方にドレイン電極が形成され、ソース電極の下方にソースオーミックが形成され、ドレイン電極の下方にドレインオーミックが形成された電界効果トランジスタ(FET)であって、チャネル温度の上昇が抑制され、基板との間の寄生容量が低減され、ドレイン効率の温度依存性が抑制され、高温にて高効率動作が可能なFETを提供する。

【解決手段】FET20は、ドレイン電極22Dが互いに離間する複数のドレイン電極22Da、22Dbに分割されており、かつ、分割された複数のドレイン電極22Da、22Dbの下方に各々形成されたドレインオーミック26Da、26Db間に絶縁領域24Iが形成されたものである。

(もっと読む)

テラヘルツ波受信素子

【課題】テラヘルツ波を効率よく受信し、信号/雑音比を向上したテラヘルツ波受信素子を提供する。

【解決手段】第1の波長λ1のテラヘルツ波を受信するテラヘルツ波受信素子100であ

って、2以上の半導体層(バッファ層102aおよび電子供給層104a)のヘテロ接合により形成される2次元電子チャネル層103a、ゲート幅方向にλ1/2の長さを有するゲート電極111a、ドレイン電極113aおよびソース電極112aを有する第1のFET100aと、第1のFET100aのゲート電極111aのゲート幅方向における中央部と接続され、かつ、ゲート電極111aと直交するように配置されたゲート配線114aとを備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 電力等の信号の合成効率が高く、チップ占有面積を低減可能な半導体装置および半導体装置の製造方法を提供する。

【解決手段】 本発明の半導体装置10は、電極パッド11と、複数の信号伝送電極12a、12bおよび12cと、複数の伝送線路13、14および15とを有し、前記電極パッド11と前記各信号伝送電極12a、12bおよび12cとは、前記各伝送線路13、14および15により電気的に接続され、前記複数の伝送線路13、14および15の少なくとも一本は、その線路長が他の伝送線路14以上であり、前記線路長が他の伝送線路以上である伝送線路13および15は、その一部または全部が空中配線され、前記空中配線された伝送線路13aおよび15aが、マイクロストリップラインであることを特徴とする。

(もっと読む)

半導体装置

【課題】 本発明の目的は、半導体装置単体で負電源を必要とせずにスイッチングが可能な素子を提供することである。

【解決手段】 この発明の半導体装置は、ノーマリオンFETと、一方の電極を前記FETのゲートに、他方の電極を入力端子に電気的に接続されたキャパシタと、アノード電極が前記FETのゲートに、カソード電極が前記FETのソースに電気的に接続されたダイオードと、を前記FETと同一チップ上に形成したことを特徴としており、さらに、前記キャパシタが、前記FETのゲート引き出し電極上に誘電体などの絶縁膜を形成し、形成した前記絶縁膜に金属膜を形成することにより形成されたことが好ましい。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の表皮効果の抑制と低抵抗化を図る。

【解決手段】第1配線部41と、その第1配線部41の周りを被覆する、高融点金属窒化物を含む第2配線部42とを含む配線40aを形成する。このような配線40aにおける第2配線部42は、第1配線部41側から外周に向かって窒素含有率が高くなる部分を有するように形成する。これにより、配線40aにおける表皮効果が抑制されると共に、配線40aの低抵抗化が図られるようになる。

(もっと読む)

半導体装置

【課題】Ti、PtおよびAuからなるゲート電極を有するリセス構造を有し、Ti上のPt若しくはAuが、素子領域表面のAlGaAs層に拡散することを抑制する半導体装置を提供する。

【解決手段】GaAs基板11上に形成された素子領域16と、第1のリセス領域25と、第2のリセス領域26と、第1のリセス領域25外の素子領域16上に、互いに離間して形成されたドレイン電極13およびソース電極14と、第2のリセス領域26の表面の一部に接し、第1のリセス領域25の表面の一部に接するゲート電極15を具備し、最下層が、第1のリセス領域25、および第2のリセス領域26の表面の一部に接するように、隙間を有して形成された第1のTi層29と、第1のTi層29上に、第1のTi層29の隙間を埋めるように形成されたAl層30と、Al層30上に形成されたPt層32と、Pt層上に形成されたAu層33と、を含むように構成する。

(もっと読む)

電界効果トランジスタ

【課題】電流コラプスが抑制された窒化物半導体を用いた電界効果トランジスタを容易に実現できるようにする。

【解決手段】電界効果トランジスタは、基板100の上に形成され、第1の窒化物半導体層122及び第2の窒化物半導体層123を有する半導体層積層体102を備えている。半導体層積層体102の上には、互いに間隔をおいてソース電極131及びドレイン電極132が形成されている。ソース電極131とドレイン電極132との間には、ソース電極131及びドレイン電極132と間隔をおいてゲート電極133が形成されている。ドレイン電極132の近傍には正孔注入部141が形成されている。正孔注入部141は、p型の第3の窒化物半導体層142及び第3の窒化物半導体層142の上に形成された正孔注入電極143を有している。ドレイン電極132と正孔注入電極142とは、電位が実質的に等しい。

(もっと読む)

半導体装置

【課題】電流駆動型の半導体装置のゲートへの寄生インダクタンスによる外乱ノイズを低減し、ゲート駆動を高精度化及び安定化させる。

【解決手段】半導体装置100であって、電流駆動型の半導体素子3と、半導体素子3を制御するゲート駆動回路11と、接続端子部とを備え、半導体素子3は、窒化物半導体層の積層体の上に形成されたゲート電極パッド1と、オーミック電極パッド2及び5とを有し、接続端子部は、オーミック電極パッド2と接続されたオーミック電極端子6と、オーミック電極パッド5と接続されたオーミック電極端子10と、オーミック電極パッド2と接続されたゲート駆動用端子7と、ゲート電極パッド1と接続されたゲート端子8とを有し、ゲート駆動回路11の入力端子はゲート駆動用端子7に接続され、ゲート駆動回路11の出力端子はゲート端子8に接続され、ゲート駆動回路11の基準電位をオーミック電極パッド2の電位とする。

(もっと読む)

半導体装置

【課題】半絶縁性基板に形成されたゲートパッドにマイナスの電圧が印加され、半絶縁性基板の裏面に形成された裏面電極にプラスの電圧が印加されても、リーク電流を抑制できる半導体装置を提供する。

【解決手段】裏面電極10が形成された半絶縁性基板11の表面上に並列に形成された、複数のゲート電極15がゲート電極接続部21に接続されるとともに、このゲート電極接続部21が複数に分割された半導体装置であって、ゲート電極接続部21間の半絶縁性基板11の表面に形成されたn型の抵抗層22と、このn型の抵抗層22の周囲を覆うように、p型不純物層23と、このp型不純物層23の周囲を覆うように、所望の濃度で形成されたn型不純物層24と、を具備し、ゲートパッド29は、ゲート電極接続部21と、このゲート電極接続部21に隣接するn型の抵抗層22上の引き出し電極25とを接続するように形成される。

(もっと読む)

高周波半導体装置

【課題】FETセルごとに電源を用意・制御することなく、所望の出力電力値に合わせて、出力電力値を調整可能な高周波半導体装置を提供する。

【解決手段】分配・入力整合回路32と入力伝送線路パターン36とを搭載した分配・入力整合回路基板14と、複数の入力キャパシタセル40を搭載した入力キャパシタ基板16と、複数の電界効果トランジスタセルを搭載した半導体基板18と、複数の出力キャパシタセル41を搭載した出力キャパシタ基板20と、出力伝送線路パターン38と合成・出力整合回路34とを搭載した合成・出力整合回路基板22とを備え、所望の出力電力値に合わせて複数のセルからなる電界効果トランジスタのセル数を接続・非接続により、総ゲート電極長を実質的に変化させて、出力電力値を調整可能な高周波半導体装置30。

(もっと読む)

半導体装置およびその製造方法

【課題】炭化珪素基板を用いた接合型FETにおいて、ゲート・ソース間のpn接合領域において生じるリーク電流を低減する。

【解決手段】炭化珪素基板を用いたトレンチ型接合FETにおいて、トレンチ5の側壁および底面に窒素を導入することにより、トレンチ5の表面にn型層8およびn+型層9を形成する。これによりp+型ゲート領域4とn+型ソース領域3との接合領域であるpn接合領域はダメージの多いトレンチ5の側壁ではなく半導体基板21の主面において露出し、また、その露出する領域は狭まるため、pn接合領域におけるリーク電流を低減することができる。

(もっと読む)

半導体装置

【課題】保護素子の素子面積を小さく抑え且つ製造工程を複雑にすることなくサージ耐性が高い半導体装置を実現できるようにする。

【解決手段】半導体装置は、第1の素子領域106Aに形成された第1のトランジスタ111と、第2の素子領域106Bに形成された第2のトランジスタ121を含む第1の保護素子とを備えている。第2の保護素子オーミック電極123Bは第1のゲート電極115と接続され、第1の保護素子オーミック電極123Aは第1のオーミック電極113Aと接続され、第1の保護素子ゲート電極115は、第1の保護素子オーミック電極123A及び第2の保護素子オーミック電極123Bの少なくとも一方と接続されている。第2の素子領域106Bの面積は、第1の素子領域106Aよりも小さい。

(もっと読む)

電界効果トランジスタ、電子装置、電界効果トランジスタの製造方法及び使用方法

【課題】 チップ面積を大きくし過ぎることなく、過電圧、過電力が加わっても破壊されない電界効果トランジスタを提供する。

【解決手段】 本発明の電界効果トランジスタは、

半導体層上に、ゲート電極110と、ドレイン電極109と、ソース電極108と、保護ダイオード(保護ダイオード電極)111とが配置され、

ドレイン電極109が、保護ダイオード111の周囲の一部もしくは全部を囲む状態で形成されているか、または、

ドレイン電極109は、複数であり、複数のドレイン電極109の少なくとも一対のドレイン電極間に、保護ダイオード111が配置されるように形成されていることを特徴とする。

(もっと読む)

81 - 100 / 270

[ Back to top ]