Fターム[5F102HC02]の内容

接合型電界効果トランジスタ (42,929) | 個別プロセス (4,778) | エピタキシャル成長(分子線エピ、MOCVD等) (1,679) | 選択エピ成長(溝部をエピで埋めるものを含む) (129)

Fターム[5F102HC02]に分類される特許

21 - 40 / 129

半導体基板および半導体装置

【課題】高いしきい値電圧と低いリーク電流のノーマリーオフの半導体素子を提供する。

【解決手段】基板2の上に少なくともAlを含むIII族窒化物からなる下地層(バッファー層)3を設けた上で、III族窒化物、好ましくはGaNからなる第1の半導体層(チャネル層)4と、少なくともAlを含むIII族窒化物、好ましくはAlxGa1−xNであってx≧0.2である第2の半導体層(電子供給層)6が積層されてなる半導体層群からなるHEMT構造の半導体素子の上に、AlN−Al2O3の混晶からなる絶縁膜7を形成し、その上にゲート電極9を形成した。

(もっと読む)

半導体基板および半導体装置

【課題】高いしきい値電圧と低いリーク電流のノーマリーオフの半導体素子を提供する。

【解決手段】基板2の上に少なくともAlを含むIII族窒化物からなる下地層(バッファー層)3を設けた上で、III族窒化物、好ましくはGaNからなる第1の半導体層(チャネル層)4と、少なくともAlを含むIII族窒化物、好ましくはAlxGa1−xNであってx≧0.2である第2の半導体層(電子供給層)6が積層されてなる半導体層群からなるHEMT構造の半導体素子の上に、Al2O3−Ga2O3の混晶からなる絶縁膜7を形成し、その上にゲート電極9を形成した。

(もっと読む)

窒化物半導体装置及び窒化物半導体装置の製造方法

【課題】シリコン基板上に優れた結晶性の窒化物半導体層が形成された窒化物半導体装置を提供する。

【解決手段】シリコン基板10と、シリコン基板10に接するとともにシリコン基板10上の一部分に形成された窒化シリコンからなる選択成長マスク層20とを備え、選択成長マスク層20が形成されていないシリコン基板10上に、当該シリコン基板10に接するように窒化物半導体層30が形成されている。

(もっと読む)

炭化珪素トランジスタ装置の製造方法

【課題】微細化と、オン特性を改善する、炭化珪素トランジスタ装置の製造方法の提供。

【解決手段】高濃度n型炭化珪素基板2上に、低濃度n型ドリフト層3と高濃度p型層10をエピタキシャル成長する工程と、高濃度p型層10の一部を除去離間した複数の高濃度p型ゲート領域4を形成する工程と、互いに隣り合った高濃度p型ゲート領域4の間に位置するチャネル領域7、高濃度p型ゲート領域4及びゲート電極領域10の全面を覆う低濃度n型ドリフト層3よりも低い不純物濃度の低濃度n型領域11をエピタキシャル成長する工程と、低濃度n型領域11の一部を除去する工程と、低濃度n型領域11の表面にイオン注入し高濃度n型ソース領域5を形成する工程と、高濃度n型ソース領域5上にソース電極6を、高濃度n型炭化珪素基板2の裏面にドレイン電極1を、ゲート電極領域10にゲート電極8を形成する工程を含む炭化珪素トランジスタ装置の製造方法。

(もっと読む)

半導体基板、トランジスタおよび半導体基板の製造方法

【課題】大きな電流密度あるいは大きな利得での駆動と低いオン抵抗とを両立したHFETを得る。

【解決手段】InxAlyGa1−x−yAszP1−z(ただしx、yおよびzは、0≦x<1、0≦y<1、0<x+y≦1および0≦z≦1を満たす)からなる半導体層を有し、前記半導体層が、トランジスタのソースとして機能するソース領域の全部または一部と、前記トランジスタのドレインとして機能するドレイン領域の全部または一部と、前記ソース領域および前記ドレイン領域の間に配置され、前記トランジスタのゲートとして機能するゲート領域の全部または一部とを含み、前記ゲート領域の全部または一部における前記半導体層の最大電子親和力が、前記ソース領域の全部または一部における前記半導体層の最小電子親和力または前記ドレイン領域の全部または一部における前記半導体層の最小電子親和力より小さい半導体基板を提供する。

(もっと読む)

III族窒化物半導体からなる半導体装置およびその製造方法、電力変換装置

【課題】主面をm面とするIII 族窒化物半導体で構成されたHFETにおいて、正のしきい値電圧を高めること。

【解決手段】HFET100は、凹凸加工されたa面サファイア基板101上に、m面を主面とするGaNからなるバッファ層102、ノンドープのGaNからなるチャネル層103、ノンドープのAlGaNからなる障壁層104、酸素ドープのn−AlGaNからなるキャリア供給層105を有している。キャリア供給層105は2つの領域に分離して形成されている。キャリア供給層105は、障壁層104上に選択的に再成長させて形成した層である。ゲート電極109にバイアスを印加しない状態では、ゲート電極109直下に2DEGが形成されないため、正のしきい値電圧を高めることができる。

(もっと読む)

半導体装置

【課題】III-V族窒化物半導体に設けるオーミック電極のコンタクト抵抗を低減しながらデバイスの特性を向上できるようにする。

【解決手段】半導体装置(HFET)は、SiC基板11上にバッファ層12を介在させて形成された第1の窒化物半導体層13と、該第1の窒化物半導体層13の上に形成され、該第1の窒化物半導体層13の上部に2次元電子ガス層を生成する第2の窒化物半導体層14と、該第2の窒化物半導体層14の上に選択的に形成されたオーム性を持つ電極16、17とを有している。第2の窒化物半導体層14は、底面又は壁面が基板面に対して傾斜した傾斜部を持つ断面凹状のコンタクト部14aを有し、オーム性を持つ電極16、17はコンタクト部14aに形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】小型かつ高性能で、性能のばらつきが抑制された半導体装置を提供すること。

【解決手段】SiC基板11上に形成された第1のGaN層12と、第1のGaN層12上に形成されたドレインパッド23と、第1のGaN層12上に形成された複数の円柱状のGaN層14と、これらの円柱状のGaN層14の上端に接するように形成された第2のGaN層16と、第2のGaN層16上に形成されたソースパッド25と、を具備する半導体装置であって、複数の円柱状のGaN層14は、それぞれ下方から上方に向かって径が連続的に拡大された形状であるとともに、下から順にドレイン領域17、ゲート領域18、ドレイン領域17よりも短いソース領域19からなり、ドレイン領域17の周囲には第1の絶縁膜20、ゲート領域18の周囲にはゲート電極21、ソース領域19の周囲には第2の絶縁膜22がそれぞれ形成される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】小型かつ高性能で、性能のばらつきが抑制された半導体装置を提供すること。

【解決手段】SiC基板11上に形成された第1のGaN層12と、第1のGaN層12上に形成されたソースパッド23と、第1のGaN層12上に形成された複数の円柱状のGaN層14と、これらの円柱状のGaN層14の上端に接するように形成された第2のGaN層16と、第2のGaN層16上に形成されたドレインパッド25と、を具備する半導体装置であって、複数の円柱状のGaN層14は、それぞれ下方から上方に向かって径が連続的に拡大された形状であるとともに、下から順にソース領域17、ゲート領域18、ドレイン領域19からなるとともに、ドレイン領域19は、ソース領域17よりも長く形成され、ソース領域17の周囲には第1の絶縁膜20、ゲート領域18の周囲にはゲート電極21、ドレイン領域19の周囲には第2の絶縁膜22がそれぞれ形成される。

(もっと読む)

窒化物電子デバイスを作製する方法

【課題】ゲートリーク電流を低減できる、窒化物電子デバイスを作製する方法を提供する。

【解決手段】時刻t0で基板生産物を成長炉に配置した後に、摂氏950度まで基板温度を上昇する。基板温度が十分に安定した時刻t3でトリメチルガリウム及びアンモニアを成長炉に供給して、i−GaN膜を成長する。時刻t5で基板温度が摂氏1080度に到達する。基板温度が十分に安定した時刻t6でトリメチルガリウム、トリメチルアルミニウム及びアンモニアを成長炉に供給して、i−AlGaN膜を成長する。時刻t7でトリメチルガリウム及びトリメチルアルミニウムの供給を停止して成膜を停止した後に、速やかに、成長炉へアンモニア及び水素の供給を停止すると共に窒素の供給を開始して、成長炉のチャンバ中においてアンモニア及び水素の雰囲気を窒素の雰囲気に変更する。窒素の雰囲気が形成された後に、時刻t8で基板温度の降下を開始する。

(もっと読む)

半導体装置およびその作製法

【課題】窒化物半導体を用いたヘテロ構造電界効果トランジスタにおいて、オーミック接触抵抗を大きく低減し、同時に、ソース電極2からチャネルまでの抵抗(アクセス抵抗)を大きく低減し、その結果として、高速化および低損失化(低消費電力化)が可能となる半導体装置およびその作製法提供すること。

【解決手段】ソース電極2とドレイン電極4とに、それぞれオーミック接触し、チャネル層窒化物半導体よりも小さいバンドギャップを有する再成長窒化物半導体(2)と、前記チャネル層窒化物半導体との間を、再成長組成傾斜窒化物半導体(1)を介して接続することによって、ソース電極2とチャネルとの間、および、ドレイン電極4とチャネルとの間を、それぞれ結ぶ電路中の半導体バンドギャップの不連続が解消されていることを特徴とするヘテロ構造電界効果トランジスタを構成する。

(もっと読む)

窒化物半導体装置及び窒化物半導体装置の製造方法

【課題】基板の放熱性が高くて基板に形成される窒化物半導体層の結晶欠陥が少ない窒化物半導体装置及びその製造方法を提供する。

【解決手段】

HEMT10の製造方法は、サファイア基板11の表面にGaNの薄膜12を形成する成膜工程と、薄膜12の上端からサファイア基板11の内部に達する深さの溝を形成する溝形成工程と、溝形成工程の後に、薄膜12を種結晶としてGaN層13を成長させる成長工程と、成長工程の前又は後に、サファイアよりも熱伝導性が高い高熱伝導性材料としてのAuを溝17に充填する充填工程とを備えている。

(もっと読む)

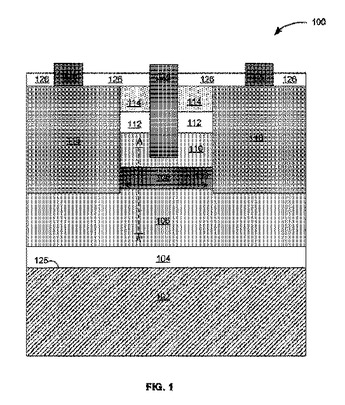

モノリシック集積複合III−V族及びIV族半導体デバイス、並びにその製造方法

【課題】単一のダイの上にIII−V族半導体デバイスをIV族半導体デバイスと共に集積する、複合デバイスの製造方法を提供する。

【解決手段】IV族半導体基板202上にIII−V族半導体本体274a,274bを形成するステップと、III−V族半導体本体にトレンチを形成し、トレンチ内にIV族半導体本体232を形成するステップとを有する。この方法は、IV族半導体本体内に少なくとも1つのIV族半導体デバイス272を製造するステップと、III−V族半導体本体内に少なくとも1つのIII−V族半導体デバイス274を製造するステップも含む。III−V族半導体本体の上面とIV族半導体本体の上面とを平坦化して、それぞれの上面をほぼ同一平面にするステップをさらに含む。一実施形態では、トレンチの側壁に隣接する、前記IV族半導体本体の欠陥領域に、少なくとも1つの受動デバイスを製造するステップをさらに含む。

(もっと読む)

集積回路デバイスに歪みを与える技術及び構成

本開示の実施形態により、例えば横型電界効果トランジスタなどの集積回路デバイスに歪みを与える技術及び構成が提供される。集積回路デバイスは、半導体基板と、該半導体基板と結合された第1のバリア層と、第1のバリア層に結合された、第1の格子定数を持つ第1の材料を有する量子井戸チャネルと、量子井戸チャネルに結合されたソース構造とを含む。ソース構造は、第1の格子定数とは異なる第2の格子定数を持つ第2の材料を有し、量子井戸チャネルに歪みを与える。その他の実施形態も開示される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】DモードとEモードの素子を組み合わせた半導体装置およびその製造方法を提供する。

【解決手段】DモードとEモードのJFETにおけるチャネル領域を設定する場所にそれぞれ凹部2aと凸部2bを備えることで、同一基板上に厚みが異なるn型チャネル層3を形成する。そして、このような厚みが異なるn型チャネル層3によってDモードとEモードで作動するJFETを同一基板上に備えることができるため、SiCでもDモードとEモードのJFETを組み合わせたSiC半導体装置を実現することが可能となる。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート電圧が閾値近傍に近づくときに発生する過剰なドレイン電流を抑制する。

【解決手段】トレンチ6の先端部に形成されたn-型チャネル層7がトレンチ6の長辺に位置する部分よりも膜厚が厚くなるため、そのトレンチ6の先端部においてJFET構造が構成されないようにする。例えば、トレンチ6の先端部の周辺を含めてn+型SiC基板1の外縁部においてn+型ソース領域4が除去されると共に、トレンチ6の先端部においてn-型チャネル層7および第2ゲート領域8が除去された凹形状とする。これにより、トレンチ6の先端部のJFET構造の閾値がトレンチ6の長辺に位置する部分のJFET構造の閾値からずれることによる影響を受けることがない。したがって、ゲート電圧が閾値近傍に近づくときに発生する過剰なドレイン電流を抑制できる構造のSiC半導体装置とすることが可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル層の厚みのバラツキを抑制できるJFET、MOSFETもしくはMESFETを備えた半導体装置およびその製造方法を提供する。

【解決手段】n+型層3に対して異方性エッチングを行うことによって凹部4を形成したのち、この凹部4内にエピタキシャル成長させることによってn型チャネル層5を形成する。これにより、n型チャネル層5を一定の膜厚かつ一定の濃度で形成することが可能となる。このため、従来の構造と異なり、n型チャネル層5の膜厚が一定なバラツキのない構造とすることが可能となる。したがって、JFETの特性も一定とすることが可能となる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】小型かつ高性能な半導体装置を提供すること。

【解決手段】SiC基板11上に形成された第1のGaN層12と、第1のGaN層12上に形成されたソースパッド23と、第1のGaN層12上に形成された複数の円柱状のGaN層14と、これらの円柱状のGaN層14の上端に接するように形成された第2のGaN層16と、第2のGaN層16上に形成されたドレインパッド25と、を具備する半導体装置であって、複数の円柱状のGaN層14は、それぞれ下から順にソース領域18、ゲート領域19、ソース領域よりも径が細いドレイン領域17からなり、ソース領域18の周囲には第1の絶縁膜20、ゲート領域19の周囲にはゲート電極21、ドレイン領域17の周囲には所定の空間を介して第2の絶縁膜22がそれぞれ形成される。

(もっと読む)

集積半導体基板構造の製造方法

【課題】GaN素子およびCMOS素子の両方を備えた集積回路を製造するための改善した方法を提供する。

【解決手段】集積半導体基板構造100は、基板11と、GaNヘテロ構造20と、半導体基板層30とを備える。GaNヘテロ構造20は、第1素子エリアに存在し、少なくとも部分的に保護層8で覆われている。半導体基板層30は、CMOS素子の区画のための第2素子エリアに存在する。GaNヘテロ構造20および半導体基板層30の少なくとも1つが、基板11の少なくとも1つの溝内をエピタキシャル成長して形成され、GaNヘテロ構造20および半導体基板層30は横方向に並置される。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】オン抵抗を大幅に低減し、十分な高電圧動作且つ高出力を得ることができる信頼性の高い化合物半導体装置を実現する。

【解決手段】ソース電極12及びドレイン電極13の下方の凹部7,8を充填し、電子供給層4の上方を覆う、Siを含むn−GaN層9が形成されており、n−GaN層9は、ソース電極12の下方及びドレイン電極13下方に含まれるSiの方が、ゲート電極15の近傍に含まれるSiよりも濃度が大きくなるように、Si添加量を漸減させながら成長形成される。

(もっと読む)

21 - 40 / 129

[ Back to top ]