Fターム[5F103PP18]の内容

半導体装置を構成する物質の物理的析出 (6,900) | 前処理・後処理 (421) | 連続処理工程 (30)

Fターム[5F103PP18]に分類される特許

1 - 20 / 30

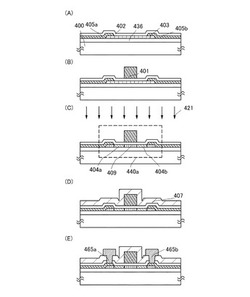

半導体装置

【課題】ノーマリーオフのスイッチング素子を実現するトランジスタ構造およびその作製方法を提供する。トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する構成およびその作製方法を提供する。信頼性の高い半導体装置を提供する。

【解決手段】半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてインジウム、ガリウム、亜鉛、及び酸素の4元素を少なくとも含み、該4元素の組成比を原子百分率で表したとき、インジウムの割合が、ガリウムの割合及び亜鉛の割合の2倍以上である酸化物半導体層を用いる。

(もっと読む)

成膜装置及び成膜方法

【課題】酸化物半導体を用いたトランジスタは、非晶質シリコンを用いたトランジスタと比較して信頼性が劣る場合があった。また、酸化物半導体を用いたトランジスタの電気特性は、基板内、基板間及びロット間において、ばらつきが大きい場合があった。そこで、信頼性が高く、電気特性のばらつきの小さい酸化物半導体を用いた半導体装置を作製する。

【解決手段】ロードロック室と、ロードロック室とゲートバルブを介して接続された搬送室と、搬送室とゲートバルブを介して接続された基板加熱室と、搬送室とゲートバルブを介して接続されたリークレートが1×10−10Pa・m3/秒以下である成膜室と、を有する成膜装置である。

(もっと読む)

基板冷却方法、基板冷却装置並びに製膜装置

【課題】製膜処理のタクトタイムが短い場合であっても、アンロード室で基板の温度分布が少ない状態とし、基板のそり変形や破損を抑制することができる基板冷却方法、基板冷却装置および製膜装置を提供することを目的とする。

【解決手段】減圧環境下において高温条件で表面に製膜処理が施された基板7を、減圧環境下でアンロード室に受け入れて、基板7の少なくとも一方の面側から、基板7の中央部に冷媒を噴き付けて基板7の冷却を行う第1基板冷却工程と、該第1基板冷却工程を経た基板7をアンロード室から搬出した後に、基板7の一方の面の反対側から、第1基板冷却工程で冷媒を噴き付けた領域の縁から所定距離内側に冷媒を噴き付けて、あるいは、第1基板冷却工程で冷媒を噴き付けた領域の縁から所定距離外側に冷媒を噴き付けて基板の冷却を行いながら基板の面内温度分布を補正する第2基板冷却工程と、を備える基板冷却方法。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタの電気特性は、基板内、基板間およびロット間において、ばらつきが大きく、熱、バイアスまたは光などの影響で変動が起こる場合がある。そこで、信頼性が高く、電気特性のばらつきの小さい酸化物半導体を用いた半導体装置を作製する。

【解決手段】酸化物半導体を用いたトランジスタにおいて、膜中および膜と膜との界面の水素を排除する。膜と膜との界面の水素を排除するためには、成膜と成膜との間で、基板を真空下で搬送する。また、大気暴露された表面を持つ基板は、熱処理またはプラズマ処理によって、表面の水素を除去する。

(もっと読む)

成膜装置、連続成膜装置、及び成膜方法

【課題】安定した電気的特性と高い信頼性を有する半導体装置を実現する成膜装置を提供することを課題の一とする。また、マザーガラスのような大きな基板を用いて、信頼性の高い半導体装置の大量生産を行うことの出来る成膜装置を提供することを課題の一とする。また、上記成膜装置を用いて安定した電気的特性と高い信頼性を有する半導体装置の作製方法を提供することを課題の一とする。

【解決手段】基板の搬送機構と、搬送機構が送る基板の進行方向に沿って、酸化物半導体を成膜する第1の成膜室と、第1の熱処理を行う第1の加熱室とを有し、基板は、該基板の成膜面と鉛直方向との成す角が1°以上30°以内に収まるよう保持され、大気に曝すことなく、基板に第1の膜を成膜した後に第1の熱処理を施すことのできる成膜装置を用いて、酸化物半導体層を形成する。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】信頼性および再現性が優れるとともに、歩留まりが高く生産性が優れた薄膜トランジスタおよびその製造方法を提供する。

【解決手段】薄膜トランジスタの製造方法は、基板上にゲート電極を形成する工程と、ゲート電極を覆って基板上に第1の絶縁膜を形成し、第1の絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第2の絶縁膜を形成して、第1の絶縁膜、酸化物半導体膜および第2の絶縁膜からなる積層体を得る工程と、積層体の第1の絶縁膜、酸化物半導体膜および第2の絶縁膜をパターニングして、それぞれゲート絶縁層、活性層およびチャネル保護層を形成する工程と、ソース電極およびドレイン電極を形成する工程とを有する。第1の絶縁膜、酸化物半導体膜および第2の絶縁膜は、大気に曝されることなく連続して形成される。

(もっと読む)

電子デバイスの製造方法、薄膜トランジスタ、電気光学装置及びセンサー

【課題】簡便に界面の欠陥を低減することを可能とする。

【解決手段】大気と遮断された真空成膜室内で、基板上に酸素不定比性のある酸化物を含有する第1層を成膜する第1成膜工程と、前記第1層上に前記第1層と同一材料又は異なる材料からなる第2層を成膜する第2成膜工程と、前記第1成膜工程後前記第2成膜工程前までの間、前記第1層を、前記真空成膜室を含む大気と遮断された室内で、前記第1成膜工程における前記真空成膜室内の酸素分圧よりも高い酸素分圧下に保持する分圧制御工程と、を有する。

(もっと読む)

成膜装置、及び半導体装置の作製方法

【課題】不純物が混入しない酸化物半導体膜を成膜する成膜装置を提供することを課題とする。不純物が混入しない酸化物半導体膜を含む半導体装置の作製方法を提供することを課題とする。

【解決手段】成膜装置を含む環境から不純物を排除することにより、成膜装置の外部から成膜装置内へ不純物を含む気体が漏洩(リーク)する現象を防げばよい。また、当該装置を用いて成膜した、不純物が低減された酸化物半導体層を半導体装置に適用すればよい。

(もっと読む)

半導体素子の作製方法、成膜装置

【課題】不純物が混入しない酸化物半導体を用いた半導体素子の作製に用いる連続成膜装置を提供することを課題とする。

【解決手段】10−6Pa以下に真空排気する手段と接続するロードロック室と、基板を加熱する第1の加熱手段が設けられた基板保持部と、少なくとも基板保持部周辺の壁面を加熱する第2の加熱手段と、スパッタリング用ターゲットを固定するターゲット保持部とが備えられ、それぞれが10−8Pa以下に真空排気する手段と接続する複数の成膜室と、10−8Pa以下に真空排気する手段と接続する加熱室と、ロードロック室、加熱室、及び成膜室のそれぞれとゲートバルブを介して連結され、10−6Pa以下に真空排気する手段と接続する搬送室とを少なくとも有し、ロードロック室、加熱室、成膜室及び搬送室のそれぞれと接続する真空排気する手段は、吸着型のポンプである成膜装置を提供する。

(もっと読む)

積層酸化物材料、半導体装置、および半導体装置の作製方法

【課題】トランジスタなどの半導体素子を有する半導体装置を安価に得ることのできる生産性の高い作製工程を提供することを課題の一とする。

【解決手段】下地部材上に、酸化物部材を形成し、加熱処理を行って表面から内部に向かって結晶成長する第1の酸化物結晶部材を形成し、第1の酸化物結晶部材上に第2の酸化物結晶部材を積層して設ける積層酸化物材料の作製方法である。特に第1の酸化物結晶部材と第2の酸化物結晶部材がc軸を共通している。ホモ結晶成長またはヘテロ結晶成長の同軸(アキシャル)成長をさせていることである。

(もっと読む)

半導体装置およびその作製方法

【課題】配線間の寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。

【解決手段】ボトムゲート構造の薄膜トランジスタにおいて、ゲート電極層と重なる酸化物半導体層の一部にチャネル保護層となる酸化物絶縁層を形成し、その酸化物絶縁層の形成時に酸化物半導体層の周縁部(側面を含む)を覆う酸化物絶縁層を形成する。酸化物半導体層の周縁部(側面を含む)を覆う酸化物絶縁層は、ゲート電極層と、その上方または周辺に形成される配線層(ソース配線層や容量配線層など)との距離を大きくし、寄生容量の低減を図る。酸化物半導体層の周縁部を覆う酸化物絶縁層は、チャネル保護層と同一工程で形成されるため、工程数の増加なく、寄生容量を低減できる。

(もっと読む)

薄膜トランジスタ製造装置、酸化物半導体薄膜の製造方法、薄膜トランジスタの製造方法、酸化物半導体薄膜、薄膜トランジスタ及び発光デバイス

【課題】酸化物半導体薄膜の酸素量を精度良く制御する。

【解決手段】大気と遮断された酸化物半導体薄膜形成室20内で、基板36上に、酸化物半導体の薄膜、すなわち活性層106を形成する薄膜形成工程と、前記薄膜形成工程の中で前記薄膜を加熱する加熱工程と、前記酸化物半導体薄膜形成室20と接続され、前記大気と遮断された輸送室14内で、前記基板36上に形成した薄膜を、前記加熱工程により加熱された温度から急速冷却する冷却工程と、を有する。

(もっと読む)

スパッタリング方法

【課題】少数のターゲットにて反応性ガスをON/OFFするだけで複数の膜種を成膜する際に、膜の種類の切替え時間を大幅に短縮し、高品質の膜を効率的に安定して確保できるスパッタリング技術を提供する。

【解決手段】第1のターゲット材料をスパッタリングして基板上に成膜する第1のスパッタ工程と、前記第1のターゲット材料とは異なる第2のターゲット材料をスパッタリングして前記基板上に成膜する第2のスパッタ工程と、前記第1のスパッタ工程と前記第2のスパッタ工程との間で、前記基板を前記複数のターゲット材料から遮蔽しつつ、前記第1および第2のターゲット材料をそれぞれ成膜レートが変化するようにスパッタリングするプリスパッタ工程とを行う。

(もっと読む)

成膜装置、電気光学装置の製造方法

【課題】異物に起因するピンホールの発生を抑制し、欠陥のない膜を形成可能な成膜装置を提供することを目的とする。

【解決手段】被処理基板Xの被処理面Xsに膜材料を成膜する成膜部10と、成膜部10に接続され被処理面Xsに付着する異物Fを除去する異物除去部20と、を備え、異物除去部20は、被処理基板Xを収納する処理室21と、処理室21内に設けられ、被処理面Xsの異物Fを除去する噴出ノズル22と、を有することを特徴とする。

(もっと読む)

光起電力モジュールの大量製造装置および方法

【課題】 基体の急速加熱、CdSの成膜、CdTeの成膜、CdCl2処理お よびオーム接点形成を含むすべての工程を中程度の圧力で単独の真空境界内で実施する、CdTe光起電力モジュールを大規模インラインで製造するための装置およびプロセスを提供する。

【解決手段】 金属塩をCdTe層上へ昇華することによってp+オーム接点領域を形成する。低コスト噴霧プロセスによって背面電極を形成し、マスクを介して行なう研磨ブラスチングか機械的ブラッシングによってモジュールをスクライビングする。真空処理装置によって、基体および膜の加熱、蒸気漏出を極力抑制した、基体および膜の蒸気への暴露、基体上への薄膜の成膜、および薄膜の基体からの剥離が容易になる。基体搬送装置により、薄膜成膜時に基体を真空に出入りさせるのが容易になり、基体搬送装置自体に被覆が生じるのを防止する。

(もっと読む)

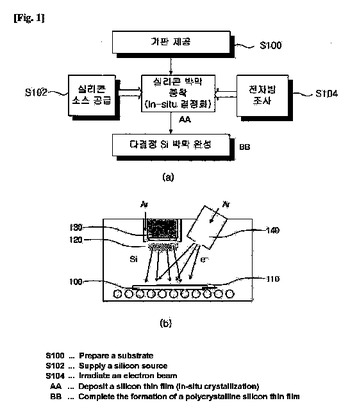

エネルギービームの照射を利用したシリコーン薄膜の製造方法

本発明のシリコーン薄膜の製造方法は、基板を提供する段階と;前記基板上にシリコーンソースを供給する段階と;前記シリコーンソースを供給してシリコーン薄膜を形成するとともに、電子ビームとイオンビームを照射したり、シリコーンソースを供給してシリコーン薄膜を形成した後後処理として前記基板上に電子ビームとイオンビームを照射する段階とを含む。本発明によって、前記供給されたシリコーンソースによって前記基板上にシリコーン薄膜が蒸着されながら前記照射された電子ビームが前記蒸着中のシリコーン薄膜にエネルギーを供給してこのシリコーン薄膜を蒸着工程中に(in−situ)結晶化させたり、非晶質シリコーン薄膜が形成された後後処理として電子ビームとイオンビームを照射することによって結晶化させることができる。また、電子ビームを照射するとともに、イオンビームをともに照射することによって、基板表面に蓄積される電子ビームの電荷がイオンビームの電荷によって中和されるようにして、電子ビームの電荷が基板表面に蓄積されて不必要な表面電流を形成することを防止し、效率的に非晶質シリコーン薄膜を結晶化させることができる。  (もっと読む)

(もっと読む)

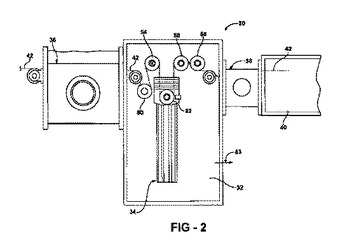

薄膜電気デバイスを製造するシステム及び方法

薄膜電気デバイスを基板上に製造するシステムを使用する方法が一実施例により与えられる。本システムはチャンバ及び気体ゲートを含む。チャンバはその中に集積装置を含む。集積装置はチャンバ内にて基板の一部分を集めるべく構成される。気体ゲートは、チャンバの圧力領域と第2圧力領域との流体連通を与える。  (もっと読む)

(もっと読む)

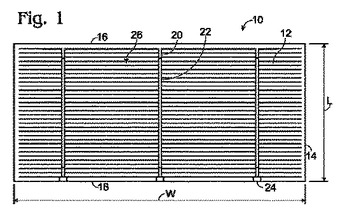

薄膜太陽電池セルを製造するための装置および方法

基板ウェブ上に半導体材料吸収層の薄膜層を形成するための改善された方法および装置を提供する。本発明の教示に従って、半導体層をマルチゾーンプロセスで形成することができ、これにより、さまざまな層が移動する基板ウェブ上に順次蒸着される。  (もっと読む)

(もっと読む)

シリコンドット形成方法及びシリコンドット形成装置

【課題】低温で基板上に直接粒径の揃ったシリコンドットを均一な密度分布で形成する方法及び装置を提供する。

【解決手段】チャンバ10内でシラン系ガス及び水素ガスからプラズマを形成してターゲット基板100上にシリコン膜を形成してシリコンスパッタターゲットを得、これをチャンバ1へ外気に触れさせることなく搬入配置して、チャンバ1内でスパッタリング用ガスからプラズマを発生させ、該プラズマでターゲットのシリコン膜をケミカルスパッタリングして基体S上にシリコンドットを形成する。

(もっと読む)

テラヘルツ電磁波対応ウェハ、テラヘルツ発生検出デバイス及びそれらの製造方法

【課題】キャリアのさらなる短寿命化が図られたテラヘルツ電磁波対応ウェハ、テラヘルツ発生検出デバイス及びそれらの製造方法を提供する。

【解決手段】本発明に係るテラヘルツ電磁波対応ウェハ11においては、表面11a近傍には多数のAsクラスター26が析出している。このAsクラスター26は、キャリアの捕獲中心として働くことが知られており、特に、表面11a近傍におけるAsクラスター26がキャリア捕捉に大きく寄与することが知られている。また、エピタキシャル層16が酸素を含有しており、この酸素により深い準位が形成されている。従って、このテラヘルツ電磁波対応ウェハ11においては、エピタキシャル層16の表面11a近傍におけるAsクラスター26が有意に増量されると共に、エピタキシャル層16中に酸素が含有されているため、キャリアのさらなる短寿命化を実現することが可能である。

(もっと読む)

1 - 20 / 30

[ Back to top ]