Fターム[5F110CC05]の内容

Fターム[5F110CC05]の下位に属するFターム

順スタガドープ (105)

Fターム[5F110CC05]に分類される特許

201 - 220 / 2,051

半導体装置

【課題】しきい値電圧の制御が困難な半導体膜を活性層に用いたトランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を提供する。

【解決手段】トランジスタの活性層と接する膜または活性層近傍の膜に負の固定電荷を有する酸化シリコン膜を用いることで、負の固定電荷により活性層に負の電界が常に重畳していることになり、しきい値電圧をプラスシフトさせることができる。そのため、トランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を作製することができる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】新たな構造の半導体装置を提供し、書き込み後の当該半導体装置のメモリセルのしきい値電圧のばらつきを小さくし、動作電圧を低減する、または記憶容量を増大する。

【解決手段】酸化物半導体を用いたトランジスタと、酸化物半導体以外の材料を用いたトランジスタとをそれぞれ有する複数のメモリセルと、複数のメモリセルを駆動する駆動回路と、駆動回路に供給する複数の電位を生成する電位生成回路と、複数のメモリセルへのデータの書き換えが終了したか否かを検知する書き込み終了検知回路と、を有し、駆動回路は、データバッファと、複数のメモリセルのそれぞれに複数の電位のうちいずれか一の電位をデータとして書き込む書き込み回路と、メモリセルに書き込まれたデータを読み出す読み出し回路と、読み出されたデータと、データバッファに保持されたデータとが一致するか否かをベリファイするベリファイ回路と、を有する。

(もっと読む)

電界効果トランジスタのゲート絶縁層用組成物、ゲート絶縁層、電界効果トランジスタ及び表示パネル

【課題】エッチング液や剥離液に対する耐性に優れているゲート絶縁層を形成することにより、このゲート絶縁層上にエッチング法により電極を形成させることができるようにすること。及び、その上に半導体材料を湿式塗布、結晶化処理しても溶出し難いゲート絶縁層を形成すること。すなわち、安価で高性能な上に、樹脂製のフレキシブル基板に適用可能な電界効果トランジスタを製造すること。

【解決手段】電界効果トランジスタのゲート絶縁層用組成物であって、重合性モノマー、重合開始剤及び架橋性基としてアリル基及び/又は(メタ)アクリロイル基を有する樹脂を含み、該重合性モノマーがエチレン性不飽和結合を2個以上有し、該架橋性基を有する樹脂の架橋性基当量が800g/eq以下であることを特徴とする電界効果トランジスタのゲート絶縁層用組成物。

(もっと読む)

重合体、この重合体を用いた有機薄膜及び有機薄膜素子

【課題】優れたホール輸送性を有する重合体を提供すること。

【解決手段】式(1)で表される構造単位及び式(2)で表される構造単位を有する重合体。 (もっと読む)

(もっと読む)

発光装置

【課題】駆動用トランジスタと、スイッチング用トランジスタを有する発光装置において、トランジスタのばらつきを低減する。

【解決手段】駆動用トランジスタと、スイッチング用トランジスタを有する発光装置において、駆動用トランジスタのチャネル幅をチャネル長よりも小さくする。その際、ゲート配線と平行にアノード側電源線を設けて、フルカラー表示を行う。

(もっと読む)

薄膜トランジスタ基板、表示装置、およびそれらの製造方法

【課題】本発明は、透過型液晶表示装置、ボトムエミッション型有機EL表示装置などの、TFT基板側が受光面または発光面となるフレキシブルディスプレイに用いることができるTFT基板を提供することを主目的とする。

【解決手段】本発明は、光透過性および絶縁性を有し、樹脂を含有する平坦化層と、上記平坦化層の一方の面にパターン状に形成され、フレキシブル性を有する金属層と、上記平坦化層の上記金属層側とは反対側の面に形成されたTFT素子および画素電極とを有し、上記画素電極が形成されている画素電極形成領域の少なくとも一部と、上記金属層が形成されていない金属層非形成領域の少なくとも一部とが重なるように配置されていることを特徴とするTFT基板を提供することにより、上記目的を達成する。

(もっと読む)

π電子共役系化合物前駆体を用いた電子デバイス用インク組成物ならびにその用途

【課題】脱離反応時の前駆体膜の流動化を抑制すること。また、変換後の半導体材料の不連続化を低減すること。その結果として、特性の低下が抑えられ、ばらつきの抑えられた電気特性を得ることが可能な電子デバイス用インク組成物ならびにそれを用いた電子デバイス、電界効果トランジスタ、およびその製造方法を提供すること。

【解決手段】電子デバイス用インク組成物であって、高分子材料と、π電子共役系化合物前駆体と、前記高分子材料および前記前駆体を溶解させる溶媒を少なくとも含有することを特徴とするインク組成物。

(もっと読む)

薄膜トランジスタの製造方法、薄膜トランジスタ、表示装置、センサ及びX線デジタル撮影装置

【課題】基板の選択性を広げつつ、電界効果移動度が高くノーマリーオフ駆動する薄膜トランジスタ等を得る。

【解決手段】活性層の成膜工程での成膜室中の雰囲気の全圧に対する酸素分圧をPo2depo(%)とし、熱処理工程中の雰囲気の全圧に対する酸素分圧をPo2anneal(%)としたときに、熱処理工程時の酸素分圧Po2anneal(%)が、−20/3Po2depo+40/3≦Po2anneal≦−800/43Po2depo+5900/43の関係を満たすように成膜工程と熱処理工程とを行う。

(もっと読む)

ディスプレイパネルの製造方法

【課題】ショート欠陥部の破片の発生を抑えつつ、かつ確実に配線のショートを解消すること。

【解決手段】薄膜トランジスタを内蔵するTFTパネルと、前記TFTパネルの表面上にマトリクス状に配置され、かつ画素電極を含む画素と、を有するディスプレイパネルの製造方法であって、前記TFTパネルを準備する工程と、前記TFTパネルの表面に画素電極をパターニングする工程と、前記画素電極のショート欠陥部を検出する工程と、前記ショート欠陥部に電圧を印加し、前記ショート欠陥部を溶断する工程と、を有する、ディスプレイパネルの製造方法。

(もっと読む)

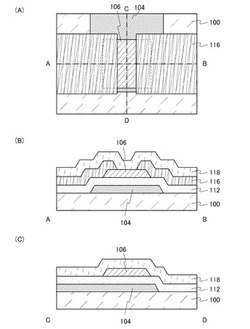

半導体装置および半導体装置の作製方法

【課題】トランジスタのチャネル部が形成される領域にU字状の縦長溝を形成し、見かけ上のチャネル長に対してチャネル長を長くする方法は、溝を掘るためにフォトリソグラフィ工程を余分に行う必要があり、コストや歩留まりの観点で問題があった。

【解決手段】ゲート電極または絶縁表面を有する構造物を利用し、三次元形状のチャネル領域を形成することにより、チャネル長が、上面から見たチャネル長に対して3倍以上、好ましくは5倍以上、さらに好ましくは10倍以上の長さとする。

(もっと読む)

電界効果型トランジスタ、表示装置、センサ及び電界効果型トランジスタの製造方法

【課題】電界効果型トランジスタの移動度を向上させる。

【解決手段】ゲート絶縁膜22と、活性層としてSn,Zn及びO、又はSn,Ga,Zn及びOを主たる構成元素とする酸化物半導体層14と、ゲート絶縁膜22と酸化物半導体層14との間に配置され、酸化物半導体層14よりも抵抗率が高い酸化物中間層16と、を有する。

(もっと読む)

表示装置および電子機器

【課題】配線層を低抵抗に保ち、かつ薄膜トランジスタにおける膜剥がれを防止した表示装置および電子機器を提供する。

【解決手段】基板11上に薄膜トランジスタ10および配線層20を備える。薄膜トランジスタ10は、基板11側からゲート電極12,ゲート絶縁膜13および半導体層14を有し、配線層20は、配線層20aおよび配線層20bにより構成されている。配線層20bとゲート電極12とは同一の膜厚および構成材料からなる。配線層20とゲート電極12との厚みは異なっている。具体的には、ゲート電極12の厚みは配線層20の厚みよりも薄く、ゲート電極12の膜内応力が小さくなっている。

(もっと読む)

膜形成用組成物および該組成物を用いた薄膜トランジスタ

【課題】 本発明の目的は、有機半導体素子の製造プロセス適応性に優れる膜形成用組成物および該組成物を用いた薄膜トランジスタを提供することである。

【解決手段】上記課題は、必須成分として、(a)式(I)で表される構造を0.6mmol/g以上含有する有機化合物と、(b)有機溶剤とを含有する膜形成用組成物および該組成物を有機半導体素子の絶縁膜等に用いる薄膜トランジスタにより達成される。該薄膜トランジスタは、閾値電圧が高く、ON/OFF電流比も高い特性の良好なトランジスタとなる。

【化1】 (もっと読む)

(もっと読む)

酸化物半導体薄膜の製造方法、電界効果型トランジスタ、表示装置及びセンサ

【課題】SGZO系酸化物半導体薄膜において、低温アニールによる低抵抗化が起こらず、成膜時の抵抗値と低温アニール後の抵抗値が同等となる組成を明らかとし、再現性が高く、大面積デバイス、特にフレキシブルデバイス作製に適した製造方法を提供する。

【解決手段】構成元素の組成比をSn:Ga:Zn=a:b:cとした場合、組成比が、a+b=2、且つ1≦a≦2、且つ1≦c≦11/2、且つc≧−7b/4+11/4を満たす酸化物半導体薄膜を基板上に成膜する成膜工程と、成膜工程後、酸化性雰囲気中で100℃以上300℃未満の熱処理を施す熱処理工程と、を有する。

(もっと読む)

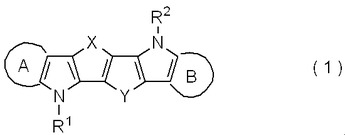

含ピロールヘテロアセン化合物、該化合物の製造方法、該化合物を含む薄膜及び該薄膜を含む有機半導体デバイス

【課題】有機半導体活性層の薄膜を与え得る新規な化合物が求められている。

【解決手段】式(1)

(式中、X及びYは、硫黄原子、酸素原子、セレン原子、テルル原子又はSO2を表す。環構造A及び環構造Bは、芳香族炭化水素環又は芳香族複素環を表す。該芳香族複素環は単一の環構造である。

R1およびR2は、水素原子、炭素数1〜30のアルキル基、炭素数1〜30のアルコキシ基、炭素数2〜30のアルケニル基、炭素数2〜30のアルキニル基、炭素数1〜30のアルキルチオ基、炭素数6〜20のアリール基、炭素数4〜20のヘテロアリール基を表す。)

で表される含ピロールヘテロアセン化合物。

(もっと読む)

ホール形成方法、並びに該方法を用いてビアホールを形成した多層配線、半導体装置、表示素子、画像表示装置、及びシステム

【課題】プロセス再現性が高く、微細なホールを効率よく低コストで形成することができるホール形成方法、並びに、該ホール形成方法を用いてビアホールを形成した多層配線、半導体装置、表示素子、画像表示装置、及びシステムの提供。

【解決手段】基材上にピラー形成液を付与してピラーを形成するピラー形成工程と、前記ピラーが形成された基材上に絶縁膜形成材料を付与して絶縁膜を形成する絶縁膜形成工程と、前記ピラーを除去して前記絶縁膜に開口部を形成するピラー除去工程と、前記開口部が形成された絶縁膜を熱処理する熱処理工程とを含むホール形成方法である。

(もっと読む)

アクセプター性の基を有する化合物、これを用いた有機薄膜及び有機薄膜素子

【課題】本発明の目的は、電子輸送性に優れる有機n型半導体として利用可能な化合物を提供することにある。本発明の目的はまた、係る化合物を含む有機薄膜、及びこの有機薄膜を備える有機薄膜素子を提供することにある。

【解決手段】かご状化合物又は脂肪族炭化水素化合物から誘導される4価以上の基であるコア部と、該コア部に結合した4以上の側鎖基と、を備え、側鎖基のうち2以上がアクセプター性の基を有する、化合物。

(もっと読む)

有機電子素子用電極、有機トランジスタ素子、インクジェットインク

【課題】接触抵抗を低減した有機電子素子用電極、及びこれを利用した有機トランジスタ素子を提供することを課題とする。

【解決手段】カーボンナノホーンを含んで構成された有機電子素子用電極、及び当該電極を、ソース電極18、及びドレイン電極20として適用した有機トランジスタ素子。

(もっと読む)

有機電子素子用電極、有機トランジスタ素子

【課題】有機半導体に対する接触抵抗を低減した有機電子素子用電極、及びこれを利用した有機トランジスタ素子を提供することを課題とする。

【解決手段】金属層24Aと、金属層24Aの表面の少なくとも一部に付着したカーボンナノチューブ24Bと、を有する有機電子素子用電極、及び当該電極を、ソース電極18、及びドレイン電極20として適用した有機トランジスタ素子。

(もっと読む)

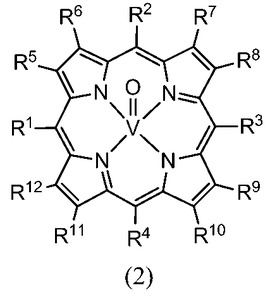

テトラビシクロポルフィリンバナジル錯体の製造方法、半導体層形成用組成物、電子デバイスの製造方法、太陽電池及び太陽電池モジュール

【課題】電子デバイスで好適に用いられるテトラベンゾポルフィリンバナジル錯体の高純度製造法の提供。

【解決手段】テトラビシクロポルフィリン化合物とバナジル化合物の反応を65℃以上95℃以下の温度で行う。式(2)の錯体の製造方法。 (もっと読む)

(もっと読む)

201 - 220 / 2,051

[ Back to top ]