Fターム[5F110CC09]の内容

Fターム[5F110CC09]に分類される特許

161 - 180 / 320

窒化物半導体素子およびその製造方法

【課題】抵抗値を効果的に低減することができる構造の窒化物半導体素子およびその製造方法を提供する。

【解決手段】この窒化物半導体素子は、基板1と、基板1の一方側に形成された窒化物半導体積層構造部2とを備えている。窒化物半導体積層構造部2は、n型層3と、n型層3上に積層形成されたp型GaN層4と、p型GaN層4上に積層形成されたn+型GaN層5とを備えている。n+型GaN層5のp型不純物濃度は、1×1018cm-3以下とされている。n型層3、p型GaN層4およびn+型GaN層5は、同一処理室内で、一度も大気中に取り出すことなく、結晶成長させられる。ただし、p型GaN層4の成長後には、結晶成長を中断し、処理室の内部雰囲気中のp型不純物濃度の低下を待って、n+型GaN層5の結晶成長が行われる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体素子とコンタクトプラグとが高精度で位置合わせされた半導体装置の製造方法を提供する。

【解決手段】半導体基板のエッチング速度が絶縁層2のエッチング速度よりも速くなるように、裏面側から、半導体基板内の突起状領域に対応する位置の異方性エッチングを行い、第1構造体が露出するまで開口2を設ける。

(もっと読む)

端部接触型縦型カーボンナノチューブトランジスタ

カーボンナノチューブベースの電界効果トランジスタのための垂直装置構造は、トレンチ内に形成された、1つまたは複数のカーボンナノチューブを有する。  (もっと読む)

(もっと読む)

半導体素子

【課題】インバータ回路など、電気接続された2つの半導体スイッチによるスイッチング動作を行なうための電気回路において、寄生インダクタンスおよびオン抵抗を抑制することができる構造の半導体素子を提供すること。

【解決手段】この半導体素子は、基板1と、基板1の一方側に形成される半導体積層構造部2とを備える。半導体積層構造部2は、n型層5、このn型層5の一方側(下面側)に積層されたp型層4、およびこのp型層4に積層されたn型層3からなる縦型npn構造の第1半導体積層構造8と、n型層5をこの第1半導体積層構造8と共有し、n型層5、このn型層5の他方側(上面側)に積層されたp型層6、およびこのp型層6に積層されたn型層7からなる縦型npn構造の第2半導体積層構造9とを備える。

(もっと読む)

半導体装置

【課題】層間絶縁膜を厚くしなくてもソース配線の外にドレイン配線を引き出せ、かつ、LOCOS酸化膜や層間絶縁膜などの絶縁膜の絶縁破壊を防止できるようにする。

【解決手段】素子部8から配線引出し部9に延設されるようにn-型ドリフト層4の裏面に裏面電極19を備え、この裏面電極19とソース配線18との間に電流が流れるような構造、つまりn-型ドリフト層4の表裏を貫通して縦方向に電流を流す構造にする。そして、裏面電極19を配線引出し部9まで延設し、n+型コンタクト領域21、配線引出し部9のn-型ドリフト層4、nウェル領域20およびn+型コンタクト領域21を通じてドレイン配線23と接続する。すなわち、裏面電極19を通じて電流が流れるようにすることにより、ドレイン配線23を素子部8の外に引き出した構造とする。

(もっと読む)

CMOS半導体装置

【課題】簡易な構造で、かつ小型化が可能なCMOS半導体装置を得る。

【解決手段】CMOS半導体装置であって、絶縁性の基板1と、基板1上に設けられる凸部形状のゲート電極2と、ゲート電極2の上面2a並びに第1の側面2b及び第2の側面2cを覆う絶縁膜3と、絶縁膜3を介してゲート電極の上面2a上に設けられるドレイン電極4と、ゲート電極2の第1の側面2a側の基板1上に設けられ、第1の電源端子側に接続される第1のソース電極5と、ドレイン電極4と第1のソース電極5の間を覆い、Pチャネル領域を形成するため設けられる第1の半導体層7と、ゲート電極2の第2の側面2c側の基板1上に設けられ、第2の電源端子側に接続される第2のソース電極6と、ドレイン電極4と第2のソース電極6の間を覆い、Nチャネル領域を形成するため設けられる第2の半導体層8とから構成されることを特徴としている。

(もっと読む)

半導体装置およびその製造方法

【課題】高密度に搭載可能な構造を有する電界効果トランジスタを備えた半導体装置を提供する。

【解決手段】基板と、この基板上に設けられた第1の絶縁層と、第1の絶縁層に埋め込まれた導電層と、この導電層に電気的に接続し直上に配置された下部拡散層、この下部拡散層上の半導体層、及びこの半導体層上の上部拡散層を有する柱状半導体部と、前記半導体層の周囲側面に設けられたゲート絶縁膜と、このゲート絶縁膜上に設けられたゲート電極と、このゲート電極および前記柱状半導体部を埋め込むように設けられた第2の絶縁層を有する半導体装置。

(もっと読む)

有機薄膜トランジスタの製造方法及び有機薄膜トランジスタ

【課題】移動度及びオン/オフ比が高い有機薄膜トランジスタ(有機TFT)を提供すること。

【解決手段】少なくとも基板上にゲート電極、ソース電極及びドレイン電極の3端子、絶縁体層並びに有機半導体層が設けられ、ソース−ドレイン間電流をゲート電極に電圧を印加することによって制御する有機薄膜トランジスタを作製する方法であって、該絶縁体層の形成工程がフッ素ポリマーの気相成膜を含むことを特徴とする有機薄膜トランジスタの製造方法及び該方法で製造されてなる有機薄膜トランジスタ。

(もっと読む)

テトラセン化合物及び有機半導体素子

【課題】高い移動度を維持し且つ室温下での溶媒溶解性及び大気中での耐酸化性に優れる有機半導体材料を提供する。また、高い移動度を有する有機半導体薄膜、及び、電子特性の優れた有機半導体素子を提供する。

【解決手段】

ソース・ドレイン電極として金電極のパターンを形成したシリコン基板上に、大気中室温下において2−ヘキシルテトラセンのトルエン溶液をキャストあるいはスピンコートすることにより、2−ヘキシルテトラセン薄膜を形成し、トランジスタ構造とした。

(もっと読む)

有機トランジスタおよびその製造方法

【課題】 寿命が長い有機トランジスタおよびその製造方法を提供する。

【解決手段】有機トランジスタ100は、ソース電極102と、ドレイン電極105と、ソース電極102とドレイン電極105との間に設けられた有機層100aとを有し、有機層100aは、平面構造を含む共役系炭化水素分子であるP型分子と、P型分子の共役系を構成するCH(炭素−水素)部位の少なくとも1つを窒素に置換された分子であるN型分子とが直接または間接に共有結合を介して結合された共役系分子鎖を含み、P型分子およびN型分子が有する平面構造が、ソース電極あるいはドレイン電極に平行な面に対して略垂直に配向している。

(もっと読む)

ハロゲン化フタロシアニン類の使用

本発明は、ハロゲン化フタロシアニン類を、電荷輸送材料及び/又は吸収体材料として用いる使用に関する。 (もっと読む)

薄膜半導体素子を備えた表示装置及び薄膜半導体素子の製造方法

【課題】高速動作が可能な高信頼性のアクティブマトリクス方式の表示装置を提供する。

【解決手段】絶縁性基板101上に成膜したSi窒化膜102、Si酸化膜103の上に非晶質Si膜104を成膜する。非晶質Si膜104は脱水素処理される(図1の(a))。この非晶質Si膜104に炭酸ガスレーザーによるアニールと同時にUV光を照射することで結晶化率が90%以上、表面の凹凸差が10nm以下の結晶化Si膜が得られる(図1の(c))。この結晶化Si膜を用いて表示装置のための薄膜トランジスタ等の半導体素子を形成する。炭酸ガスレーザーのみでのアニールでは結晶化率が90%以上の結晶化Si膜を得るためには350℃以上の基板加熱が必要である(図1の(b))。

(もっと読む)

半導体装置、半導体装置の製造方法並びにデータ処理システム

【課題】完全空乏化型のトランジスタ特性を維持しつつ、良好なS値と大きなドレイン電流が得られる縦型SGT構造を有する半導体装置を提供する。

【解決手段】本発明の半導体装置は、完全空乏化が可能な太さに形成された複数の半導体の基柱5と、複数の基柱5の各々の外周面に設けられたゲート絶縁膜10と、複数の基柱5の隙間を埋めて複数の基柱5の各々の外周面を覆うゲート電極11と、を備えていることを特徴とする。

(もっと読む)

ナノチューブ縦型電界効果トランジスタの形成方法

ナノチューブ電界効果トランジスタおよび製造方法を開示する。本方法は、開口部によって画定される導電層の領域と接触するようにするナノチューブの電気泳動堆積を含む。  (もっと読む)

(もっと読む)

有機薄膜トランジスタ

【課題】塗工や印刷等の簡便なプロセスで製造できる有機薄膜トランジスタを提供すること。

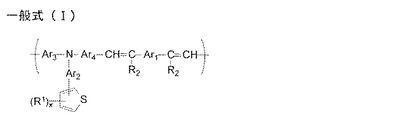

【解決手段】有機半導体層1を具備する有機薄膜トランジスタにおいて、有機半導体層が、下記一般式(I)で示される繰り返し単位を有する重合体を主成分とするものであることを特徴とする有機薄膜トランジスタ。;

(Ar1、Ar2、Ar3、Ar4は芳香族炭化水素もしくは芳香族複素環の二価基を表わす。)

(もっと読む)

マルチファセット・ゲートMOSFETデバイス

【課題】ゲート電極中のドーパント不純物がゲート絶縁物を貫通する。

【解決手段】中心部分と2つの端部を備えた、歪みSiベース単結晶ストリップであって、中心部分がマルチファセット・チャンネル領域511、512を備え、端部がソースとドレイン540を備えるものである歪みSiベース単結晶ストリップ510と、チャンネル領域を覆うゲート絶縁物520、530と、チャンネル領域の少なくとも2つのファセットの上に重なりかつゲート絶縁物に接続するゲート500と、付着手段によって歪みSiベース単結晶ストリップと係合する支持台590、595とを備え、ゲートが、ゲート絶縁物の上面に配置された第1の層500を含み、第1の層がSi:CまたはSiGe:Cである、マルチファセット・ゲートMOSFETデバイスである。

(もっと読む)

スプリット仕事関数ゲートを含むMOSFETを有する集積回路

【課題】ゲート誘起ドレインリーク電流が少ない電界効果トランジスタ、および、ゲート電極とソース/ドレイン領域との間に薄い絶縁体構造物を含む集積回路を提供する。

【解決手段】トランジスタ542のゲート電極は、ゲート電極とチャネル領域512との間の第1のフラットバンド電圧を決定する主部532と第1の側部535とを含む。この第1の側部は、上記主部に接触すると共に、上記ゲート電極と第1のソース/ドレイン領域514,516との間の第2のフラットバンド電圧を決定する。上記第1のフラットバンド電圧および上記第2のフラットバンド電圧は、少なくとも0.1eVだけ異なる。

(もっと読む)

ベンゾジチオフェン誘導体並びにそれを用いた有機薄膜トランジスタ及び有機薄膜発光トランジスタ

【課題】大気中に暴露した状態でも電界効果移動度の安定性に優れる有機化合物並びにそれを利用した有機薄膜トランジスタ及び有機薄膜発光トランジスタを提供する。

【解決手段】中心に芳香族炭化水素基又は芳香族複素環基を有するベンゾジチオフェン誘導体、少なくとも基板上にゲート電極、ソース電極及びドレイン電極の3端子、絶縁体層並びに有機半導体層が設けられ、ソース−ドレイン間電流をゲート電極に電圧を印加することによって制御する有機薄膜トランジスタにおいて、前記有機半導体層が、中心に芳香族炭化水素基又は芳香族複素環基を有する特定のベンゾジチオフェンを含む有機薄膜トランジスタ、並びに該有機薄膜トランジスタにおいて、ソース−ドレイン間を流れる電流を利用して発光を得、ゲート電極に電圧を印加することによって発光を制御する有機薄膜発光トランジスタである。

(もっと読む)

有機薄膜トランジスタ及び有機薄膜発光トランジスタ

【課題】大気中の安定性に優れ、かつ動作速度が大きい有機薄膜トランジスタが望まれている。

【解決手段】この有機薄膜トランジスタは、基板上に、ゲート電極、ソース電極及びドレイン電極の3端子と、ソース電極及びドレイン電極とゲート電極との間を絶縁する絶縁体層と、有機半導体層とが設けられていて、ゲート電極に印加された電圧によりソース−ドレイン間電流を制御する有機薄膜トランジスタにおいて、有機半導体層の結晶性を制御する結晶性化合物から成膜される結晶性制御層を備え、該結晶性制御層上に、複素環基を有する化合物またはキノン構造を有する化合物を含んでなる有機半導体層が成膜されていることを特徴とするものである。また、前記有機薄膜トランジスタのソース電極とドレイン電極のうち、いずれか一方を正孔注入性電極で構成し、残りの電極を電子注入性電極で構成したことを特徴とする有機薄膜発光トランジスタを提供するものである。

(もっと読む)

電界効果半導体装置

【課題】HEMTの漏れ電流を低減すること及び集積度を高めることが困難であった。

【解決手段】HEMT又はこれに類似の電界効果半導体装置は、第1の半導体層(3)と、第1の半導体層(3)に2次元電子ガス層を生じさせるために第1の半導体層(3)の一部上に配置された第2の半導体層(4)と、第1の半導体層(3)の主面(14)上に配置された第3の半導体層(5)と、第3の半導体層(5)の上に配置され且つ第3の半導体層(5)よりも低い抵抗率を有している第4の半導体層(6)と、第2の半導体層(4)の上に配置された第1の主電極(7)と、第4の半導体層(6)の上に配置された第2の主電極(8)と、第3の半導体層(5)の側面を被覆している絶縁膜(9)と、絶縁膜(9)を介して第3の半導体層(5)に対向配置されたゲート電極(10)とを備えている。

(もっと読む)

161 - 180 / 320

[ Back to top ]