Fターム[5F110CC09]の内容

Fターム[5F110CC09]に分類される特許

301 - 320 / 320

電界効果トランジスタ

【課題】 電界効果トランジスタのキャリアの移動度を向上させる。

【解決手段】 半導体部と絶縁部を備える電界効果トランジスタであって、絶縁部が強誘電性及び強磁性をともに有する物質と非磁性物質を含有することを特徴とする電界効果トランジスタ。

(もっと読む)

電界効果トランジスタおよび該電界効果トランジスタの製造方法

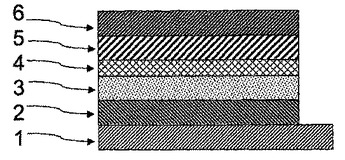

電界効果トランジスタにおいて、ソースコンタクトとドレインコンタクトとの間に垂直方向に配向されナノメータ領域の直径を有する少なくとも1つの半導体支柱が設けられており、この半導体支柱が絶縁間隔を残してゲートコンタクトによってリング状に取り囲まれていることは、すでに知られている。本発明によれば、簡単にされた製造方法が提供される。本発明に従い製造されたトランジスタは、半導体支柱(2)が第1および第2の絶縁層(3,5)に組み込まれており、これらの絶縁層の間にゲートコンタクトとして外側に向かって案内された金属層(4)が設けられている。上方に向かって第2の絶縁層(5)を貫通するこの金属層の端部は、部分的に絶縁体(6)に変換されるかまたは、部分的に除去されて絶縁材料によって充填される。  (もっと読む)

(もっと読む)

半導体装置

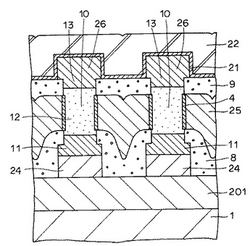

【課題】 ビット線の容量を小さくし、高速動作が得られるダイナミックランダムアクセスメモリを得ること。

【解決手段】 ソース/ドレイン領域の一方になり、かつビット線にもなる第1の不純物拡散層24の上に、第1の半導体層11、チャネル半導体層12、ソース/ドレイン領域の他方になり、かつストレージノード26にもなる第2の導電層13が設けられている。第2の導電層13の上にキャパシタ絶縁膜21が設けられる。キャパシタ絶縁膜21を介在させて、ストレージノード26の上にセルプレート22が設けられている。

(もっと読む)

不揮発性メモリーセル、メモリーセルアレイおよび不揮発性メモリーセルの製造方法

本発明は、不揮発性メモリーセル、メモリーセルアレイおよび不揮発性メモリーセルの製造方法に関するものである。不揮発性メモリーセルは、チャネル領域として設計されたナノ素子を有する垂直電界効果トランジスタと、ナノ素子を少なくとも部分的に取り囲む、電荷蓄積層として、および、ゲート絶縁層としての電気絶縁層とを備えている。この電気絶縁層は、電気的な電荷担体をその内部に選択的に注入でき、または、その内部から除去できるように設計されており、電気絶縁層に注入された電気的な電荷担体によって、ナノ素子の導電性に特徴的に影響を及ぼすように設計されている。  (もっと読む)

(もっと読む)

有機又は無機トランジスタ及びその製造方法並びに画像表示装置

【課題】動作特性を損なうことなく短チャネル化及び微細化を行うことができる有機又は無機トランジスタ及びその製造方法並びに画像表示装置を提供する。

【解決手段】有機トランジスタは、基板1の表面に形成された導電層2上の絶縁層3及びそれを含む内面に形成される。導電層2は、ソース又はドレイン電極6に接続される。ゲート電極4は、絶縁層3上にある多孔質金属膜内にあり、ゲート絶縁膜5は、ゲート電極4を覆うようにして形成される。有機半導体層7は、ソース又はドレイン電極6とドレイン又はソース電極8との間に挟まれ、有機トランジスタのチャネルは、有機半導体層7とゲート絶縁膜5との界面に垂直方向に形成される。

(もっと読む)

SOIトレンチ横型IGBT

【課題】IGBTにおいて、高耐圧で、大電流での駆動を可能とし、ラッチアップ耐量を高くし、単位面積あたりのオン抵抗を低くすること。

【解決手段】n+エミッタ領域6aとp+コレクタ領域12aとの間のウェハ全面にトレンチ16a,16bを形成し、その中をトレンチ埋め込み絶縁膜17で埋めることによって、耐圧を担持するドリフト領域を折り曲げて、実効的なドリフト長を長くする。トレンチ埋め込み絶縁膜17内に、エミッタ側フィールドプレート15を埋め込み、トレンチ埋め込み絶縁膜17のエミッタ側に生じる横電界を遮蔽することによって、n-ドリフト領域3aとpベース領域4aとのPN接合で発生する電界を緩和する。

(もっと読む)

電界効果トランジスタ

【課題】 電界効果トランジスタのキャリアの移動度を向上させる。

【解決手段】 電界効果トランジスタに、強誘電性及び強磁性をともに有する物質を含有する絶縁部16と絶縁部16に対向して設けられ強磁性を少なくとも有する物質を含有する強磁性部14とを設ける。

(もっと読む)

電界効果トランジスタ

【課題】 従来よりもオン電流値を上昇させ、精度の高い回路動作を行なえるようにした、優れた電界効果トランジスタを提供する。

【解決手段】 ゲート絶縁部2に、強誘電体物質を含有するコア部と、常誘電体物質を含有するシェル部とからなるコア・シェル構造粒子を含有させる。

(もっと読む)

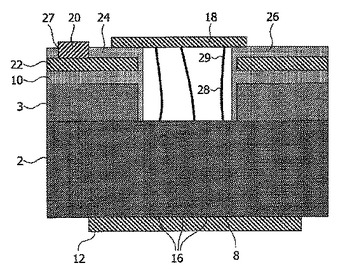

ナノワイヤ半導体デバイス

半導体デバイスはナノワイヤ(16)を使用して製造される。ナノワイヤ(16)に沿う伝導を制御するために導電ゲート(22)が使用されても良い。この場合、一方の接点がドレイン(12)であり、他方がソース(18)である。ナノワイヤ(16)は、基板(2)中の或いは特に基板(2)上の表面層(3)中のトレンチまたは貫通穴(8)内で成長されても良い。ゲート(22)はナノワイヤ(16)の一端にだけ設けられても良い。ナノワイヤ(16)は、その全長にわたって同じ材料から成ることができ、あるいは、異なる材料を使用することができ、特に、ゲート(22)の近傍およびゲート(22)とトレンチの底部との間で異なる材料を使用できる。  (もっと読む)

(もっと読む)

相補的窒化膜トランジスタの垂直およびコモンドレイン

【課題】少ない材料で、電流搬送能力に優れた半導体デバイスを提供する。

【解決手段】 異なる平面に、オーミック接点を含む半導体デバイス、およびそのデバイスを製造するための方法であって、連続したステップで、異なる導電タイプの半導体層の半導体スタックをエッチングし、第1半導体層内に、第1の幅の第1開口部を形成し、別の半導体層を露出させ、次に別の層内に、より狭い幅の第2開口部を形成し、オーミック接点を収容するための別の層の一部を、露出した状態で残すことを含む。

(もっと読む)

アレイ状に配置された垂直型カーボン・ナノチューブ電界効果トランジスタを製造する方法、並びに、それによって形成された電界効果トランジスタ及びアレイ

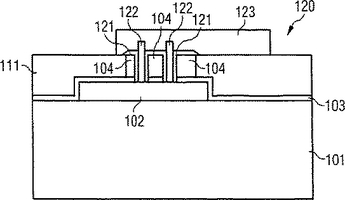

【課題】 カーボン・ナノチューブ電界効果トランジスタと、カーボン・ナノチューブ電界効果トランジスタのアレイと、デバイス構造体とを製造するための方法、及び、該方法によって形成されたデバイス構造体のアレイを提供する。

【解決手段】 本方法は、ゲート電極層と、各々がソース/ドレイン・コンタクトと電気的に結合された触媒パッドとを含む積層構造体を形成することを含む。ゲート電極層は多数のゲート電極に分割され、少なくとも1つの半導体カーボン・ナノチューブが、化学気相堆積プロセスによって触媒パッドの各々の上に合成される。完成したデバイス構造体は、ゲート誘電体によって覆われた側壁を有するゲート電極と、該ゲート電極の該側壁に隣接する少なくとも1つの半導体カーボン・ナノチューブとを含む。ソース/ドレイン・コンタクトを半導体カーボン・ナノチューブの両端と電気的に結合することによって、デバイス構造体が完成する。多数のデバイス構造体は、メモリ回路又は論理回路のいずれかとして構成することができる。

(もっと読む)

垂直型ナノチューブ半導体デバイス構造体及びその形成方法

【課題】 大量生産技術に対応した、チャネル領域として1つ又は複数の半導体カーボン・ナノチューブを組み込む垂直型FET構造体を提供する。

【解決手段】 少なくとも1つのナノチューブを組み組む垂直型デバイス構造体、及び、化学気相成長法によってこうしたデバイス構造体を製造する方法である。各々のナノチューブは、触媒パッドによって触媒作用が及ぼされる化学気相成長法によって成長され、誘電体材料のコーティング内に包み込まれる。包み込まれたナノチューブがゲート電極の厚さを通って垂直方向に延びるように、該包み込まれたナノチューブの周りにゲート電極を形成することによって、垂直型電界効果トランジスタを作ることができる。包み込まれたナノチューブ、及び、該包み込められたナノチューブを支持する対応する触媒パッドが1つのキャパシタ・プレートを形成するように、キャパシタを作ることができる。

(もっと読む)

スペーサによって定められる通路内で成長した半導体ナノチューブを組み込んだ垂直型電界効果トランジスタ

【課題】 ICチップの大量生産技術に対応した、チャネル領域として1つ又は複数の半導体カーボン・ナノチューブを組み込んだ垂直型FET構造体を提供する。

【解決手段】 少なくとも1つの半導体ナノチューブによって定められたチャネル領域を有する垂直型電界効果トランジスタ、及び、こうした垂直型電界効果トランジスタを、スペーサによって定められるチャネルを用いて化学気相成長法によって製造する方法である。各々のナノチューブは、スペーサとゲート電極との間に定められる高アスペクト比通路の底部に位置決めされた触媒パッドにより触媒される化学気相成長法によって、成長する。各々のナノチューブは、スペーサによる境界の存在によって制限される垂直配向を持つ通路内で成長する。通路の開口部から離れたスペーサの底部に、隙間が設けられる。隙間を通って触媒パッドに流れる反応物質が、ナノチューブの成長に関与する。

(もっと読む)

半導体電源スイッチ、および、半導体電源スイッチの製造に適した方法

半導体電源スイッチ(1)が、ソース端子(2)と、ドレイン端子(3)と、それらの間に設けられた半導体構造と、ゲート(5)とを備えている。このゲート(5)は、ソース端子(2)とドレイン端子(3)との間の半導体構造を介して電流の流れを制御するために、用いられる。該半導体構造は、複数のナノワイヤ(4)を備えている。これらのナノワイヤ(4)は、並列に接続されており、各ナノワイヤがソース端子とドレイン端子との間の電気接続を形成するように、配置されている。  (もっと読む)

(もっと読む)

ヘテロ接合を備える半導体デバイス

ヘテロ接合を有する半導体デバイス。このデバイスは、基板と少なくとも1つのナノ構造とを備える。この基板とナノ構造とは、異なる材料から成る。この基板は、例えばIV族半導体材料から成ることがあるのに対して、このナノ構造は、III−V族半導体材料から成ることもある。このナノ構造は、この基板によって支持され、この基板とエピタキシャルな関係にある。ナノ構造は、ゲートアラウンドトランジスタデバイスなどの電子デバイスの機能コンポーネントになる可能性がある。ゲートアラウンドトランジスタの一実施形態においては、ナノワイヤ(51)が、基板(50)によって支持され、この基板はドレインであり、このナノワイヤは電流チャネルであり、上部金属コンタクト(59)はソースである。薄いゲート絶縁膜(54)が、このナノワイヤとこのゲート電極(55A、55B)とを絶縁している。  (もっと読む)

(もっと読む)

薄膜トランジスタ及びその製造方法

本発明の薄膜トランジスタは、半導体層(14)と、前記半導体層に相互に対向するように分離して設けられたソース領域(15)とドレーン領域(16)とを有する薄膜トランジスタ(100)であって、前記半導体層はπ共役系有機半導体分子を主成分として有し、前記π共役系有機半導体分子が、π軌道が実質的に対向するように配向され、かつ主鎖の分子軸が前記半導体層に形成されるチャネルにおける電界の方向に対して傾斜して配向されている。 (もっと読む)

完全空乏型シリコン・オン・インシュレータのCMOSロジック

【課題】SOI技術を用いた部分空乏型CMOSデバイスにおける浮遊ボディの不必要な影響を制御可能とする。

【解決手段】シリコン・オン・インシュレータのCMOSメモリデバイスにおいて、引き出し線を含む領域が用いられる。引き出し線を逆方向にバイアスすることで、部分空乏型メモリセルのボディ領域から少数キャリアを取り除く。これにより、ボディ領域を完全空乏化し、浮遊ボディの不必要な影響を抑制する。

(もっと読む)

縦型有機電界効果トランジスタ

共通のソース電極を共有するアクティブセルとキャパシタとを備える縦型有機電界効果トランジスタ。アクティブセルは、ドレイン電極と共通のソース電極との間に挟まれた半導体層を備える。キャパシタは、ゲート電極と共通のソース電極との間に挟まれた誘電体層を備える。共通のソース電極は、ゲート電極に印加される電位を制御することによってソース電極とドレイン電極との間を流れる電流を制御することを可能にする。

(もっと読む)

(もっと読む)

縦型ナノトランジスタおよび該トランジスタの製造方法ならびにメモリ装置

本発明の課題は、機械的応力に対し良好な耐性をもち、その製造が公知の従来技術よりも煩雑でない縦型ナノトランジスタを提供することである。本発明によればこの課題は、以下の特徴を備えた縦型ナノトランジスタによって解決される。すなわちソースコンタクトと、ドレインコンタクトと、ゲート領域と、ソースコンタクトとドレインコンタクトの間に配置され半導体特性をもつ円筒状のチャネル領域が設けられており、この円筒状チャネル領域は絶縁性フレキシブル基板に埋め込まれており、この領域は、ゲート領域とチャネル領域上部が同軸構造を成すよう、フレキシブル基板上およびチャネル領域上部の金属層により形成されたゲート領域により取り囲まれている。さらにソースコンタクトと半導体特性をもつチャネル領域とドレインコンタクトは縦方向に配置されていて、ソースコンタクトとドレインコンタクトと半導体特性をもつチャネル領域に対向するゲート領域と、基板の上側および下側は電気的に絶縁性の部材を有している。メモリ装置は多数のこの種の縦型ナノトランジスタから成る。本発明はこの種のトランジスタの製造方法にも関する。  (もっと読む)

(もっと読む)

薄膜電子部品の製造方法および製造装置ならびに薄膜電子部品

本発明は、薄膜電子部品の製造方法およびこの方法を実施する装置に関する。また、本発明は、この方法に従って製造された薄膜電子部品に関する。まず、実質的に誘電性を有する基板上に、導電性材料から成るガルヴァニックに均一な最下段の導電層が形成され、この最下段の導電層から導電領域がガルヴァニックに相互に分離して、電極パターンが形成される。この電極パターン上には、薄膜部品に必要とされる上部の不活性層または活性層を1層または数層形成することが可能である。本発明によれば、この最下段の導電層が分離することによる電極パターンの形成は、ダイカットエンボス加工に基づく切断作業を最下段の導電層に行うことによる。すなわち、切断作業に使用する切断部材の浮彫りが、基板上に永久変形が生じさせ、同時に、導電層から、ガルヴァニックに相互に分離した導電領域に至る領域をエンボス加工する。本発明は、ロールツーロール方式における薄膜部品の製造に適している。

(もっと読む)

(もっと読む)

301 - 320 / 320

[ Back to top ]