Fターム[5F110CC09]の内容

Fターム[5F110CC09]に分類される特許

141 - 160 / 320

有機半導体組成物

【課題】特定の有機化合物と高分子材料を含む組成物およびインクを用いることで、耐熱性、大気安定性、基板濡れ性に優れた、電界効果トランジスタ用の材料、および製造法を提供すること。

【解決手段】下記一般式(1)で表される部分構造を有する有機半導体材料および高分子材料を含む組成物およびインク。

(式中、XはS、Se、またはTeを表す。)

(もっと読む)

有機トランジスタ

【課題】高い移動度、大きな電流オン/オフ比を有し、保存安定性に優れた有機トランジスタを提供する。

【解決手段】有機半導体層を有する有機トランジスタにおいて、該有機半導体層に一般式(1)で表される化合物を少なくとも1種含有してなる有機トランジスタ。

(式中、X1〜X4はそれぞれ独立に、水素原子、ハロゲン原子、直鎖、分岐または環状のアルキル基、直鎖、分岐または環状のアルコキシ基、直鎖、分岐または環状のアルコキシアルキル基、あるいは置換または未置換のアリール基を表し、環Aおよび環Bはそれぞれ独立に、置換または未置換のチオフェン環、あるいは置換または未置換のベンゾ[b]チオフェン環を表す)

(もっと読む)

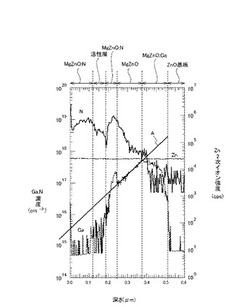

半導体素子

【課題】ドナー元素を含む半導体層を備えた半導体素子を形成する場合に、このドナー元素が上層に拡散することを抑制することができる半導体素子を提供する。

【解決手段】ZnO基板上にGaドープMgZnO層、アンドープMgZnO層、窒素ドープMgZnO層、アンドープ活性層、窒素ドープMgZnO層と積層した積層体でGaの拡散を分析した。アンドープMgZnO層の次の窒素ドープMgZnO層で、拡散してきたGaの濃度が表面側になるにつれて、急激に減少しており、この窒素ドープMgZnO層の上層にGaは拡散していない。このように、ドナー元素を含む同一組成のドナー含有半導体層の一部に、アクセプタ元素を含み前記ドナー含有半導体層と同一組成のアクセプタ含有半導体層を形成することで、ドナー元素の拡散を防止できる。

(もっと読む)

半導体装置

【課題】絶縁ゲート構造を有する横型の高耐圧半導体装置において、セル面積の増大を抑えつつ、素子全体の耐圧を向上させること。

【解決手段】平面レイアウトにおいて、トラック形状のゲート電極38は、直線状に延びるコレクタ電極40を囲む。トラック形状のエミッタ電極37は、ゲート電極38を囲む。トラック形状の第1分離トレンチ43aは、エミッタ電極37を囲む。第2分離トレンチ43bは、第1分離トレンチ43aを囲む。第1分離トレンチ43aと第2分離トレンチ43bの間の領域は、n型の分離シリコン領域44である。分離シリコン領域44は、エミッタ電極37と同電位になっている。ゲート電極38を通る切断線Q−R−Sにおける断面構成において、ゲート電極38の弧状部分に対応するR−S間のpベース領域の深さは、ゲート電極38の直線状部分に対応するQ−R間のpベース領域の深さよりも浅い。

(もっと読む)

半導体装置及びその製造方法

【課題】貼り合わせSOI基板を使用せずに容易な製造プロセスにより、微細で、高速且つ高性能なMIS電界効果トランジスタを提供する。

【解決手段】半導体基板1上に酸化膜2を介して、横方向エピタキシャル半導体層3が設けられ、素子分離領域形成用の埋め込み絶縁膜4及び酸化膜2により島状に絶縁分離されている。絶縁分離された横方向エピタキシャル半導体層3上に選択的に縦方向エピタキシャル半導体層7が設けられ、上部には高濃度ドレイン領域10及び低濃度ドレイン領域9が設けられ、下部には高濃度ソース領域8が設けられ、側面にはゲート酸化膜11を介してゲート電極12が設けられている。高濃度ドレイン領域10、高濃度ソース領域8及びゲート電極12には、それぞれバリアメタル18を有する導電プラグ19を介してバリアメタル21を有するCu配線22が接続されている。

(もっと読む)

有機半導体装置

【課題】製造工程を簡略化し、占有面積を低減したキャパシタ部とトランジスタ部を有する有機半導体装置の提供。

【解決手段】基板1と、基板1上に形成された凸部の少なくとも上面部を構成する第1の電極2と、第1の電極2上及び凸部の側面2b上に設けられる第1の絶縁膜3と、凸部の上方2aの第1の絶縁膜3上に設けられる第2の電極4と、凸部の側面2bの下方に隣接して基板1上に設けられる第3の電極5と、凸部の側面2b上の第1の絶縁膜3を覆い、第2の電極4及び第3の電極5と接するように設けられる有機半導体層6とを備え、第1の電極2と、第1の絶縁膜3と、第2の電極4とから、キャパシタ部20が構成され、第2の電極4及び第3の電極5からなるソース電極及びドレイン電極と、第1の電極2からなるゲート電極と、第1の絶縁膜3からなるゲート絶縁膜と、有機半導体層6からなる半導体層とから、トランジスタ部21を構成する。

(もっと読む)

有機半導体材料及びその製造方法、並びに有機電子デバイス

【課題】高いキャリア移動度と安定性を有し、容易なプロセスで作製可能な有機半導体材料及び有機デバイスを提供する。

【解決手段】チアポルフィリン骨格を有し、チアポルフィリン環平面からチアポルフィリン骨格を形成する原子の中心までの距離が1Å以内に配置された分子構造を有する化合物を含むことを特徴とする有機半導体材料、及び、ビシクロ構造を有する前駆体としてのチアポルフィリン骨格を有する化合物を溶媒に溶解した溶液を基板上に塗布し、加熱することにより、上記チアポルフィリン骨格を有する化合物に変換することを特徴とする有機半導体材料の製造方法、並びに、半導体層と2以上の電極とを有する有機電子デバイスにおいて、該半導体層が上記有機半導体材料を含むことを特徴とする有機電子デバイス。

(もっと読む)

有機トランジスタ及びその製造方法

【課題】有機ゲート絶縁膜の密着性を高めることができ、トランジスタ特性を向上させることができる有機トランジスタ及びその製造方法を得る。

【解決手段】基板1と、基板1上に設けられるゲート電極2と、ゲート電極2上に設けられる有機材料からなるゲート絶縁膜4と、ゲート絶縁膜4上に設けられる有機半導体層8と、有機半導体層8にチャネル領域を形成するため有機半導体層に接するように設けられるドレイン電極6及びソース電極7とを備え、ゲート電極4が、ゲート電極2上に設けられたフルオロカーボン膜3の上に形成されていることを特徴としている。

(もっと読む)

絶縁膜層分離IC製造

【課題】二酸化ケイ素や窒化ケイ素など非常に薄い低応力誘電体材料と半導体層とで形成された可とう性の膜で集積回路(24、26、28、...30)を製造する汎用手法を提供する。

【解決手段】膜(36)の半導体層中に半導体デバイス(24、26、28...30)を形成する。最初に、標準厚さの基板(18)から半導体膜層(36)を形成し、次いで、基板の薄い表面層をエッチングまたは研磨する。他のバージョンでは、ボンディングされた従来の集積回路ダイ用の支持および電気的相互接続として可とう性膜を使用し、膜中の複数の層に相互接続部を形成する。1つのそのような膜に複数のダイを接続することができ、膜は次いでマルチチップ・モジュールとしてパッケージされる。

(もっと読む)

N,N’−ビス(フルオロフェニルアルキル)で置換されたペリレン−3,4:9,10−テトラカルボキシイミド、ならびにその製造および使用

本発明は、式(I)のN,N’−ビス(フルオロフェニルアルキル)で置換されたペリレン−3,4:9,10−テトラカルボキシイミドと、その製造と、電荷輸送材料、励起子輸送材料、またはエミッタ材料としてのその使用とに関する。  (もっと読む)

(もっと読む)

透明有機薄膜トランジスタ

【課題】無色透明性の高い有機薄膜トランジスタ、該トランジスタを用いた透明半導体回路、および開口率の高い画像表示装置並びに受光装置を提供する。

【解決手段】半導体活性層に、膜厚30nmの薄膜としたときに可視域である400〜700nmの範囲の最大吸光度が0.2以下であるp型有機半導体材料を用いた透明有機薄膜トランジスタ。

(もっと読む)

有機半導体素子及びその製造方法

【課題】絶縁層の上に有機半導体層を設けた有機半導体素子において、移動度及びオン/オフ比などの半導体特性に優れた有機半導体素子及びその製造方法の提供。

【解決手段】絶縁層3と、絶縁層3上に設けられる有機半導体層5とを備える有機半導体素子であって、絶縁層3と有機半導体層5の間に、以下の一般式で表わされる共重合体からなる高分子層4が設けられていることを特徴としている。

(式中、R1、R2及びR3は、互いに同一であっても異なってもいてもよく、水素原子またはアルキル基を示す。x及びyは、0.001≦y/x<0.1の関係を満足する。)

(もっと読む)

重合体、それを含む有機膜及びトランジスタ

【課題】溶解性に優れ、空気安定性、高い移動度、ON/OFF比を有するビスチアゾール重合体を含む有機薄膜および有機薄膜トランジスタを提供すること。

【解決手段】下記一般式(1)で表わされる構成単位を含有することを特徴とする重合体。

(式中、R1、R2、R3及びR4は水素原子、ハロゲン原子、置換もしくは無置換のアルキル基またはアルコシキ基もしくはチオアルコキシ基から選択される基であり同一でも異なっていても良く、且つ、少なくとも一つが水素以外の置換基を有する。nは1以上の整数を示し、nが2以上の場合、R3およびR4は同一でも異なる基でもよい。)

(もっと読む)

半導体装置およびその製造方法

【課題】縦型MOSトランジスタの小型化、それに伴い増加する寄生抵抗、寄生容量の低減。

【解決手段】基板と、基板上の絶縁膜と、基板上の絶縁膜上に形成された平面状半導体層と、平面状半導体層に形成される第1のドレイン/ソース領域、平面状半導体層上に形成される柱状半導体層、柱状半導体層上部に形成される第2のソース/ドレイン領域、及び柱状半導体層の側壁を包囲するように絶縁膜を介して形成されるゲート電極を含む第1及び第2のMOSトランジスタとを備える半導体装置において、第1又は第2のMOSトランジスタの第2のソース/ドレイン領域の上面の面積は、第1又は第2のMOSトランジスタの柱状半導体層のそれぞれの上面の面積よりも大きく、第1のMOSトランジスタの第1のドレイン/ソース領域の表面の少なくとも一部と第2のMOSトランジスタの第1のドレイン/ソース領域の表面の少なくとも一部とを接続するシリサイド層が形成される。

(もっと読む)

III族窒化物半導体からなるトランジスタ

【課題】III族窒化物半導体の特性を最大限に引き出して低抵抗化を実現し、かつ、生産性にすぐれたパンチスルー型トランジスタを提供する。

【解決手段】この窒化物半導体素子は、基板1と、基板1の一方側に形成された窒化物半導体積層構造部2とを備え、パンチスルー型トランジスタを構成している。窒化物半導体積層構造部2は、n+型GaNドレイン層6と、n-型GaNドリフト層7と、p型GaNチャネル層4と、n+型GaNソース層5とを積層して形成されている。たとえば、動作電圧は400V、n-型GaNドリフト層7のドナー濃度が2×1016cm-3、p型GaNチャネル層4のアクセプタ濃度が3×1017cm-3であって、n-型GaNドリフト層7の層厚が、1μmとされている。

(もっと読む)

半導体装置およびその製造方法

【課題】縦型MOSトランジスタの小型化、それに伴い増加する寄生抵抗、寄生容量の低減。

【解決手段】基板と、基板上の絶縁膜と、基板上の絶縁膜上に形成された平面状半導体層と、平面状半導体層に形成される第1のドレイン/ソース領域、平面状半導体層上に形成される柱状半導体層、柱状半導体層上部に形成される第2のソース/ドレイン領域、及び柱状半導体層の側壁を包囲するように絶縁膜を介して形成されるゲート電極を含む第1及び第2のMOSトランジスタとを備える半導体装置において、第1又は第2のMOSトランジスタの第2のソース/ドレイン領域の上面の面積は、第1又は第2のMOSトランジスタの柱状半導体層のそれぞれの上面の面積よりも大きく、第1のMOSトランジスタの第1のドレイン/ソース領域の表面の少なくとも一部と第2のMOSトランジスタの第1のドレイン/ソース領域の表面の少なくとも一部とを接続するシリサイド層が形成される。

(もっと読む)

半導体装置

【課題】縦型MOSトランジスタの小型化、及びそれに伴って増加する寄生抵抗、寄生容量を低減すること。

【解決手段】基板と、基板上の絶縁膜と、基板上の絶縁膜上に形成された平面状半導体層と、平面状半導体層に形成されるドレイン又はソース領域、平面状半導体層上に形成される柱状半導体層、柱状半導体層上部に形成されるソース又はドレイン領域、及び柱状半導体層の側壁を包囲するように絶縁膜を介して形成されるゲート電極を含む第1及び第2のMOSトランジスタとを備える半導体装置において、第1のMOSトランジスタの平面状半導体層に形成されるドレイン又はソース領域の表面の少なくとも一部と第2のMOSトランジスタの平面状半導体層に形成されるドレイン又はソース領域の表面の少なくとも一部とを接続するシリサイド層が形成されている。

(もっと読む)

ナノデバイス、これを含むトランジスタ、ナノデバイス及びこれを含むトランジスタの製造方法

【課題】ナノデバイス、これを含むトランジスタ、ナノデバイス及びこれを含むトランジスタの製造方法を提供する。

【解決手段】ナノデバイスは、i)基板、ii)基板上に位置し、一つ以上の開口部を有するマスク層、及びiii)開口部の周縁に沿って基板の板面に実質的に垂直の方向に伸びたナノ壁またはナノチューブを含む。

(もっと読む)

半導体装置の製造方法

【課題】縦型MOSトランジスタの高集積化、高性能化。

【解決手段】基板上の絶縁膜上に平面状半導体層及び複数の平面状半導体層上の柱状半導体層を形成し、平面状半導体層を素子に分離し、平面状半導体層に不純物領域を形成し、その後に表面の少なくとも一部に絶縁膜を形成し、絶縁膜上に導電膜を形成し、絶縁膜及び前記導電膜をエッチバックし、柱状半導体層側面の絶縁膜及び導電膜を所望の長さに形成し、ゲート電極を形成し、導電膜及び絶縁膜を選択的にエッチングにより除去し、ゲート電極及び前記ゲート電極から延在するゲート配線を形成し、複数の柱状半導体層の各々に対応する複数のMOSトランジスタのうち、第1のMOSトランジスタの平面状半導体層に形成された不純物領域の表面の少なくとも一部と第2のMOSトランジスタの平面状半導体層に形成された不純物領域の表面の少なくとも一部とを接続する第1のシリサイド層を形成する。

(もっと読む)

半導体記憶装置

【課題】微細化しても、信号量が大きく、コンタクトによる端子間のショートを回避し、寄生抵抗を低くした半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、第1方向に延伸するビット線と、第2方向に延伸するワード線と、第1方向に沿った断面においてU状の半導体層と、半導体層の上部に設けられた第1拡散層と、半導体層の下部に設けられた第2拡散層と、第1拡散層と第2拡散層との間にある半導体層の中間部に形成されたボディと、U状半導体層の外側面に面する第1ゲート電極と、U状半導体層の内側面に面する第2ゲート電極と、ビット線コンタクトと、ソース線コンタクトとを備え、第1方向に隣接するメモリセルは、ビット線コンタクトおよびソース線コンタクトを交互に共有している。

(もっと読む)

141 - 160 / 320

[ Back to top ]