Fターム[5F110CC09]の内容

Fターム[5F110CC09]に分類される特許

81 - 100 / 320

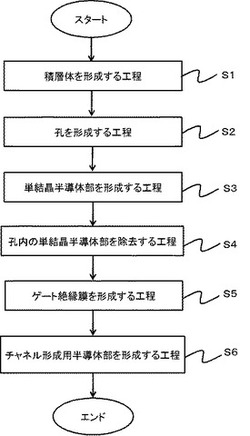

半導体装置の製造方法

【課題】ゲート電極を形成してからチャネル形成用半導体部を形成する方法において、結晶品質の良い単結晶Siを用いて良質なゲート絶縁膜を形成した縦型半導体装置を提供する。

【解決手段】単結晶半導体基板に少なくとも第1絶縁層を有する積層体を形成する工程S1と、前記積層体に、前記単結晶半導体基板が露出する孔を形成する工程S2と、前記孔の底面に露出している前記単結晶半導体基板を種結晶領域とすることにより、前記第1絶縁層の上にゲート電極となる単結晶半導体部を形成する工程S3と、前記孔内に埋められた前記単結晶半導体部を除去することで、前記孔の底面に前記単結晶半導体基板を再び露出させる工程S4と、前記単結晶半導体部の前記孔の側面に露出している部分にゲート絶縁膜を形成する工程S5と、前記孔にチャネル形成用半導体部を形成する工程S6と、を有する半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】三次元半導体であるsurrounding gate transistor(SGT)のオン電流を増加させることにより、SGTの高速動作を実現する半導体装置を提供することを課題とする。

【解決手段】ソース、ドレイン及びゲートが、基板上に階層的に配置される半導体素子であって、シリコン柱と、前記シリコン柱の側面を取り囲む絶縁体と、前記絶縁体を囲むゲートと、前記シリコン柱の上部又は下部に配置されるソース領域と、前記シリコン柱の上部又は下部に配置されるドレイン領域であって、前記シリコン柱に対して前記ソース領域と反対側に配置されるドレイン領域とを備え、前記シリコン柱と前記ソース領域との接触面は、前記シリコン柱と前記ドレイン領域との接触面より小さい半導体素子を提供することにより上記課題を解決する。

(もっと読む)

改良された閾値下の振れを有するトンネル電界効果トランジスタ

【課題】閾値下の振れが改良され、供給電圧が更に低減されたトンネル電界効果トランジスタを提供する。

【解決手段】高ドープドレイン領域3、低ドープチャネル領域2、高ドープソース領域1及び、高ドープソース領域1と接触する低ドープチャネル領域2の少なくとも一部を覆うゲート誘電体10およびゲート電極9を有し、ソース−チャネル界面12におけるゲート誘電体10の膜厚は、ソース−チャネル界面12から所定の距離離れたチャネル2上のゲート誘電体10の膜厚より小さい。

(もっと読む)

薄膜トランジスタ

【課題】ポリスチレンを塗布プロセスにより形成し不溶化処理を行うことで、半導体層を塗布プロセスで積層可能なポリスチレンからなる絶縁体層を有し、応答速度(駆動速度)が早く、オン/オフ比が大きい、優れたトランジスタ特性を有する薄膜トランジスタを提供する。

【解決手段】少なくとも基板上にゲート電極、ソース電極及びドレイン電極の3端子、絶縁体層並びに半導体層が設けられ、ソース−ドレイン間電流をゲート電極に電圧を印加することによって制御する薄膜トランジスタにおいて、前記絶縁体層が、塗布法により積層された層であって、有機溶媒に対して不溶化したポリスチレンからなる薄膜トランジスタ。

(もっと読む)

半導体装置

【課題】1個の柱を用いてインバータを構成することにより、高集積なCMOSインバータ回路からなる半導体装置を提供する。

【解決手段】第1のシリコンと、該第1のシリコンとは極性が異なる第2のシリコンと、前記第1のシリコンと前記第2のシリコンとの間に配置され、基板に対して垂直方向に延びている第1の絶縁物とからなる1本の柱と、前記第1のシリコンの上下のそれぞれに配置され、前記第1のシリコンとは極性が異なる第1の高濃度不純物を含むシリコン層と、前記第2のシリコンの上下のそれぞれに配置され、前記第2のシリコンとは極性が異なる第2の高濃度不純物を含むシリコン層と、前記第1のシリコンと前記第2のシリコンと前記第1の絶縁物とを取り囲む第2の絶縁物と、前記第2の絶縁物を取り囲む導電体とを含む半導体装置により、上記課題を解決する。

(もっと読む)

半導体装置

【課題】4個の島状半導体を用いてSRAMを構成することにより、高集積なSGTを用いたSRAMからなる半導体装置を提供することを目的とする。

【解決手段】第1の島状半導体層の周囲を取り囲む第1のゲート絶縁膜と、第1のゲート絶縁膜の周囲を取り囲む第1のゲート電極と、第1のゲート電極の周囲を取り囲む第2のゲート絶縁膜と、第2のゲート絶縁膜の周囲を取り囲む第1の筒状半導体層と、第1の島状半導体層の上部に配置された第1の第1導電型高濃度半導体層と、第1の島状半導体層の下部に配置された第2の第1導電型高濃度半導体層と、第1の筒状半導体層の上部に配置された第1の第2導電型高濃度半導体層と、第1の筒状半導体層の下部に配置された第2の第2導電型高濃度半導体層と、を有するインバータを用いたSRAMにより、上記課題を解決する。

(もっと読む)

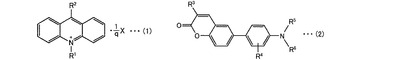

光照射によって誘電率が変化する膜およびそれを用いた電子デバイス

【課題】光照射によって誘電率を変化させることが可能な膜、およびそれを用いた電子デバイスを提供する。

【解決手段】薄膜トランジスタ20は、ガラス基板21、ゲート電極22、ゲート絶縁膜23、半導体層(活性層)24、ソース電極25およびドレイン電極26を備える。ゲート電極22、ゲート絶縁膜23および半導体層24は、この順序でガラス基板21上に積層されている。ソース電極25およびドレイン電極26は、半導体層24上に形成されている。ゲート絶縁膜23は、有機重合体と、その有機重合体中に分散された化合物とを含む溶液を、ガラス基板上に形成されたゲート絶縁膜上にスピンコート法によって塗布した。その化合物は、以下の式(1)で表される化合物および以下の(2)で表される化合物から選ばれる少なくとも1種の化合物である。[化学式(1)および(2)] (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】高集積なSGTを用いたCMOSインバータ回路からなる半導体装置を提供する。

【解決手段】第1のトランジスタは、島状半導体層と、島状半導体層の周囲を取り囲む第1のゲート絶縁膜と、第1のゲート絶縁膜の周囲を取り囲むゲート電極と、島状半導体層の上部に配置された第1の第1導電型高濃度半導体層と、島状半導体層の下部に配置された第2の第1導電型高濃度半導体層とを有し、第2のトランジスタは、ゲート電極の周囲の一部を取り囲む第2のゲート絶縁膜と、第2のゲート絶縁膜の周囲の一部に接する第2の半導体層と、第2の半導体層の上部に配置され、第1導電型高濃度半導体層と反対の極性を有する第1の第2導電型高濃度半導体層と、第2の半導体層の下部に配置され、第1導電型高濃度半導体層と反対の極性を有する第2の第2導電型高濃度半導体層とを有することにより、上記課題を解決する。

(もっと読む)

半導体装置

【課題】本発明では、高速化及び高集積化が可能な半導体素子、及びそれが高集積された

半導体装置、並びにこれらの作製方法を提供する。

【解決手段】 本発明は、基板の厚さ方向に積層されたソース領域、チャネル形成領域、

及びドレイン領域と、絶縁膜を介して前記チャネル形成領域と重畳するゲート電極とを有

し、前記チャネル形成領域は、極細炭素繊維で形成されている半導体装置である。本発明

の半導体装置は、極細炭素繊維をチャネル形成領域に有し、かつ基板表面に対して縦方向

に積層されている半導体素子を有するため、高集積化が可能である。

(もっと読む)

半導体装置とその製造方法

【課題】縦型トランジスタにおいて、柱状半導体層上のコンタクトと柱状半導体層の周囲に形成されるゲート電極のショートの抑制。

【解決手段】上方に平面状半導体層及び該平面状半導体層上の柱状半導体層が形成された基板に対して、柱状半導体層の上部に第2のドレイン/ソース領域を形成し、コンタクトストッパー膜を成膜し、コンタクト層間膜を成膜し、第2のドレイン/ソース領域上にコンタクトを形成し、ここでコンタクトの形成は、コンタクトのパターンを形成し、コンタクトのパターンを用いてコンタクト層間膜をコンタクトストッパー膜までエッチングすることにより、コンタクト用のコンタクト孔を形成し、コンタクト用のコンタクト孔の底部に残存するコンタクトストッパー膜をエッチングにより除去することを含み、コンタクト用のコンタクト孔の底面の基板への投影面は、柱状半導体層の上面及び側面に形成されたコンタクトストッパー膜の基板への投影形状の外周内に位置する。

(もっと読む)

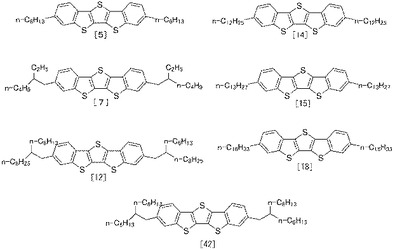

置換ベンゾカルコゲノアセン化合物、該化合物を含有する薄膜及び該薄膜を含有する有機半導体デバイス

【課題】有機半導体材料として好適な新規化合物の提供。

【解決手段】下式で表わされる、置換ベンゾカルコゲノアセン化合物、該化合物を含む薄膜及び該薄膜を構成成分にもつ有機半導体デバイス。 (もっと読む)

(もっと読む)

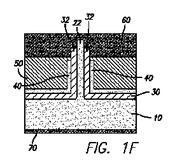

半導体装置及びその製造方法

【課題】半導体基板上に容易なプロセスにより、微細で、高速なSOI構造の縦型のMISFETを得ること。

【解決手段】半導体基板1上に酸化膜2を介して、下部に配線層3を有する自己整合の横及び縦方向エピタキシャル半導体層からなる凸状構造の半導体層6が設けられ、凸状構造の半導体層6は素子分離領域埋め込み絶縁膜4及び酸化膜2により島状に絶縁分離されている。凸状構造の半導体層6の上部には高濃度及び低濃度ドレイン領域10、9が設けられ、下部には高濃度及び低濃度ソース領域7、8が設けられ、側面にはゲート酸化膜11を介してゲート電極12が設けられ、高濃度ドレイン領域10、下層配線3を介した高濃度ソース領域7及びゲート電極12には、それぞれバリアメタル18を有する導電プラグ19を介してバリアメタル21を有するCu配線22が接続されている自己整合連続縦横エピタキシャル成長法によるMISFET。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート電極7作製後にチャネル部12を作製する縦型MISFETの製造方法において、ゲート絶縁膜10に損傷を与えたり移動度を劣化させたりすることなく、孔底面に形成された絶縁膜や、自然酸化膜を除去する。

【解決手段】単結晶半導体基板1または単結晶半導体層に形成された不純物領域8の上に、第一絶縁層4、5と、ゲート電極層7と、第二絶縁層5、4と、をこの順に積層した積層体を形成し、前記積層体に不純物領域8が露出する孔を形成し、少なくとも前記孔の側壁に露出しているゲート電極層7、および、前記孔の底面に露出している不純物領域8の上に絶縁膜10を形成し、ゲート電極層7の露出部分の上に形成された絶縁膜10の上に半導体膜を重ねて形成し、不純物領域8の上に形成された絶縁膜を除去し、孔の底面に露出している不純物領域8に接し、孔底面から孔の開口部までつながる半導体部を形成する半導体装置の製造方法を提供する。

(もっと読む)

パッシベートされたシリコンナノワイヤーの製造方法およびこれにより得られるデバイス

パッシベートされたシリコンナノワイヤーの製造方法およびこれにより得られる電子構造体について記載する。こうした構造体は、金属−酸化物−半導体(MOS)構造を含むことができ、構造体はMOS電界効果トランジスタ(MOSFET)または光電子スイッチに用いることができる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】4個の島状半導体を用いてSRAMを構成することにより、高集積なSGTを用いたSRAMからなる半導体装置を提供する。

【解決手段】第1の島状半導体層137の周囲上に少なくとも一部に接して第1のゲート絶縁膜187が存在し、第1のゲート絶縁膜187に第1のゲート電極178の一面が接し、第1のゲート電極178の他面に第2のゲート絶縁膜187が接し、第2のゲート絶縁膜187に少なくとも第2の半導体層141が接して、第1の島状半導体層137の上部に配置された第1の第1導電型高濃度半導体層161と、第1の島状半導体層137の下部に配置された第2の第1導電型高濃度半導体層162と、第2の半導体層141の上部に配置された第1の第2導電型高濃度半導体層154と、第2の半導体層141の下部に配置された第2の第2導電型高濃度半導体層156と、を有するインバータを用いてSRAMを形成する。

(もっと読む)

新規な縮合芳香環化合物及びそれを用いた有機薄膜トランジスタ

【課題】容易に合成可能であり、酸化安定性に優れる有機化合物並びにそれを利用した有機薄膜トランジスタ及び有機薄膜発光トランジスタを提供する。

【解決手段】下記式(1)で表わされる有機薄膜トランジスタ用化合物。

[式中、R1〜R4は、それぞれ独立に、水素原子等であり、Xは、それぞれS、O、Se及びTeから選択されるいずれかの原子であり、Yは、それぞれN又はC−R5(R5は前記R1〜R4と同様の基を表す。)である。R1〜R5の隣接する2つの基は互いに連結し、炭素数6〜60の芳香族炭化水素基、又は炭素数1〜60の芳香族複素環基を形成してもよく、また、R5同士で互いに連結し、炭素数6〜60の芳香族炭化水素基、又は炭素数1〜60の芳香族複素環基を形成してもよい。]

(もっと読む)

半導体装置

【課題】三次元半導体であるSGTのリーク電流の増加による消費電力の増大を解決し、SGTの低消費電力を実現する半導体装置を提供すること。

【解決手段】第一導電型の第一シリコン柱と、その側面を囲む第一の絶縁体とその絶縁体を囲むゲートがあり、第一シリコン柱の下部に第二シリコン柱、上部に第三シリコン柱が備わり、第二シリコン柱の第一シリコン柱との接触面を除く面に形成された第二導電型の高濃度不純物領域と、第二シリコン柱に形成された第二導電型の高濃度不純物領域に囲まれた第一導電型不純物領域と、第三シリコン柱の第一シリコン柱との接触面を除く面に形成された第二導電型の高濃度不純物領域と、第三シリコン柱に形成された第二導電型の高濃度不純物領域に囲まれた第一導電型不純物領域から構成されており、第二シリコン柱と第三シリコン柱の第一導電型不純物領域が第二シリコン柱と第三シリコン柱の底部から伸びる空乏層領域より大きい。

(もっと読む)

半導体装置及びその製造方法

【課題】複数のゲート長を有するトランジスタを形成することができる半導体装置の製造方法を提供する。

【解決手段】半導体基板上に、第1の柱状体と第2の柱状体とを形成する工程と、前記第1及び第2の柱状体と前記半導体基板とを覆う半導体膜であって、前記第1の柱状体を覆う第1の部分と前記第2の柱状体を覆う第2の部分との導電型及び不純物の濃度の少なくとも一方が互いに異なるように半導体膜を形成する工程と、前記半導体膜をエッチバックして、前記第1及び第2の柱状体のそれぞれの側壁に、互いに異なる高さを有する第1の半導体膜柱状部と第2の半導体膜柱状部とを形成する工程と、を備えることを特徴とする半導体装置の製造方法を採用する。

(もっと読む)

有機電界効果トランジスタ

【課題】有機トランジスタの導電特性を改良し、高強度の電流を得られるようにする。

【構成】ソース電極6及びドレイン電極8間の半導体層10中に、導電性チャンネルに近接し、又は電気絶縁層20及び前記半導体層10に対して、ゲート電極22の反対側に位置する圧電層23を備え、該圧電層23は、前記ソース電極6及びドレイン電極8から、及び前記半導体層10から絶縁されている。

(もっと読む)

逆耐圧を有する縦型窒化ガリウム半導体装置

【課題】逆阻止能力を有し、低オン抵抗で高速スイッチング特性を有する素子を提供すること。

【解決手段】シリコン基板101と、シリコン基板101上に形成されたバッファ層102,103と、バッファ層102、103上に形成された窒化ガリウム半導体層104と、シリコン基板101の裏面からシリコン基板101ならびにバッファ層102、103を貫通して窒化ガリウム半導体層104に達する深さで形成されたトレンチ溝112と、このトレンチ溝112の中に形成された金属膜113と、を備え、金属膜113と窒化ガリウム半導体層104とがショットキー接合を形成する逆耐圧を有する窒化ガリウム半導体装置とする。

(もっと読む)

81 - 100 / 320

[ Back to top ]