Fターム[5F110CC09]の内容

Fターム[5F110CC09]に分類される特許

21 - 40 / 320

半導体装置

【課題】信頼性の高い、酸化物半導体を有する半導体装置。

【解決手段】酸化物半導体層は、ソース電極と重なる第1の領域と、ドレイン電極と重なる第2の領域と、ソース電極及びドレイン電極と重ならない第3の領域と、を有し、記第3の領域における酸化物半導体層の膜厚は、第1の領域及び第2の領域における酸化物半導体層の膜厚よりも小さく、第3の領域における酸化物半導体層の一端部は、第1のテーパを有し、記第3の領域における酸化物半導体層の他端部は、第2のテーパを有し、ソース電極の端部は、第3のテーパを有し、ドレイン電極の端部は、第4のテーパを有し、第1のテーパと、第3のテーパとは連続した形状を有し、第2のテーパと、第4のテーパとは連続した形状を有する半導体装置である。

(もっと読む)

半導体装置

【課題】半導体基板上へのVFETと他の種類の素子との混載が可能でありながら、半導体基板上に積層される半導体層の表面に大きな段差を有しない半導体装置を提供する。

【解決手段】P型シリコン基板2上には、酸化シリコンからなるボックス層3、N+型横方向導電層4およびN−型表面層5が積層されている。ボックス層3上には、N−型表面層5の表面からボックス層3に至る深さを有する、平面視環状のディープトレンチ6が形成されている。ディープトレンチ6およびボックス層3に取り囲まれるトランジスタ形成領域8は、その周囲から分離されている。このトランジスタ形成領域8において、N−型表面層5の表層部には、ソース領域14およびドレイン領域16が形成されている。またディープトレンチ6の側面に沿って、ドレイン領域16とN+型横方向導電層4とに接続されたN+型縦方向導電層17が形成されている。

(もっと読む)

半導体メモリ装置および半導体メモリ装置の作製方法

【課題】高度に集積化したゲインセル方式の半導体メモリを提供する。

【解決手段】第1絶縁体101、読み出しビット線102b、第2絶縁体103、第3絶縁体103、第1半導体膜105、第1導電層107a乃至107d等を形成し、その上に凸状絶縁体112を形成する。そして、凸状絶縁体112を覆って、第2半導体膜114a、114bと第2ゲート絶縁膜115を形成する。その後、導電膜を形成し、これを異方性エッチングすることで、凸状絶縁体112の側面に書き込みワード線116a、116bを形成し、凸状絶縁体112の頂部に書き込みビット線125へ接続するための第3コンタクトプラグ124を形成する。このような構造でメモリセルの面積を最小で4F2とできる。

(もっと読む)

アクセプター性の基を有する化合物、これを用いた有機薄膜及び有機薄膜素子

【課題】本発明の目的は、電子輸送性に優れる有機n型半導体として利用可能な化合物を提供することにある。本発明の目的はまた、係る化合物を含む有機薄膜、及びこの有機薄膜を備える有機薄膜素子を提供することにある。

【解決手段】かご状化合物又は脂肪族炭化水素化合物から誘導される4価以上の基であるコア部と、該コア部に結合した4以上の側鎖基と、を備え、側鎖基のうち2以上がアクセプター性の基を有する、化合物。

(もっと読む)

縦型電界効果トランジスタとその製造方法及び電子機器

【課題】縦型電界効果トランジスタとその製造方法及び電子機器において、チャネルの下地の材料の選択の幅を広げると共に、縦型電界効果トランジスタのオン抵抗が上昇するのを抑制すること。

【解決手段】基材1と、基材1の上に形成されたソース電極2と、基材1の上に形成され、ソース電極2に重なる開口12を備えた第1の絶縁膜3と、開口12の横の第1の絶縁膜3の上に形成されたゲート電極6と、開口12の側面に形成されたゲート絶縁膜16と、第1の絶縁膜3の上に形成され、開口12に繋がる凹部8aを備えた第2の絶縁膜8と、開口12と凹部8aのそれぞれの内側と第2の絶縁膜8の上に形成され、酸化物半導体を材料とするチャネル17と、凹部8aの横の前記チャネル17の上に形成されたドレイン電極19とを有する縦型電界効果トランジスタによる。

(もっと読む)

多環縮環化合物、多環縮環重合体及びこれらを含む有機薄膜

【課題】高い電荷輸送性を発揮し得る構造を有するとともに、溶媒への溶解性にも優れる多環縮環重合体を提供すること。

【解決手段】式(1)で表される構造単位を有する多環縮環重合体。 (もっと読む)

(もっと読む)

縦型電界効果トランジスタとその製造方法及び電子機器

【課題】縦型電界効果トランジスタとその製造方法及び電子機器において、基材の材料の選択の幅を広げること。

【解決手段】基材1と、基材1の上に形成され、ソース電極とドレイン電極のうちの一方となる第1の電極2と、基材1の上に形成され、第1の電極2に重なる開口12を備えた第1の絶縁膜3と、開口12の横の第1の絶縁膜3の上に形成されたゲート電極6と、第1の絶縁膜3の上に形成され、開口12を備えた第2の絶縁膜8と、開口12の横の第2の絶縁膜8の上に形成され、ソース電極とドレイン電極のうちの他方となる第2の電極10と、開口12の側面に形成されたゲート絶縁膜16と、第1の電極2、第2の電極10、及びゲート絶縁膜16上に形成され、酸化物半導体を材料とするチャネル17とを有する縦型電界効果トランジスタによる。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート動作に関与する結晶表面における表面電荷蓄積を大幅に低減し、ピンチオフ特性が得られる、高性能のInN系FETを提供すること。

【解決手段】チャネル層としてInN系半導体を含む電界効果トランジスタである半導体装置であって、InN系半導体でなるチャネル層2の表面(c面)に、段差を形成して窒化物半導体の六方晶結晶のa面もしくはm面でなる側壁面2aを形成し、この側壁面2aにゲート電極6が配置され、ゲート電極6を挟むようにソース電極3とドレイン電極4がc面上に形成されている。

(もっと読む)

ポリマー薄膜における自己整合ビアホールの形成

【課題】有機電界効果トランジスタにおけるビア形成を、低コストで効率的なプロセスで実現する。

【解決手段】誘電層106内にビア113を形成する際、まず各ビア位置にパターン化された導電材よりなるポストを印刷し、次にパターン化されていない誘電層106を堆積させ、次に第2のパターン化された導電層を堆積させる。ビア113は、誘電層106を堆積した後、第2の導電層を堆積する前に、ポストをフラッシュアニールすることにより形成される。

(もっと読む)

SOI型トランジスタ

【課題】DRAMメモリアレイに用いられるセミコンダクタ・オン・インシュレータ型トランジスタを提供する。

【解決手段】SOI型のトランジスタは、半導体物質層60(SOI層)と、この半導体物質層60の内部を通って走るゲート線65a,65b,66cと、このゲート線65a,65b,66cに沿ってソース拡散領域70a、70b、70cよりも遠くまで延びるドレイン拡散領域64と、このドレイン拡散領域64よりも上方にあるソース拡散領域70a、70b、70cと、ドレイン拡散領域64まで延びるドレインコンタクト79と、ソース拡散領域まで延びるソースコンタクトと、を備え、これらドレインコンタクト79及びソースコンタクトは、ゲート線65a,65b,66cと平行に走る平面内にある。

(もっと読む)

トランジスタおよびメモリアレイ

【課題】大きな順方向−逆方向電流比を有するスイッチングデバイスを提供する。

【解決手段】トランジスタは、ソースと、ドレインと、ゲート領域と、ソースバリヤと、ドレインバリヤとを含む。ゲート領域は、ゲートと、アイランドと、ゲート酸化物とを含み、ゲート酸化物は、ゲートとアイランドとの間に配置される。ゲートおよびアイランドは、互いに、同時活性的に結合される。ソースバリヤはゲート領域からソースを分離し、ドレインバリヤはゲート領域からドレインを分離する。

(もっと読む)

含窒素縮合環化合物、含窒素縮合環重合体、有機薄膜及び有機薄膜素子

【課題】優れた電子輸送性を有する有機n型半導体として利用可能な新規化合物及び新規重合体の提供。

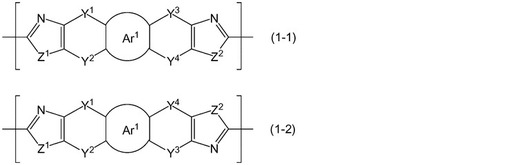

【解決手段】式(1−1)及び式(1−2)で表される構造単位からなる群より選択される、含窒素縮合環化合物。

[式中、Ar1は、芳香環を示し、Y1及びY2のうちいずれか一方は、−C(=X1)−で表される基を示し、他方は、単結合を示し、Y3及びY4のうちいずれか一方は、−C(=X2)−で表される基を示し、他方は、単結合を示し、X1及びX2は、酸素原子等を示し、Z1及びZ2は、酸素原子等を示す。]

(もっと読む)

埋め込み配線を備える基板、その製造方法、これを利用する半導体装置およびその製造方法

【課題】 低抵抗の埋め込み配線を備える基板の製造方法を提供する。

【解決手段】 始めに半導体用基板100の第1面S1上に導電層120を形成する。次に、導電層120をパターニングして第1方向に延長する線形の導電層パターン122を形成する。導電層120をパターニングするとき露出する半導体用基板100をエッチングして導電層パターン120の下部に第1方向に延長する線形の半導体パターン104を形成する。次に導電層パターン120および半導体パターン104上に絶縁層150を形成する。半導体用基板100の第1面S1側の絶縁層150が支持基板160と当接するように支持基板160上に配置する。次に半導体用基板100のイオン注入層102側の絶縁層150が露出するように半導体用基板100を除去する。これにより、導電層パターン120は、半導体パターン104の埋め込み配線として利用することができる。

(もっと読む)

ダイヤモンド電子素子及びその製造方法

【課題】欠陥密度が低減したドリフト層を有する高出力ダイヤモンド電子素子を提供する。

【解決手段】ダイヤモンド半導体からなるドリフト層と、半絶縁性ダイヤモンド層を有する構造保持材と、ダイヤモンド半導体からなるコンタクト層とを備えるダイヤモンド電子素子であって、前記構造保持材は、開口部を有し、前記ドリフト層の一方の面に積層されており、前記コンタクト層は、前記開口部内において、前記ドリフト層に直接積層されており、また、アノード電極は、前記開口部内の前記コンタクト層に設け、カソード電極は前記ドリフト層の他方の面に設けて、例えば、ショットキーバリアダイオードを実現する。単結晶ダイヤモンド基板の一方の基板面に欠陥層を形成した後、該基板面上に前記ドリフト層を成膜し、半絶縁性ダイヤモンド層を選択的に成長させて開口部を有する構造保持材を形成した後、前記基板はスマートカット法により素子部より分離する。

(もっと読む)

ダイヤモンド電子素子及びその製造方法

【課題】欠陥密度が低減したドリフト層を有する高出力ダイヤモンド電子素子を提供する。

【解決手段】半絶縁性単結晶ダイヤモンド基板の一方の面に、p−ダイヤモンド層からなるドリフト層を成膜し、該ドリフト層の上にp+ダイヤモンド層からなるコンタクト層を成膜する工程と、前記基板の他方の面に開口部をエッチングにより形成して、前記基板を構造保持材として前記ドリフト層の一部が露出した露出部を形成する工程と、前記露出部にカソード電極を設け、前記コンタクト層にアノード電極を設ける工程とにより、ダイヤモンド電子素子の積層構造を形成する。ドリフト層を基板上に直接成膜するので、欠陥密度の減少した素子を得ることができる。

(もっと読む)

有機薄膜トランジスタ用化合物及びそれを用いた有機薄膜トランジスタ

【課題】酸化安定性と塗布プロセスが適用可能な溶解性を有する有機薄膜トランジスタ用化合物を提供する。

【解決手段】下記式(1)で表わされる有機薄膜トランジスタ用化合物。 (もっと読む)

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

有機トランジスタ

【課題】電界効果移動度が高い有機トランジスタ、及びキャリア移動度が高い化合物を提供する。

【解決手段】ソース電極、ドレイン電極、ゲート電極、活性層及び絶縁層を有し、該活性層に式

〔式中、Yは、−O−、−S−又は−Se−を表す。Zは、各々独立して、水素原子又は置換基を表す。ただし、少なくとも1つのZは、ハメットのσp値が0.3以上である置換基である。〕で表される化合物を含む有機トランジスタ。

(もっと読む)

ストリング選択線及びビット線の改善されたコンタクトレイアウトを有する3次元メモリアレイ

【課題】インターコネクト及びコンタクト用の実装面積が小さい3次元集積回路メモリ用の構造を低製造コストで提供する。

【解決手段】3次元メモリデバイスは、絶縁材料21,22,23,24で分離され、復号化回路を介してセンスアンプに結合可能なビット線BLnとして導電材料の複数の帯片の形状をしている。導電材料帯片11,12,13,14は、スタック横面に側面を有する。ワード線WLn,WLn+1の複数の導電線16,17は行デコーダに結合でき、複数のスタック上で直交して延びる。導電線は、スタックの表面に共形である。記憶素子は、スタック上の半導体材料帯片の側面と導電線の間の交点の界面領域の多層アレイに設けられる。3次元メモリは、複数層に対する2つの最小線幅のマスクで作られる。半導体材料帯片の端部に階段構造が含まれる。半導体材料帯片に平行な金属層上と、ワード線に平行な上部金属層上にSSLインターコネクトを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】良好な特性を有しながら、半導体製造工程における半導体製造装置と半導体装置とへの金属汚染を抑制するような構造を有する半導体装置、および、その製造方法を提供する。

【解決手段】本発明の半導体装置は、nMOS SGT220であり、第1の平面状シリコン層上234に垂直に配置された第1の柱状シリコン層232表面に並んで配置された、第1のn+型シリコン層113と、金属を含む第1のゲート電極236と、第2のn+型シリコン層157とから構成される。そして、第1の絶縁膜129が、第1のゲート電極236と第1の平面状シリコン層234との間に、第2の絶縁膜162が第1のゲート電極236の上面に配置されている。また、金属を含む第1のゲート電極236が、第1のn+型シリコン層113、第2のn+型シリコン層157、第1の絶縁膜129、および、第2の絶縁膜162に囲まれている。

(もっと読む)

21 - 40 / 320

[ Back to top ]