Fターム[5F110CC09]の内容

Fターム[5F110CC09]に分類される特許

41 - 60 / 320

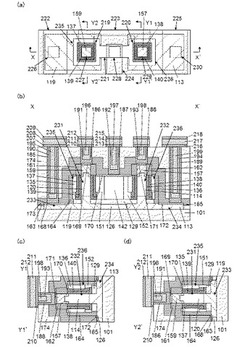

半導体装置及びその製造方法

【課題】良好な特性を有しながら、半導体製造工程における半導体製造装置と半導体装置とへの金属汚染を抑制するような構造を有する半導体装置、および、その製造方法を提供する。

【解決手段】本発明の半導体装置は、nMOS SGT220であり、第1の平面状シリコン層上234に垂直に配置された第1の柱状シリコン層232表面に並んで配置された、第1のn+型シリコン層113と、金属を含む第1のゲート電極236と、第2のn+型シリコン層157とから構成される。そして、第1の絶縁膜129が、第1のゲート電極236と第1の平面状シリコン層234との間に、第2の絶縁膜162が第1のゲート電極236の上面に配置されている。また、金属を含む第1のゲート電極236が、第1のn+型シリコン層113、第2のn+型シリコン層157、第1の絶縁膜129、および、第2の絶縁膜162に囲まれている。

(もっと読む)

垂直型ナノチューブ半導体デバイス構造体の形成方法

【課題】 大量生産技術に対応した、チャネル領域として1つ又は複数の半導体カーボン・ナノチューブを組み込む垂直型FET構造体を提供する。

【解決手段】 少なくとも1つのナノチューブ14を組み組む垂直型デバイス構造体42を製造する方法である。各々のナノチューブ14は、触媒パッド10によって触媒作用が及ぼされる化学気相成長法によって成長され、誘電体材料22のコーティング内に包み込まれる。包み込まれたナノチューブがゲート電極30の厚さを通って垂直方向に延びるように、該包み込まれたナノチューブの周りにゲート電極を形成することによって、垂直型電界効果トランジスタを作ることができる。包み込まれたナノチューブ、及び該包み込められたナノチューブを支持する対応する触媒パッドが1つのキャパシタ・プレートを形成するように、キャパシタ構造50を作ることができる。

(もっと読む)

半導体装置とその製造方法

【課題】良好な特性を有し且つ微細化を実現した半導体装置とその製造方法を提供する。

【解決手段】半導体装置は、平面状シリコン層212上の柱状シリコン層208、柱状シリコン層208の底部領域に形成された第1のn+型シリコン層113、柱状シリコン層208の上部領域に形成された第2のn+型シリコン層144、第1及び第2のn+型シリコン層113,144の間のチャネル領域の周囲に形成されたゲート絶縁膜140、ゲート絶縁膜140の周囲に形成され第1の金属シリコン化合物層159aを有するゲート電極210、ゲート電極210と平面状シリコン層212の間に形成された絶縁膜129a、柱状シリコン層208の上部側壁に形成された絶縁膜サイドウォール223、平面状シリコン層212に形成された第2の金属シリコン化合物層160、及び第2のn+型シリコン層144上に形成されたコンタクト216を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】オフ電流を低減し、特性ばらつきが抑制された多結晶半導体層をチャネル領域とする半導体装置の製造方法を提供する。

【解決手段】半導体基板の上に絶縁体層を形成する工程と、絶縁体層上に狭窄部を有する非晶質または多結晶質の半導体層を形成する工程と、半導体層上に半導体層よりも熱膨張係数の大きい絶縁体層を形成する工程と、熱処理を行う工程と、絶縁体層を除去する工程と、狭窄部の側面にゲート絶縁膜を形成する工程と、ゲート絶縁膜上にゲート電極を形成する工程と、半導体層中にソース・ドレイン領域を形成する工程と、を有することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】第1、第2素子形成領域間でノイズが伝播することを抑制することができる半導体装置を提供することを目的とする。

【解決手段】第1、第2素子形成領域20、30に形成された半導体素子のうち、第1素子形成領域20に形成された半導体素子を外部機器と接続し、第1素子形成領域20と第2素子形成領域30との間に、第1導電型層60と、当該第1導電型層60に挟まれる第2導電型層61とを配置し、第1、第2導電型層60、61の間に、オフ時に半導体層12の表面から埋込絶縁膜11に達し、第1、第2素子形成領域20、30との間を仕切る空乏層63、64を構成する。

(もっと読む)

垂直TFETの製造方法

【課題】ヘテロ構造ナノワイアを有するトンネル電界効果トランジスタと集積されたナノワイアを有する相補型トンネル電界効果トランジスタの製造方法を提供する。

【解決手段】犠牲材料21の層を有するチャネル材料34の層を含むスタック24を形成する工程と、チャネル材料34の層と犠牲材料21の層から、少なくとも1つのナノワイヤ30を形成するために、スタック24から材料を除去する工程と、第1ドーパント型の少なくとも1つのナノワイヤ30中の犠牲材料21を第1ドーパント型のヘテロ接合材料41で置き換えて、その後に、第2ドーパント型の少なくとも1つのナノワイア中の犠牲材料を、第2ドーパント材料のヘテロ接合材料52で置き換える工程を含み、相補型TFETの容易な製造が可能となる。

(もっと読む)

半導体素子

【課題】垂直に形成されたナノワイヤを構成要素として備える半導体素子の寄生容量増加を抑制し、動作速度時定数が改善される半導体素子を提供する。

【解決手段】導電性基板101の主平面と電極109間の層間絶縁膜を膜厚調整層102と保護絶縁層103の2層化することにより、膜密着性の乏しい低誘電率膜102と電極109を保護絶縁層103で隔てることによってはがれを抑制しながら、主平面101と電極109間を電気的に接続するナノワイヤ107と、導電性基板101と電極109の間の寄生容量を低減する。

(もっと読む)

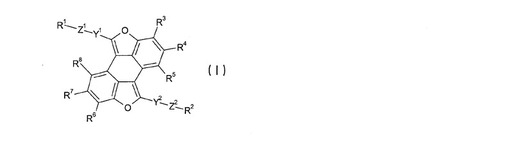

半導体装置及びその製造方法

【課題】SOI構造の縦型のMISFETの提供

【解決手段】Si基板1上に、一部に空孔4を有する絶縁膜2が設けられ、空孔4上及び絶縁膜2の一部上に横方向半導体層6が設けられ、半導体層6の側面の一部に導電膜3が接して設けられ、絶縁膜2により素子分離されている。半導体層6上の、空孔4直上部に縦方向半導体層7が設けられ、半導体層7の上部にドレイン領域(10,9)が設けられ、離間し、相対して下部にソース領域8が設けられ、ソース領域8は延在して、半導体層6全体に設けられている。半導体層7の全側面には、ゲート酸化膜11を介してゲート電極12が設けられ、ドレイン領域10、ゲート電極11及び導電膜3を介したソース領域8には、バリアメタル18を有する導電プラグ19を介してバリアメタル21を有する配線22が接続されている縦型のMISFET。

(もっと読む)

半導体装置

【課題】特性が良好であって、かつ大電力用途向けの半導体装置を提供することを課題とする。

【解決手段】半導体装置、具体的には縦型トランジスタのゲート電極層の一部を、ソース電極層、ドレイン電極層およびチャネル領域となる半導体層の一部と重畳する構造にすることである。つまり、ソース電極層と、ソース電極層に接した酸化物半導体層と、酸化物半導体層に接したドレイン電極層と、一部がソース電極層、ドレイン電極層および酸化物半導体層と重畳したゲート電極層と、ゲート電極層の全ての面に接するゲート絶縁層と、を有する半導体装置を提供することである。

(もっと読む)

電気光学装置及び電子機器

【課題】電気光学装置において画素の狭ピッチ化、高精細化と共に高開口率を実現する。

【解決手段】TFT(30)の半導体層(1a)は、交差部(Cr)に重なる開孔部(3

5)内から開孔部(35)外にまで連続的に形成されると共に、開孔部(35)の底面に

露出するデータ線(6)の表面部分と電気的に接続される第1のソースドレイン領域(1

b)と、開孔部(35)の側壁に配置されたチャネル領域(1a')と、開孔部(35)

外に形成され画素電極(9)と電気的に接続される第2のソースドレイン領域(1c)と

を有し、TFT(30)のゲート電極(3a)は、少なくともチャネル領域(1a')に

重なるように開孔部(35)内に形成され、走査線(11)と電気的に接続される。

(もっと読む)

半導体装置

【課題】高集積なCMOS型SRAMを提供する。

【解決手段】第1の第1導電型半導体137と、第1の第1導電型半導体とは極性が異なる第1の第2導電型半導体104と、第1の第1導電型半導体137と第1の第2導電型半導体104との間に配置される第1の絶縁物112が一体となり基板に対して垂直に延びる1本の第1の柱と、第1の第1導電型半導体137の上下に配置された第1の第2導電型高濃度半導体182と、第2の第2導電型高濃度半導体141と、第1の第2導電型半導体104の上下に配置された第1の第1導電型高濃度半導体186と、第2の第1導電型高濃度半導体143と、第1の柱を取り囲む第1のゲート絶縁物176と、第1のゲート導電体167と、を有するインバータを用いてSRAMを構成する。

(もっと読む)

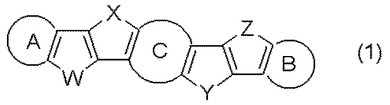

多環式化合物及び有機半導体デバイス

【課題】有機半導体活性層の薄膜を与え得る新規化合物の提供。

【解決手段】式(1)

(式中、環構造Cは、式(C1)、式(C2)または式(C3)で示される環を表わす。

(式中、PおよびQは、硫黄原子、酸素原子、セレン原子またはテルル原子を表わす。W、X、YおよびZは、硫黄原子、セレン原子またはN−(R15)等を表わす。環構造Aおよび環構造Bは、芳香族性炭素環または芳香族性複素環を表わす。R15はアルキル基を表わす。))で示される多環式化合物。

(もっと読む)

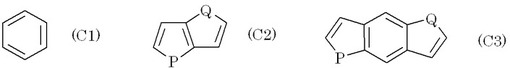

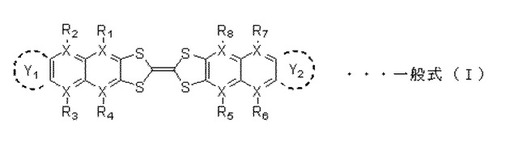

新規ビベンゾ[b]フラン化合物、並びに該化合物を含有してなる有機半導体材料及び有機半導体素子

【課題】製造が容易であり、有機半導体材料として半導体素子に用いた際に高いキャリア移動度を実現できる新規な化合物の提供。

【解決手段】下記一般式(I)で表されるビベンゾ[b]フラン化合物。式中、R1及びR2は、水素原子、ハロゲン原子、アルキル基、アリール基、複素環基又はトリアルキルシリル基を表し、R3〜R8は、水素原子、ハロゲン原子、アルキル基、アルコキシ基、チオアルキル基、アリール基又は複素環基を表し、Y1、Y2、Z1及びZ2は、直接結合、−O−、−S−、−CH=CH−、−C≡C−又はアリーレン基を表す。 (もっと読む)

(もっと読む)

埋立ビットラインを有する半導体装置及び半導体装置の製造方法

【課題】埋立ビットラインを有する半導体装置及び半導体装置の製造方法を提供すること。

【解決手段】埋立ビットラインを備えて低抵抗を有する垂直ピラートランジスタを含む半導体装置及びその製造方法が開示される。垂直ピラートランジスタは、基板上に形成され、下部と上部を有する本体、本体の上部に配置されるソース/ドレインノード、そして、本体の下部に配置されるドレイン/ソースノードを含む。半導体装置は、少なくとも本体の下部の上部表面に形成され、金属シリサイドを含む前記埋立ビットライン及び前記本体の上部を部分的に包むワードラインを備える。

(もっと読む)

半導体デバイスの製造方法

【課題】 垂直に形成されたナノワイヤの長さを再現性良く作製する。

【解決手段】 半導体デバイスの製造方法であって、基板101の上に第1の層102を形成する工程と、第1の層の上に、第1の層よりヤング率が高いストップ層103を形成する工程と、第1の層及び前記ストップ層の一部をそれぞれ除去して前記基板の一部が露出するように凹部108を形成する工程と、凹部に、第1の層の厚さとストップ層の厚さの和よりも大きな長さを有するように、前記基板の表面に対して垂直方向に延びるナノワイヤ107を、成長させる成長工程と、前記ナノワイヤが成長した前記凹部に、前記和よりも大きい膜厚を有し、ヤング率が前記ストップ層よりも低い平坦化層を形成する工程と、平坦化層108を、ストップ層まで除去し、ナノワイヤを平坦化層の表面から露出させる工程と、ナノワイヤの上端に接続される電極を形成する工程と、を有する。

(もっと読む)

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法に対する様々な実施例が与えられる。一実施例では、半導体デバイスは、ゲート層、誘電体層、メモリ層、ソース層、半導体チャネル層、及びドレイン層を含む。ソース層は電気的浸透性及びパーフォレーションを有する。半導体チャネル層はソース層及びメモリ層と接触する。ソース層及び半導体チャネル層は、ゲート電圧チューナブル電荷注入バリアを形成する。  (もっと読む)

(もっと読む)

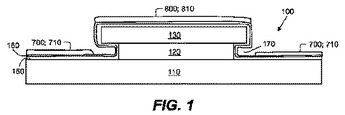

内側にへこんだ形状を含んだ縦型トランジスタ

トランジスタは、基板と、導電材料層と、電気絶縁材料層とを含んでいる。該基板、該導電材料層、及び該電気絶縁材料層のうちの1つ以上の少なくとも一部が凹部形状を画成している。

(もっと読む)

(もっと読む)

信号処理回路、及び信号処理回路の駆動方法

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる記憶装置、当該記憶装置を用いた信号処理回路の提供を目的の一つとする。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積及び放出を制御するスイッチング素子とを設ける。上記スイッチング素子には、酸化物半導体をチャネル形成領域に含むトランジスタを用いる。そして、上記記憶素子を、信号処理回路が有する、レジスタやキャッシュメモリなどの記憶装置に用いる。

(もっと読む)

内側にへこんだ形状を含んだトランジスタを製造する方法

トランジスタを製造する方法は、導電材料層と電気絶縁材料層とを順に含んだ基板を準備する工程と、前記電気絶縁材料層上にレジスト材料層を堆積する工程と、前記レジスト材料層をパターニングして、前記電気絶縁材料層の一部を露出させる工程と、露出された前記電気絶縁材料層を除去して、前記導電材料層の一部を露出させる工程と、露出された前記導電材料層を除去し、前記導電材料層及び前記電気絶縁材料層内に凹部形状を作り出す工程と、前記基板と露出された前記電気絶縁材料層及び前記導電材料層とを第2の電気絶縁材料層で共形に被覆する工程と、前記第2の電気絶縁材料層を半導体材料層で共形に被覆する工程と、前記半導体材料層上に導電材料層を指向性堆積する工程とを含む。

(もっと読む)

(もっと読む)

テトラチアフルバレン誘導体を用いた有機トランジスタ及びその製造方法

【課題】種々の溶媒に対して溶解性が優れ、インクジェット等の印刷法により製膜可能なTTF誘導体を用いたインクおよびそれを用いた製造方法、用途を提供する。

【解決手段】一般式(I)で表わされるテトラチアフルバレン誘導体を含む電子デバイス用インク。

(式中、Xは炭素原子または硫黄原子または窒素原子から選択される原子であり、同一でも異なっていてもよい。Xに炭素原子及び窒素原子が選択される場合において、R1〜R8は水素原子、ハロゲン原子、置換および無置換のアルキル基またはアルコシキ基またはチオアルコキシ基から選択される基であり、同一でも異なっていてもよい。)

(もっと読む)

41 - 60 / 320

[ Back to top ]