Fターム[5F110CC09]の内容

Fターム[5F110CC09]に分類される特許

101 - 120 / 320

MOSトランジスタ及びMOSトランジスタを備えた半導体装置の製造方法

【課題】縦型トランジスタにおいて、柱状半導体層上部のシリサイドの細線効果を低減すること、また、シリサイドと上部拡散層間の界面抵抗を低減することによりトランジスタ特性を改善すること、またコンタクトとゲート間のショートが発生しない構造を実現すること。

【解決手段】柱状半導体層と、前記柱状半導体層の底部に形成される第1のドレイン又はソース領域と、該柱状半導体層の側壁を包囲するように第1の絶縁膜を介して形成されるゲート電極と、前記柱状半導体層上面上部に形成されるエピタキシャル半導体層とを含み、前記第2のソース又はドレイン領域が少なくとも前記エピタキシャル半導体層に形成され、前記第2のソース又はドレイン領域の上面の面積は、前記柱状半導体層の上面の面積よりも大きいことを特徴とするMOSトランジスタ。

(もっと読む)

半導体装置及び製造方法

【課題】 オフリーク電流が低減され、電流の立ち上がり特性も良好な結晶性シリコン薄膜半導体装置を提供する。

【解決手段】 非晶質シリコン層及び結晶性シリコン層を半導体層とする薄膜トランジスタにおいて、ドレイン電極が、半導体層の結晶性シリコン層と直接接することにより、電流の立ち上がり特性を向上させることを特徴とする薄膜トランジスタ。

(もっと読む)

半導体装置

【課題】柱状半導体層の周囲にゲート電極が形成される縦型トランジスタにおいては、各々の縦型トランジスタのゲート長より大きいゲート長を持つトランジスタを形成することが困難である。

【解決手段】基板上に形成された第1の拡散層上に2個の柱状半導体層によって形成された縦型トランジスタが隣接して形成されており、それらの縦型トランジスタは共通なゲート電極を備え、第1の柱状半導体層の上部に形成された第1の上部拡散層はソース電極に接続され、第2の柱状半導体層の上部に形成された第2の上部拡散層はドレイン電極に接続され、2個の縦型トランジスタが直列に接続されることによって、各々の縦型トランジスタの2倍のゲート長を持つトランジスタとして機能することを特徴とする半導体装置を提供する。

(もっと読む)

有機トランジスタの製造方法及び有機トランジスタ

【課題】移動度の高い有機トランジスタを効率良く製造することができる製造方法及び有機トランジスタを得る。

【解決手段】ゲート電極2と、ゲート電極2上に設けられるゲート絶縁膜3,4と、ゲート絶縁膜3,4上に設けられる有機半導体層9と、ゲート絶縁膜3,4上の有機半導体層9にチャネル領域を形成するため設けられるソース電極7及びドレイン電極8とを備える有機トランジスタを製造する方法であって、ゲート電極2を形成する工程と、ゲート電極2の上にゲート絶縁膜3,4を形成する工程と、ソース電極7及びドレイン電極8を形成する工程と、ゲート絶縁膜3,4に、カップリング剤の溶液を接触させた状態で、ゲート電極2に電圧を印加してゲート絶縁膜3,4の上にカップリング剤層5を形成する工程と、カップリング剤層5が形成されたゲート絶縁膜3,4の上に有機半導体層9を形成する工程とを備えることを特徴としている。

(もっと読む)

半導体装置およびその製造方法

【課題】ウェル電位固定用のウェル給電用素子を設ける際に、縦型MOSトランジスタ間に素子分離用の埋込絶縁層を必要とせず、素子分離用の埋込絶縁層の形成に必要な面積を削減して、半導体装置の高集積化を図る。

【解決手段】半導体基板1に形成された第1導電型のウェル2内に、ウェル給電用素子Xと縦型MOSトランジスタYとが備えられ、ウェル給電用素子Xは、ウェル2と同じ導電型のボディ領域からなるピラー部P1を有し、ピラー部P1の上部には、第1導電型のウェル2の濃度よりも高い濃度を有する第1導電型の第1不純物拡散層13を備え、縦型MOSトランジスタYは、ウェル2と同じ導電型のボディ領域からなるピラー部P2を有し、かつ縦型MOSトランジスタYのピラー部P2の上部には、第2導電型の第2不純物拡散層7を備えることを特徴とする半導体装置を採用する。

(もっと読む)

半導体装置及びその製造方法

【課題】1個の島状半導体を用いてインバータを構成することにより、高集積なSGTを用いたCMOSインバータ回路からなる半導体装置を提供する。

【解決手段】島状半導体層の周囲を取り囲む第1のゲート絶縁膜と、第1のゲート絶縁膜の周囲を取り囲むゲート電極と、ゲート電極の周囲を取り囲む第2のゲート絶縁膜と、第2のゲート絶縁膜の周囲を取り囲む筒状半導体層と、島状半導体層の上部に配置された第1の第1導電型高濃度半導体層と、島状半導体層の下部に配置された第2の第1導電型高濃度半導体層と、筒状半導体層の上部に配置された第1の第2導電型高濃度半導体層と、筒状半導体層の下部に配置された第2の第2導電型高濃度半導体層と、を有することを特徴とする半導体装置により、上記課題を解決する。

(もっと読む)

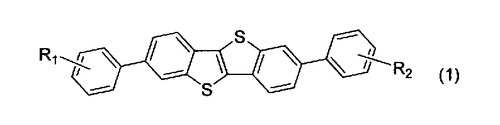

縦型有機半導体デバイス

【課題】雰囲気安定性、高ON/OFF比、高電流密度等の優れた特性を有する実用的な縦型有機半導体デバイスを提供する。

【解決手段】一般式(1)で表される化合物を半導体材料として含む、縦型有機半導体デバイス。

(R1及びR2はそれぞれ独立に置換基を有してもよい芳香族基を表す)

(もっと読む)

有機トランジスタ

【課題】無機半導体デバイスに比べて簡便なプロセスで素子を作製することが可能であり、かつ長時間安定したトランジスタ特性を示す有機トランジスタを提供する。

【解決手段】有機半導体層が、下式で表される化合物の重合体を含有する有機トランジスタ。

(R1〜R18は、それぞれ独立に、水素原子もしくは1価の有機残基を表し、R1〜R5のうち少なくとも一つは水素原子であり、かつR6〜R10のうち少なくとも一つは水素原子である。)

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体を用いた新たな半導体装置を提供することを課題とする。

【解決手段】基板(例えば絶縁表面を有する基板)と、基板上の第1の電極層と、その一部が第1の電極層上に存在する酸化物半導体層と、酸化物半導体層の側面を覆うゲート絶縁層と、ゲート絶縁層の開口部において、酸化物半導体層と電気的に接続した第2の電極層と、ゲート絶縁層を介して酸化物半導体層の側面に電圧を印加する第3の電極層と、を有する。

(もっと読む)

金属表面の処理方法及び電界効果トランジスタの製造方法

【課題】弁金属を含む金属の陽極酸化処理と、形成した膜の表面を疎水性にする処理とを同時に行う方法とその方法を用いた電界効果トランジスタの製造方法の提供。

【解決手段】電解液中に、ホスホン酸基と有機基を有するカップリング剤が含まれていることを特徴としており、好ましくは、カップリング剤が;R(OH)2POで表される。(式中、Rは、炭素数1〜20の炭化水素基、炭素数1〜20のアルキル基、アリール基、フェニル基、エーテル基、チオフェン誘導体、ピロール誘導体、アニリン誘導体、ビニル基を有する誘導体、エポキシ基を有する誘導体、スチリル基を有する誘導体、メタクリロキシ基を有する誘導体、アクリロキシ基を有する誘導体、アミノ基を有する誘導体、ウレイド基を有する誘導体、クロロプロピル基を有する誘導体、メルカプト基を有する誘導体、スルフィド基を有する誘導体、イソシアネート基を有する誘導体)

(もっと読む)

半導体装置及びその製造方法

【課題】基板容量及び基板抵抗を低減することにより、高速及び高周波で動作する半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の製造方法が、第1導電型の半導体基板に第2導電型の第1の不純物層を形成することにより、半導体基板にPN接合を形成する工程(a)と、第1の不純物層の上面の半導体基板表面に、半導体素子と、第1の不純物層と電気的に接続される導電層とを形成する工程(b)と、導電層を、エッチング用電源の正電極と接続し、対向電極をエッチング用電源の負電極と接続し、半導体基板と対向電極とをエッチング液に浸し、半導体基板の内部に形成されたPN接合に逆バイアスを印加することにより、第1の不純物層をエッチング停止層として、第1導電型の半導体基板を除去する工程(c)と、第1の不純物層の下面に、恒久支持基板を取り付ける工程(d)と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜の侵食を抑制し、FETの故障や不良の発生を抑制することが可能な半導体装置の製造方法を提供すること。

【解決手段】基板10上にGaN系半導体層15を形成する工程と、GaN系半導体層15上に酸化アルミニウムからなるゲート絶縁膜18を450℃以下の成膜温度で形成する工程と、ゲート絶縁膜18の上面に保護膜19を形成する工程、ゲート絶縁膜18を熱処理する工程、及びゲート絶縁膜18をプラズマ処理する工程のいずれか一つと、前記いずれか一つの工程の後に、ゲート絶縁膜18を形成する工程の後のアルカリ溶液を用いた処理を実行する工程と、前記ゲート絶縁膜18上にゲート電極を形成する工程と、を有することを特徴とする半導体装置の製造方法。

(もっと読む)

ホウ素ドープ半導体ナノワイヤ及びその製造方法

【課題】成長軸方向に径の均一なホウ素ドープ半導体ナノワイヤ及びその製造方法を提供する。

【解決手段】成長軸方向に径の均一なホウ素ドープ半導体ナノワイヤは、次の工程を含む製造方法により製造できる。

工程(1):半導体原料ガスを用いて、基板上にIV族半導体ナノワイヤを成長させる;

工程(2):ジボランガスのみを導入することにより、前記半導体ナノワイヤの表面にホウ素膜を堆積させる;

工程(3):表面にホウ素膜を堆積させた前記ホウ素膜付き半導体ナノワイヤを、半導体ナノワイヤ(本体)の融点以下の温度で熱アニールする。

(もっと読む)

センサデバイス

【課題】高速で動作可能な縦型トランジスタを用いたセンサデバイスを提供する。

【解決手段】絶縁物の多孔質により形成される多孔質絶縁層と、多孔質絶縁層の一方の面に形成される第1の開口部を有する第1の電極と、多孔質絶縁層の他方の面に形成される第1の開口部に対応した第2の開口部を有する第2の電極と、第2の電極上に形成される絶縁層と、多孔質絶縁層の孔の内壁に配置された分子認識材料とを有することを特徴とするセンサデバイスを提供することにより上記課題を解決する。

(もっと読む)

ESD保護素子

【課題】SOI層のばらつきによる耐圧の依存性が低く、素子面積を小さくすることが可能なESD保護素子を提供すること。

【解決手段】BOX酸化膜、N+埋込層、及びP型SOI層が順に積層された略直方体形状のSOI基板と、前記SOI基板におけるP型SOI層側の第1の矩形面において、対向する二辺に沿ってそれぞれ形成されたドレイン及びソースと、前記SOI基板における、前記第1の面の前記ドレイン及びソースが沿って形成された二辺に直交する二面に形成された絶縁ゲートと、保護対象装置の入力端子における電圧を検出する電圧検出手段と、を備え、前記電圧検出手段により閾値電圧を超える電圧が検出されたときに、前記絶縁ゲートが駆動されることを特徴とする、ESD保護素子。

(もっと読む)

横型MOSトランジスタ

【課題】

オン抵抗の低減を図った横型MOSトランジスタを提供する。

【解決手段】

第1導電型の半導体層と、半導体層の第1領域に深さ方向に形成される第1酸化膜と、半導体層の第1領域とは離間した第2領域に深さ方向に形成される第2酸化膜と、半導体層内で第1酸化膜に隣接する領域に深さ方向に形成されるゲート電極と、半導体層内で第2酸化膜に隣接する領域に形成される制御電極と、半導体層の第1酸化膜と第2酸化膜で挟まれる領域の表面部のうちの第1酸化膜の近傍の領域に形成される第2導電型領域と、第2導電型領域の表面部のうちの第1酸化膜の近傍の領域に形成される第1導電型領域と、第1導電型領域及び第2導電型領域の上に形成されるソース電極と、半導体層の第1酸化膜と第2酸化膜で挟まれる領域の表面部のうちの第2酸化膜の近傍の領域に形成される第1導電型領域と、第1導電型領域の上に形成されるドレイン電極とを含む。

(もっと読む)

半導体装置とその製造方法

【課題】柱状半導体層が微細化されて高集積化されても、コンタクト抵抗の増加を抑制する構造の半導体装置を提供する。

【解決手段】半導体装置は、基板(半導体基板1)と、半導体基板1上に設けられた、半導体柱状部(柱状半導体層3)と、の天面に接するように設けられた、柱状半導体層3と同径以下のコンタクト柱状部(コンタクト層7)と、この天面に設けられた凹部をと備えるものである。

(もっと読む)

半導体装置の製造方法

【課題】微細化された3次元的なデバイスを実現し得る、半導体装置の製造方法を提供する。

【解決手段】開示される、本発明の一実施形態による、半導体装置の製造方法によれば、ライン・アンド・スペース状の第2の層12を、第2の層12が延在する方向と交わる方向に延びるライン・アンド・スペース状の第8の層25をマスクとしてエッチングすることにより、二次元的に配列される第2の層12を得、これにより下地層をエッチングすることにより、二次元的に配列されるピラーを形成することができる。

(もっと読む)

半導体装置

【課題】 小型であり、順方向と逆方向の双方で導通可能(スイッチング可能)な半導体装置を提供する。

【解決手段】 第1導電型の第1領域30と、第2導電型であり、第1領域30に接している第2領域32と、第1導電型であり、第2領域32によって第1領域から分離されている第3領域36と、第2導電型であり、第3領域36によって第2領域32から分離されている第4領域22と、第1導電型であり、第4領域22によって第3領域36から分離されている第5領域20と、第1領域30及び第2領域34と導通している第1電極56と、第4領域22及び第5領域20と導通している第2電極54と、第2領域32に対して絶縁膜42を介して対向している第1ゲート電極44と、第4領域22に対して絶縁膜50を介して対向している第2ゲート電極52を備えていることを特徴とする半導体装置。

(もっと読む)

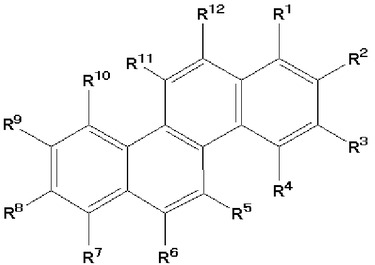

クリセン骨格を有する有機化合物を用いた半導体材料

【課題】ペンタセンの不安定性を克服しつつ、単結晶の貼り付け法、真空蒸着法、塗布法と多様な製造プロセスに適応でき、有機トランジスタとしても高い性能を示す新規な有機半導体材料を提供する。

【解決手段】下記化学式で表されるクリセン骨格を有する有機半導体材料。 (もっと読む)

(もっと読む)

101 - 120 / 320

[ Back to top ]