Fターム[5F110EE24]の内容

Fターム[5F110EE24]に分類される特許

161 - 180 / 404

半導体集積回路装置、及びその製造方法

【課題】高圧金属電極と低圧電極との間の絶縁耐圧を上昇させることができる。

【解決手段】支持基板5、この支持基板に積層された絶縁膜6、及び絶縁膜に積層された第一半導体層8を備えた高耐圧半導体210と、制御回路とを備える半導体集積回路装置において、高耐圧半導体210は、第一半導体層を取り囲むように、閉ループ状の絶縁膜が形成された内側誘電体分離領域701と、内側誘電体分離領域の外周に、閉ループ状の絶縁膜が形成された外側誘電体分離領域702と、絶縁膜の表面であって、内側誘電体分離領域と外側誘電体分離領域との間に形成された第二半導体層81と、内側誘電体分離領域、外側誘電体分離領域、及び第二半導体層の表面に積層されたフィールド酸化膜50と、第一半導体層に接続され、フィールド酸化膜の表面に形成された金属電極3とを備えている。

(もっと読む)

半導体記憶装置

【課題】フローティングボディ型のNMOSトランジスタを用い、そのボディに安定な電位を供給して正孔の蓄積に起因する特性劣化を防止可能な半導体記憶装置を提供する。

【解決手段】本発明の半導体記憶装置において、メモリセルMCに含まれるNMOSトランジスタQ0は、ゲート電極がワード線WLに接続され、一方のソース・ドレイン領域がビット線BLに接続されている。センスアンプ回路10に含まれるNMOSトランジスタQ10は、ゲート電極がビット線BLに接続され、一方のソース・ドレイン領域が所定の電位(グランド電位)に接続されている。NMOSトランジスタQ0、Q10は、フローティングボディ型のNMOSトランジスタであって、少なくともプリチャージ動作時に、ビット線BLに所定の電位(グランド電位)が供給されるので、ボディへの電位が安定化し、正孔の蓄積に起因する特性劣化を抑えることができる。

(もっと読む)

MIS積層構造体の作製方法およびMIS積層構造体

【課題】コスト低減の図れるスイッチング素子の基本構造であるMIS積層構造体およびそれらの作製方法を提供する。

【解決手段】支持基板上に、少なくとも半導体材料層〔S〕、絶縁材料層〔I〕、および導電性酸化物材料層〔M〕(照射するレーザ光を吸収し、薄膜の少なくとも一部がアモルファス相である導電性酸化物材料層)を順次成膜してMIS積層構成体を形成する成膜工程(a)と、集光した状態のレーザ光を前記導電性酸化物材料層側から照射して該導電性酸化物材料層の一部を熱変化させると共に、MIS積層構成体内部に伝播した熱により前記半導体材料層の一部を熱変化させる熱処理工程(b)と、前記MIS積層構成体の熱変化していない部分をエッチング処理で除去するエッチング処理工程(c)とによりMIS積層構造体を作製し、これに電極を設けてスイッチング素子とする。

(もっと読む)

ゲイン変化補償を伴うトランジスタ

半導体装置(10)およびこれを製造方法は、活性素子領域(12)および隔離領域(14)を提供する工程を含み、隔離領域は、活性素子領域との境界(32)を形成する。パターン化ゲート材料(16)は、境界の第1部分(34)と第2(36)部分との間において、活性素子領域と重なる。パターン化ゲート材料は、活性素子領域内において、チャネルを画定し、ゲート材料は、境界領域の第1部分および第2部分の付近において、境界の第1部分と第2部分との間よりも大きい(24+26,28+30)、ゲート材料の主要寸法に沿って中心線(18)と直交するゲート長さ寸法を有する。チャネルは、境界の第1部分に隣接する第1端と、境界の第2部分に隣接する第2端とを含み、更に、チャネルの両端においてテーパが付けられたゲート長さ寸法によって特徴付けられる。  (もっと読む)

(もっと読む)

露光装置およびそれを用いたデバイスの製造方法

【課題】ゲート電極とソース/ドレイン電極の相対的な位置を自己整合的に精度よく合わせることができ、生産性の高い有機薄膜トランジスタの製造用露光装置を提供すること。

【解決手段】ロールtoロールで光透過性を有するフレキシブル基板を搬送し、このフレキシブル基板上に有機トランジスタを形成する際に、フレキシブル基盤上にゲート電極、絶縁層、感光性自己組織化膜を形成し、ゲート電極をマスクとして自己整合的に感光性自己組織化膜に露光、感光するための露光装置において、露光用の光源から見てフレキシブル基板と反対側に形成される側の装置内壁面に反射防止膜を設ける。

(もっと読む)

薄膜トランジスタ及びその作製方法、並びに表示装置及びその作製方法

【課題】従来よりも少ないマスク数で作製する薄膜トランジスタ及び表示装置の作製方法を提供する。

【解決手段】第1の導電膜と、絶縁膜と、半導体膜と、不純物半導体膜と、第2の導電膜とを積層し、この上に3段階の厚さを有するレジストマスクを形成し、第1のエッチングを行って薄膜積層体を形成し、該薄膜積層体に対してサイドエッチングを伴う第2のエッチングを行ってゲート電極層を形成し、その後レジストマスクを後退させて半導体層、ソース電極及びドレイン電極層を形成することで、薄膜トランジスタを作製する。3段階の厚さを有するレジストマスクは、例えば、4階調のフォトマスクにより形成する。

(もっと読む)

アクティブマトリクスOLEDディスプレイおよびその駆動回路

ディスプレイが、それぞれが関連画素駆動回路をもつ複数の有機発光ダイオード(OLED)画素と、複数の選択線と、複数のデータ線とを有する。画素駆動回路のそれぞれは、選択線およびデータ線に結合される。画素駆動回路は、OLEDを駆動するように構成された駆動トランジスタを含むとともに、選択線に結合された第1の端子と、データ線に結合された第2の端子とを有する選択トランジスタを含み、選択トランジスタの端子の一方は、選択トランジスタのゲート接続を備え、端子の他方は、選択トランジスタのドレイン接続およびソース接続の一方を備え、選択トランジスタは、ソース領域と、ドレイン領域と、ゲート領域とを備え、ゲート領域は、ソース領域およびドレイン領域に少なくとも部分的に重なり、ゲート接続と、ドレイン接続およびソース接続の一方との間の静電容量が、ゲート接続と、接続の他方との間の静電容量よりも小さくなるように、ゲート領域の、ソース領域およびドレイン領域の一方との重なりの面積が、領域の他方との重なりの面積よりも大きくなっている。  (もっと読む)

(もっと読む)

電子装置およびその製造方法

【課題】半導体薄膜に対し十分な加熱が行われ、かつ、熱源走査の往路または復路の何れかでアニールを行っても特性がばらつかないようにする。

【解決手段】薄膜トランジスタが、予備加熱層としてのゲート電極11と、ゲート電極11に対し平面形状で一部が重なる薄膜半導体層13dとを有する。予備加熱層としてのゲート電極11は、薄膜半導体層13dと重なる第1領域R1以外の部分(第2領域R2が、一方向(X軸方向)と直交する方向(Y軸方向)の軸を境に線対称な平面形状を有する。このような平面形状では、X軸方向に走査される熱源の往路と復路で、トランジスタチャネルが形成される第1領域R1に対する予備加熱の仕方がほぼ同じとなり、トランジスタ特性の均一性が高くなる。

(もっと読む)

静電気放電保護素子

【課題】 SOI基板上に形成され、ESD耐性の高い半導体装置を提供する。

【解決手段】 SOI基板上に形成されたMOSトランジスタ2と、MOSトランジスタのソース電極及びドレイン電極間に少なくとも一つのダイオード3、及び抵抗4が直列接続されており、ダイオードと抵抗の接続点にMOSトランジスタ2のゲート電極5を接続することによってESD耐性を高める。さらに、ダイオードと抵抗の接続点と、ボディコンタクト領域6とを接続することによって、より高いESD耐性を得ることができる。

(もっと読む)

金属型及び半導体型単層カーボンナノチューブからなる半導体装置

【課題】ソース・ドレイン等の電極に金属型単層カーボンナノチューブ(SWCNT)、チャネルに半導体型SWCNTを利用することで、チャネル・ソース・ドレイン間のコンタクトが良好な半導体装置を提供する。

【解決手段】SWCNT原料から、金属型・半導体型SWCNTの分離精製を行い、それぞれ純度90%以上のものを用意し、インクジェット法により、ソース・ドレインを金属型SWCNTで形成し、チャネルを半導体型SWCNTで形成することにより、良好なコンタクトを保ちながら、トランジスタ動作が可能となる。

(もっと読む)

有機トランジスタアレイ及び表示装置

【課題】 プロセスステップを増加させず、かつ現状の印刷プロセスで製造可能な集積度の高い有機トランジスタアレイ、及び、前記有機トランジスタアレイを有する表示装置を提供することを目的とする。

【解決手段】 基板上に設けられた複数のゲート電極と、前記複数のゲート電極の上層又は下層にゲート絶縁膜を介して設けられた複数のソース電極及び複数のドレイン電極と、前記ゲート絶縁膜を介して前記ゲート電極に対向して配置され、前記ソース電極と前記ドレイン電極との間にチャネル領域を形成する有機半導体層と、を有する有機トランジスタアレイであって、前記有機トランジスタアレイは、平面視において、単一画素を構成する複数の区画に区分され、前記区画は、最密充填構造を有することを特徴とする。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタアレイ並びに画像表示装置

【課題】薄膜トランジスタの寄生容量を低減した薄膜トランジスタアレイ及び薄膜トランジスタアレイを備えた画像表示装置を提供する。

【解決手段】半導体層とゲート電極とソース電極とドレイン電極とを備え、前記ゲート電極、前記ソース電極または前記ドレイン電極のいずれか一つが開口部を有する形状であること。開口部は円、三角、四角のいずれかの形状であり、半導体層が有機半導体または酸化物半導体であることを特徴とする薄膜トランジスタ。

(もっと読む)

寄生容量が低減されたSOIボディ・コンタクト型FETのための方法及び構造体

【課題】 ボディ・コンタクトを半導体オン・インシュレータ・デバイスに設け、それにより、デバイスに寄生容量の低減をもたらすこと。

【解決手段】 1つの実施形態において、本発明は、絶縁層の上を覆うように配置された半導体層を含む基板であって、半導体層は、半導体ボディと、半導体ボディの外周の周りに存在する分離領域とを含む基板と、基板の半導体層の上を覆うゲート構造体であって、半導体ボディの上面の第1の部分上に存在するゲート構造体と、非シリサイド半導体領域によって半導体ボディの第1の部分から分離される半導体ボディの第2の部分と直接物理的に接触しているシリサイド・ボディ・コンタクトとを含む、半導体デバイスを提供する。

(もっと読む)

メモリ素子、半導体記憶装置及びその動作方法

【課題】メモリウィンドウを拡大することで信頼性が向上したメモリ素子を提供することを課題とする。

【解決手段】支持基板上に設けられた半導体層と、半導体層内に設けられたチャネル領域と、チャネル領域の両側に設けられ、半導体層内に位置する第1の導電型の2つの拡散層領域と、チャネル領域の上に設けられた電荷蓄積機能を有する第1のゲート絶縁膜と、第1のゲート絶縁膜の上に設けられた第1のゲート電極とを備え、更に、チャネル領域のチャネル幅方向の端部に隣接し、チャネル領域外の半導体層の上に設けられた第2のゲート絶縁膜と、第2のゲート絶縁膜の上に設けられ、第1のゲート電極と電気的に絶縁された第2のゲート電極とを備えていることを特徴とするメモリ素子により上記課題を解決する。

(もっと読む)

半導体装置及びその製造方法

【課題】MOSFETダイオードのチャネル幅を効率良く広げることができ、レイアウトの利用効率を向上できるようにした半導体装置及びその製造方法を提供する。

【解決手段】Si基板1上に絶縁層3を介して形成されたSi層5と、Si層5上に形成されたゲート絶縁膜13と、ゲート絶縁膜13上に形成され、平面視で複数の環状体151,152a〜152dが接触した形状である第1の部位15aを有するゲート電極15と、第1の部位15aをなす各環状体151,152a〜152dの内側と外側のSi層5にそれぞれ形成されたS/D層17,18と、S/D層18とゲート電極15とを接続する配線31と、を備える。このような構成であれば、アクティブ領域のSi層5に、多数の環状のチャネル領域を形成することができ、MOSFETダイオードのチャネル幅を効率良く広げることができる。

(もっと読む)

MuGFETのESD保護デバイスの設計手法

【課題】所定の設計目標に対して最適化することができるMuGFETのESD保護デバイスの製造方法を提供すること。

【解決手段】複数の相互に依存したレイアウトとプロセスパラメータを選択する工程を含み、MuGFETのESD保護デバイスのフィン幅、ゲート長、フィン数を含み、更に、フィン幅、ゲート長、フィン数に依存する少なくとも1つの他のパラメータのサブセットを含む。この方法は、(a)予め決められたESDの制限に合致するように、採りうる値の複数の組み合わせを選択する工程と、(b)予め決められた関係に基づいて、サブセットのために複数の値を決定する工程と、(c)予め決められた設計ターゲットの観点からサブセットの最適値を決定する工程と、(d)最適値に基づいて、フィン幅、ゲート長、およびフィン数の値を決定する工程と、(e)所定の製造プロセスと、工程(d)で決められた値を用いて、製造する工程と、を含む。

(もっと読む)

半導体装置およびその製造方法

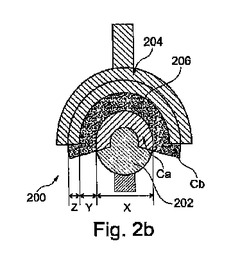

【課題】横型のMISFETを形成して成る半導体装置およびその製造方法において、簡単な構成により、生産性の向上、およびオン抵抗とドレインソース間の接合静電容量の積の低減を図る。

【解決手段】半導体装置1は、SOI基板2の主表面に横型のMISFETを形成して成り、基板2の主表面には、MISFETのソース領域3とドレイン領域4間の電流経路を拡大させるための凹凸構造6が設けられており、凹凸構造6の凹部11と凸部12の境界が斜めに傾斜している面によって構成されている。凹凸構造6表面の角度変化が緩やかで膜切れが発生しにくく、ゲート絶縁膜51やゲート電極5を生産性良く容易に形成できる。凹凸構造6により、オン抵抗(Rとする)が低減され、平面状態より凹んでいる凹部11におけるドレインソース間容量(Cとする)が最適化されCR積を低減できる。

(もっと読む)

半導体装置

半導体装置は、基板(11)上に形成されたフィン型半導体領域(13)と、前記フィン型半導体領域(13)の所定部分の上面及び両側面を覆うように形成されたゲート絶縁膜(14)と、前記ゲート絶縁膜(14)上に形成されたゲート電極(15)と、前記フィン型半導体領域(13)における前記ゲート電極(15)の両側に形成された不純物領域(17)とを備えている。前記フィン型半導体領域(13)の上面上における前記ゲート電極(15)の両側に隣接して不純物阻止部(15a)が設けられている。 (もっと読む)

半導体装置

【課題】印加電圧に対して従来よりも高い耐性を有し、小型化に優れ、被保護素子を保護する半導体装置を提供する。

【解決手段】半導体装置は、被保護素子に接続され、ソース層とドレイン層との間を放電経路として被保護素子を保護する半導体装置であって、絶縁膜20上に設けられた半導体層30と、半導体層内に形成され、第1の方向に延伸するソース層Sと、半導体層内に形成され、ソース層に沿って延伸するドレイン層Dと、ソース層とドレイン層との間の半導体層において第1の方向に延伸するように設けられた複数のボディ領域Bと、複数のボディ領域を接続するボディ接続部BCPとを備え、ボディ接続部から比較的離れた位置におけるソース層とドレイン層との間の第1の間隔は、ボディ接続部の比較的近傍におけるソース層とドレイン層との間の第2の間隔よりも大きい。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】 簡便に形成可能であり、リーク電流の発生を抑制できる薄膜トランジスタ及び薄膜トランジスタの製造方法を提供する。

【解決手段】 薄膜トランジスタ22は、ソース領域及びドレイン領域の一方である第1領域と、他方である第2領域と、を有した半導体層25と、ゲート絶縁層27と、ゲート絶縁層上に形成され、第1領域から外れて位置し、第2領域に重ねられた開口部30aを有した環状のゲート電極30と、層間絶縁膜31と、半導体層の第1領域に接続された第1電極と、半導体層の第2領域に接続された第2電極と、を備えている。

(もっと読む)

161 - 180 / 404

[ Back to top ]