Fターム[5F110EE24]の内容

Fターム[5F110EE24]に分類される特許

101 - 120 / 404

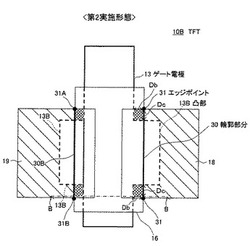

半導体デバイスおよび表示装置

【課題】オン抵抗を犠牲にしないで寄生容量とリーク電流のトレードオフを解消または緩和する。

【解決手段】TFT部10Bは、2つのソース・ドレイン電極18,19が、半導体膜15の平面視でチャネル形成領域を挟んで位置する一方と他方の半導体領域に接する。ソース・ドレイン電極18,19は、半導体膜15と接する領域(斜線部)の当該ソース・ドレイン電極の輪郭部分30において、その両端のエッジポイント31の各々が、平面視でゲート電極13の外側に位置している。

(もっと読む)

半導体装置及びその製造方法

【課題】 ゲートとドレインの間で生じる電界集中を緩和する半導体装置を提供する。

【解決手段】本発明によれば,半導体基板上にゲート絶縁膜を介して形成された第1のゲート電極と、前記半導体基板上に前記ゲート絶縁膜を介して形成され、かつ、第1のゲート電極の側面に絶縁性のスペーサを介して配置された第2のゲート電極と、第1及び第2のゲート電極を挟むように前記半導体基板上に形成されたソース領域及びドレイン領域と、第1のゲート電極下方における前記半導体基板の一部の領域を挟むように形成され、第2のゲート電極及び前記ソース領域及びドレイン領域と重なるように形成された電界緩和領域と、を備える半導体装置が提供される。

(もっと読む)

半導体装置およびプラズマディスプレイデバイス

【課題】寄生抵抗が小さく、かつ電流駆動能力が大きい高耐圧ハイブリッドトランジスタのような半導体装置の構造を提供する。

【解決手段】第1導電型の半導体層22に第1導電型のベース領域9を備える。ベース領域9には第2導電型のエミッタ領域10が設けられる。半導体層22にはベース領域9に隣接して半導体層22の表面から半導体層22の厚さより小さい所定深さにわたって第2導電型の不純物層23が設けられる。不純物層23にはベース領域9から離間して第1導電型のコレクタ領域11および第2導電型のドレイン領域14が設けられる。半導体層22の表面上には、エミッタ領域10の端部上、ベース領域9上および不純物層23上の一部にわたってゲート絶縁膜12を介してゲート電極13が設けられる。エミッタ領域10とベース領域9とに共通接続された第1電極15と、コレクタ領域11とドレイン領域14とに共通接続された第2電極16とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】駆動電流の増大を図る。

【解決手段】半導体装置は、半導体基板10と、前記半導体基板上のソース/ドレイン領域に形成された第1半導体層11と、前記第1半導体層上に形成された第1部分12aと、前記ソース/ドレイン領域の間に位置するチャネル領域に線状に形成された第2部分12bと、を有する第2半導体層12と、前記第2半導体層の前記第2部分の周囲に絶縁膜17を介して形成されたゲート電極18と、を具備し、前記第2半導体層の前記第2部分の膜厚は、前記第2半導体層の前記第1部分の膜厚より小さい。

(もっと読む)

薄膜トランジスタ及びその製造方法並びに表示基板

【課題】本発明の一つの目的は、金属イオンの拡散によって半導体パターンの長さが短くなることを防止する薄膜トランジスタ及びその製造方法並びに表示基板を提供する。

【解決手段】薄膜トランジスタは、ソース領域、ドレーン領域、チャンネル領域及び拡散抑制部を含む半導体パターンと、半導体パターン上に形成された第1絶縁膜パターンと、半導体パターンに対応して第1絶縁膜パターン上に形成されたゲート電極と、ゲート電極上に形成された第2絶縁膜パターンと、第2絶縁膜パターン上に形成され、半導体パターンのソース領域及びドレーン領域がそれぞれ接続されるソース電極及びドレーン電極とが設けられ、拡散抑制部はソース電極又はドレーン電極からチャンネル領域へ金属イオンが拡散することを抑制する。

(もっと読む)

半導体装置

【課題】絶縁層上の半導体層に形成されたトランジスターの閾値電圧のバラツキを低減できるようにした半導体装置を提供する。

【解決手段】絶縁層上に半導体層が形成された基板と、前記半導体層に形成されたトランジスターと、を備え、前記トランジスターは、前記半導体層上にゲート絶縁膜を介して形成されたゲート電極と、前記ゲート電極の両側下の前記半導体層に形成されたソース又はドレインと、前記ゲート電極直下の前記半導体層において前記トランジスターのゲート幅方向に沿って電流を流すための入力側端子及び出力側端子と、を有する。

(もっと読む)

半導体基板の作製方法および半導体装置

【課題】炭化シリコンを含む半導体基板の新たな作製方法を提供することを目的の一とする。または、炭化シリコンを用いた半導体装置を提供することを目的の一とする。

【解決手段】炭化シリコン基板にイオンを添加することにより、炭化シリコン基板中に脆化領域を形成し、炭化シリコン基板とベース基板とを絶縁層を介して貼り合わせ、炭化シリコン基板を加熱して、脆化領域において炭化シリコン基板を分離することにより、ベース基板上に絶縁層を介して炭化シリコン層を形成し、炭化シリコン層を1000℃〜1300℃の温度で熱処理して、炭化シリコン層の欠陥を低減することにより半導体基板を作製する。または、上述のようにして形成された半導体基板を用いて半導体装置を作製する。

(もっと読む)

半導体装置とその製造方法

【課題】縦型トランジスタにおいて、柱状半導体層上のコンタクトと柱状半導体層の周囲に形成されるゲート電極のショートの抑制。

【解決手段】上方に平面状半導体層及び該平面状半導体層上の柱状半導体層が形成された基板に対して、柱状半導体層の上部に第2のドレイン/ソース領域を形成し、コンタクトストッパー膜を成膜し、コンタクト層間膜を成膜し、第2のドレイン/ソース領域上にコンタクトを形成し、ここでコンタクトの形成は、コンタクトのパターンを形成し、コンタクトのパターンを用いてコンタクト層間膜をコンタクトストッパー膜までエッチングすることにより、コンタクト用のコンタクト孔を形成し、コンタクト用のコンタクト孔の底部に残存するコンタクトストッパー膜をエッチングにより除去することを含み、コンタクト用のコンタクト孔の底面の基板への投影面は、柱状半導体層の上面及び側面に形成されたコンタクトストッパー膜の基板への投影形状の外周内に位置する。

(もっと読む)

半導体装置およびその作製方法

【課題】高い開口率を有し、安定した電気的特性を有する薄膜トランジスタを有する、信頼性のよい表示装置を作製し、提供することを課題の一とする。

【解決手段】チャネル形成領域を含む半導体層を酸化物半導体膜とする薄膜トランジスタを有する半導体装置の作製方法において、酸化物半導体膜の純度を高め、不純物である水分などを低減する加熱処理(脱水化または脱水素化のための加熱処理)を行う。また、ゲート電極層、ソース電極層、及びドレイン電極層を透光性の導電膜を用いて作製し、開口率を向上させる。

(もっと読む)

半導体装置、電気光学装置、電子機器

【課題】ある応力がかかっても回路全体としての動作特性が変化しない薄膜の半導体素子を実現し、これによって、動作マージンが広く大型化が容易なフレキシブルな半導体装置、電気光学装置、電子機器を提供する。

【解決手段】本発明の半導体装置は、基板100上に薄膜トランジスタ8を有し、この薄膜トランジスタ8は、基板100の湾曲に対してチャネル内のキャリアの移動度が相補的に変化する第1のチャネル領域1cおよび第2のチャネル領域1cを有している。

(もっと読む)

トランジスタを有する表示装置の作製方法

【課題】安定した電気的特性を有するトランジスタを用いて安定した動作を行う表示装置を提供することを課題とする。

【解決手段】酸化物半導体層をチャネル形成領域とするトランジスタを適用して表示装置を作製するに際し、少なくとも駆動回路に適用するトランジスタの上に更なるゲート電極を配する。酸化物半導体層をチャネル形成領域とするトランジスタを作製するに際しては、酸化物半導体層に対して脱水化または脱水素化のための加熱処理を行い、上下に接して設けられるゲート絶縁層及び保護絶縁層と酸化物半導体層の界面に存在する水分などの不純物を低減する。

(もっと読む)

半導体装置

【課題】 DCBLストレスによるオフ耐圧性能を向上させた高耐圧LDMOSを提供する。

【解決手段】 半導体基板に形成され、トレンチにより素子分離され、ソース領域がドレイン領域で挟まれたMOSトランジスタであり、ゲート電極に接続されたメタル層ゲート配線がP型ドリフト層上を通過するように前記トレンチ外に引き出されている高耐圧LDMOS。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板上に容易なプロセスにより、微細で、高速なSOI構造の縦型のMISFETを得ること。

【解決手段】半導体基板1上に酸化膜2を介して、下部に配線層3を有する自己整合の横及び縦方向エピタキシャル半導体層からなる凸状構造の半導体層6が設けられ、凸状構造の半導体層6は素子分離領域埋め込み絶縁膜4及び酸化膜2により島状に絶縁分離されている。凸状構造の半導体層6の上部には高濃度及び低濃度ドレイン領域10、9が設けられ、下部には高濃度及び低濃度ソース領域7、8が設けられ、側面にはゲート酸化膜11を介してゲート電極12が設けられ、高濃度ドレイン領域10、下層配線3を介した高濃度ソース領域7及びゲート電極12には、それぞれバリアメタル18を有する導電プラグ19を介してバリアメタル21を有するCu配線22が接続されている自己整合連続縦横エピタキシャル成長法によるMISFET。

(もっと読む)

半導体装置

【課題】SOI基板にFETが形成された半導体装置であって、動作の信頼性が高い半導体装置を提供する。

【解決手段】半導体装置1においては、SOI基板10のシリコン層13内に、N−型のボディ領域22、P+型のドレイン領域23a及びソース領域23b、ボディ領域22から見てソース領域23b側に配置されたN+型のボディコンタクト領域24が形成されている。上方から見て、ボディ領域22の形状はコ字状であり、FET形成領域の短辺方向に延びる本体部22aと、本体部22aから長辺方向に延出した延出部22bとが形成されている。また、短辺方向から見て、ボディコンタクト領域24の形状はL字状であり、延出部24bはボディ領域22の延出部22bの直下域に進入している。これにより、ボディコンタクト領域24は本体部22aに接触し、ゲート絶縁膜14の中央部分14cから離隔している。

(もっと読む)

高耐圧半導体装置

【目的】裏面工程追加などの複雑な製造プロセスを一切伴わず、レベルシフタ素子である高耐圧NMOSFETの高耐圧化が安価で実現できるほか、安定した高電位配線、低いオン電圧による低電圧駆動かつ高速応答性の実現を可能とする高耐圧半導体装置および高電圧集積回路装置を提供することにある。

【構成】支持基板100上に埋め込み酸化膜200を介して半導体層101が形成され、半導体層101上に高電位側第2段トランジスタ302とそれを囲むように低電位側第1段トランジスタ301を形成し、第2段トランジスタのドレイン電極1071と第1段トランジスタ301のソース電極1072を接続する。第2段トランジスタ302のドレイン電極114はドレインパッド119と接続される。

(もっと読む)

半導体装置及びその製造方法

【課題】4個の島状半導体を用いてSRAMを構成することにより、高集積なSGTを用いたSRAMからなる半導体装置を提供する。

【解決手段】第1の島状半導体層137の周囲上に少なくとも一部に接して第1のゲート絶縁膜187が存在し、第1のゲート絶縁膜187に第1のゲート電極178の一面が接し、第1のゲート電極178の他面に第2のゲート絶縁膜187が接し、第2のゲート絶縁膜187に少なくとも第2の半導体層141が接して、第1の島状半導体層137の上部に配置された第1の第1導電型高濃度半導体層161と、第1の島状半導体層137の下部に配置された第2の第1導電型高濃度半導体層162と、第2の半導体層141の上部に配置された第1の第2導電型高濃度半導体層154と、第2の半導体層141の下部に配置された第2の第2導電型高濃度半導体層156と、を有するインバータを用いてSRAMを形成する。

(もっと読む)

半導体素子、論理ゲート、ビットコンパレータ及び確率的連想処理回路

【課題】高速かつ高精度に、確率的な動作を実行する。

【解決手段】2D−TJA14は、ソース領域12とドレイン領域13とを接続する抵抗線網である。2D−TJA14では、複数のドット20が形成されている。ゲート電極G1、G2は、2D−TJA14の複数のドット20各々と容量結合されている。2D−TJA14は、ドット20間を接続する抵抗線網によって微小トンネル接合が形成されている。ドット20のサイズは実質的に均一であり、微小トンネル接合のサイズも実質的に均一である。

(もっと読む)

寄生容量が低減されたSOIボディ・コンタクト型FETのための方法

【課題】

ボディ・コンタクトを半導体オン・インシュレータ・デバイスに設け、それにより、デバイスに寄生容量の低減をもたらすこと。

【解決手段】

1つの実施形態において、本発明は、絶縁層の上を覆うように配置された半導体層を含む基板であって、半導体層は、半導体ボディと、半導体ボディの外周の周りに存在する分離領域とを含む基板と、基板の半導体層の上を覆うゲート構造体であって、半導体ボディの上面の第1の部分上に存在するゲート構造体と、非シリサイド半導体領域によって半導体ボディの第1の部分から分離される半導体ボディの第2の部分と直接物理的に接触しているシリサイド・ボディ・コンタクトとを含む、半導体デバイスの製造方法を提供する。

(もっと読む)

MOSトランジスタ及びMOSトランジスタを備えた半導体装置の製造方法

【課題】縦型トランジスタにおいて、柱状半導体層上部のシリサイドの細線効果を低減すること、また、シリサイドと上部拡散層間の界面抵抗を低減することによりトランジスタ特性を改善すること、またコンタクトとゲート間のショートが発生しない構造を実現すること。

【解決手段】柱状半導体層と、前記柱状半導体層の底部に形成される第1のドレイン又はソース領域と、該柱状半導体層の側壁を包囲するように第1の絶縁膜を介して形成されるゲート電極と、前記柱状半導体層上面上部に形成されるエピタキシャル半導体層とを含み、前記第2のソース又はドレイン領域が少なくとも前記エピタキシャル半導体層に形成され、前記第2のソース又はドレイン領域の上面の面積は、前記柱状半導体層の上面の面積よりも大きいことを特徴とするMOSトランジスタ。

(もっと読む)

半導体装置及びその作製方法

【課題】接続する素子の駆動電圧によってトランジスタのドレイン電圧が決定される。トランジスタの小型化にともないドレイン領域に集中する電界強度が高まり、ホットキャリアが生成し易くなる。ドレイン領域に電界が集中し難いトランジスタを提供することを課題の一とする。また、トランジスタを有する表示装置を提供することを課題の一とする。

【解決手段】高い導電率を有する第1配線層および第2配線層の端部とゲート電極層の重なりをなくすことにより、第1電極層及び第2電極層近傍に電界が集中する現象を緩和してホットキャリアの発生を抑制し、加えて第1配線層および第2配線層より高抵抗の第1電極層および第2電極層をドレイン電極層として用いてトランジスタを構成する。

(もっと読む)

101 - 120 / 404

[ Back to top ]