Fターム[5F110EE24]の内容

Fターム[5F110EE24]に分類される特許

81 - 100 / 404

液晶表示装置、及び当該液晶表示装置を具備する電子機器

【課題】低消費電力化できる液晶表示装置を提供することを課題の一とする。

【解決手段】駆動回路部及び画素部を有する表示パネルと、駆動回路部を駆動する制御信号及び画素部に供給する画像信号を生成するための信号生成回路と、画像信号をフレーム期間毎に記憶する記憶回路と、記憶回路でフレーム期間毎に記憶された画像信号のうち、連続するフレーム期間の画像信号の差分を検出する比較回路と、比較回路で差分を検出した際に連続するフレーム期間の画像信号を選択して出力する選択回路と、比較回路で差分を検出した際に制御信号及び選択回路より出力される画像信号の駆動回路部への供給を行い、比較回路で差分を検出しない際に制御信号を駆動回路部への供給を停止する表示制御回路と、を有する。

(もっと読む)

金属電極および該金属電極を有する有機半導体素子

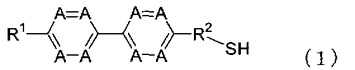

【課題】本発明は、有機高分子等の半導体薄膜形成材料が単結晶でなく、多結晶であっても、印刷方法により金属電極上に安定で良好な有機半導体薄膜を簡便に形成することができ、性能の優れた有機半導体素子を提供することを課題とする。

【解決手段】本発明の金属電極は、下記式(1)で表される化合物を含有する溶液を用いて形成された表面処理層を有することを特徴とする。 (もっと読む)

(もっと読む)

半導体装置及びその作製方法

【課題】量産性の高い新たな半導体材料を用いた大電力向けの半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体膜中の水分または水素などの不純物を低減するために、酸化物半導体膜を形成した後、酸化物半導体膜が露出した状態で第1の加熱処理を行う。次いで、酸化物半導体膜中の水分、または水素などの不純物をさらに低減するために、イオン注入法またはイオンドーピング法などを用いて、酸化物半導体膜に酸素を添加した後、再び、酸化物半導体膜が露出した状態で第2の加熱処理を行う。

(もっと読む)

半導体装置及びその作製方法

【課題】生産性の高い新たな半導体材料を用いた大電力向けの半導体装置を提供することを目的の一とする。または、新たな半導体材料を用いた新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1の結晶性を有する酸化物半導体膜及び第2の結晶性を有する酸化物半導体膜が積層された酸化物半導体積層体を有する縦型トランジスタ及び縦型ダイオードである。当該酸化物半導体積層体は、結晶成長の工程において、酸化物半導体積層体に含まれる電子供与体(ドナー)となる不純物が除去されるため、酸化物半導体積層体は、高純度化され、キャリア密度が低く、真性または実質的に真性な半導体であって、シリコン半導体よりもバンドギャップが大きい。

(もっと読む)

絶縁ゲート型半導体素子及び絶縁ゲート型半導体集積回路

【課題】耐放射線性を有する絶縁ゲート型半導体素子、絶縁ゲート型半導体集積回路を提供する。

【解決手段】一部がチャネル領域をなすp型の半導体層11と、半導体層11の上部に活性領域21Bを定義する素子分離絶縁膜21と、チャネル領域にキャリア注入口を介してキャリアを注入するn型の第1主電極領域12と、チャネル領域から、キャリアを排出するキャリア排出口を有するn型の第2主電極領域13と、活性領域21Bの上に設けられたゲート絶縁膜22と、ゲート絶縁膜22の上に設けられ、第1主電極領域12と第2主電極領域13との間を流れるキャリアの流路に直交する主制御部、主制御部に交わる2本のガード部241,242を有してπ字型をなすゲート電極24と、第2主電極領域13のゲート幅方向の両端側に設けられたp型のリーク阻止領域61,62とを備える。

(もっと読む)

トランジスタ

【課題】生産性の高い新たな半導体材料を用いた大電力向けの半導体装置を提供する。または、新たな半導体材料を用いた新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体中で電子供与体(ドナー)となりうる不純物を除去することで、真性又は実質的に真性な半導体であって、シリコン半導体よりもバンドギャップが大きい酸化物半導体でチャネル形成領域が形成される縦型トランジスタであり、酸化物半導体の厚さが1μm以上、好ましくは3μmより大、より好ましくは10μm以上であり、酸化物半導体に接する電極の一方の端部が、酸化物半導体の端部より内側にある。

(もっと読む)

半導体装置

【課題】無線通信機能を有する半導体装置を低消費電力化又は長寿命化すること。

【解決手段】当該半導体装置は、電力供給源となる電池と、特定の回路とがチャネル形成領域が酸化物半導体によって構成されるトランジスタを介して電気的に接続することによって解決することができる。当該酸化物半導体の水素濃度は、5×1019(atoms/cm3)以下である。そのため、当該トランジスタのリーク電流を低減することができる。その結果、当該半導体装置の待機時の消費電力を低減することができる。また、これにより当該半導体装置を長寿命化することができる。

(もっと読む)

スパッタリングターゲットおよびその製造方法、並びにトランジスタ

【課題】酸化物半導体膜を成膜する成膜技術を提供することを課題の一とする。

【解決手段】金属酸化物の焼結体を含み、その金属酸化物の焼結体の含有水素濃度が、たとえば、1×1016atoms/cm3未満と低いスパッタリングターゲットを用いて酸化物半導体膜を形成することで、H2Oに代表される水素原子を含む化合物、もしくは水素原子等の不純物の含有量が少ない酸化物半導体膜を成膜する。また、この酸化物半導体膜をトランジスタの活性層として適用する。

(もっと読む)

半導体装置

【課題】プロセスの複雑化を招くことなく、サイリスタとしての機能を実現することの出来る半導体装置を提供することを課題の一とする。

【解決手段】リセット動作及び初期化動作により所定の電位が記憶されたメモリ回路を有する半導体装置において、トリガー信号の供給に応じて、メモリ回路の書き換えが行われる回路を設ける構成とする。そして、メモリ回路の書き換えにより、半導体装置に流れる電流を負荷に流す構成とすることで、サイリスタとしての機能を実現しうる半導体装置とする。

(もっと読む)

電界効果トランジスタ

【課題】蛇行した形状に形成されたリセス部を備えることにより、オン抵抗を低減することができる電界効果トランジスタを提供することを目的とする。

【解決手段】電界効果トランジスタ1は、チャネル層11と、チャネル層11とヘテロ接合を構成するキャリア供給層12と、キャリア供給層12の表面から掘り下げて形成されたリセス部13と、リセス部13に沿って形成された第1絶縁層31と、第1絶縁層31の上に形成された第1ゲート電極23と、リセス部13に対してチャネル長方向の一方側に形成されたソース電極21と、リセス部13に対してチャネル長方向の他方側に形成されたドレイン電極22とを備える。リセス部13は、ソース電極21とドレイン電極22とが平面視で平行に対向するチャネル長の範囲内において、蛇行しながらチャネル長方向と交差する方向に延長されている。

(もっと読む)

III族窒化物系半導体素子およびIII族窒化物系半導体素子の製造方法

【課題】低コストで製造することができ、かつ、高い絶縁破壊耐圧を有するIII族窒化

物系半導体素子、およびIII族窒化物系半導体素子の製造方法を提供する。

【解決手段】シリコン層、絶縁層、および表面にシリコンからなる複数の核領域と前記複

数の核領域の間を埋める絶縁領域を有する複合層がこの順に形成された基板と、前記基板

上に形成されたIII族窒化物系半導体からなるバッファ層と、前記バッファ層上に形成

されたIII族窒化物半導体からなる動作層と、前記動作層上に形成された第1の電極お

よび第2の電極とを備え、前記核領域のそれぞれの最大幅L1が、前記第1の電極および

前記第2の電極の間の距離L2よりも小さいことを特徴とする。

(もっと読む)

非線形素子、表示装置、および電子機器

【課題】逆方向飽和電流の低い非線形素子(例えば、ダイオード)を提供する。

【解決手段】例えば、基板上に設けられた第1の電極と、前記第1の電極上に接して設けられ、二次イオン質量分析法で検出される水素濃度が5×1019atoms/cm3以下である酸化物半導体膜と、前記酸化物半導体膜上に接して設けられた第2の電極と、前記第1の電極、前記酸化物半導体膜、及び前記第2の電極を覆うゲート絶縁膜と、前記ゲート絶縁膜に接して設けられ、前記第1の電極、前記酸化物半導体膜、及び前記第2の電極を介して対向する複数の第3の電極と、を有し、前記複数の第3の電極は、前記第1の電極または前記第2の電極と接続されている非線形素子を提供する。

(もっと読む)

半導体装置

【課題】三次元半導体であるsurrounding gate transistor(SGT)のオン電流を増加させることにより、SGTの高速動作を実現する半導体装置を提供することを課題とする。

【解決手段】ソース、ドレイン及びゲートが、基板上に階層的に配置される半導体素子であって、シリコン柱と、前記シリコン柱の側面を取り囲む絶縁体と、前記絶縁体を囲むゲートと、前記シリコン柱の上部又は下部に配置されるソース領域と、前記シリコン柱の上部又は下部に配置されるドレイン領域であって、前記シリコン柱に対して前記ソース領域と反対側に配置されるドレイン領域とを備え、前記シリコン柱と前記ソース領域との接触面は、前記シリコン柱と前記ドレイン領域との接触面より小さい半導体素子を提供することにより上記課題を解決する。

(もっと読む)

フォトマスクおよびこれを用いたトランジスタの製造方法

【課題】各トランジスタの特性を均一化することができるフォトマスクを提供する。

【解決手段】フォトマスク100には、複数のチャネルパターン101と、配線パターン102と、補助パターン103とが形成されている。複数のチャネルパターン101は、半導体基板上に形成された拡散層211の2つの縁部に跨って延ばされ、互いに並列に配された複数のチャネル部を形成するために、並列に配されている。配線パターン102は、チャネル部から延びたゲート配線部を形成するために、チャネルパターン101から延びている。補助パターン103は、各々のチャネル部の、拡散層の縁部212から一定の距離だけ離れた部分を、該チャネル部が延びている方向と直交する方向T2に広げるように、各々のチャネルパターン101に対して設けられている。各々のチャネルパターンに対して設けられた補助パターン103は、互いに同一形状になっている。

(もっと読む)

電子書籍

【課題】安定した電気的特性を有する薄膜トランジスタを有する表示パネルを供えた電子書籍を提供する。また、画像の保持特性の高い電子書籍を提供する。また、高解像度の電子書籍を提供する。また、消費電力の低い電子書籍を提供する。

【解決手段】酸化物半導体中で電子供与体(ドナー)となる不純物を除去することで、真性又は実質的に真性な半導体であって、シリコン半導体よりもエネルギーギャップが大きい酸化物半導体でチャネル形成領域が形成される薄膜トランジスタによって、電子書籍の表示パネルの表示を制御するものである。

(もっと読む)

論理回路及び半導体装置

【課題】トランジスタのリーク電流を低減し、論理回路の誤動作を抑制する。

【解決手段】チャネル形成層としての機能を有する酸化物半導体層を含み、チャネル幅1μmあたりのオフ電流が1×10−13A以下であるトランジスタを有し、入力信号として、第1の信号、第2の信号、及びクロック信号である第3の信号が入力され、入力された第1の信号乃至第3の信号に応じて電圧状態が設定された第4の信号及び第5の信号を出力信号として出力する構成とする。

(もっと読む)

フレキシブル半導体装置およびその製造方法

【課題】高性能なフレキシブル半導体装置を提供すること。

【解決手段】金属箔から成る支持層、支持層の上に形成された半導体構造部、および半導体構造部の上に形成された樹脂フィルムを有して成るフレキシブル半導体装置。かかるフレキシブル半導体装置では、樹脂フィルムには開口部が形成されており、その開口部に半導体構造部の表面と接触する導電部材が形成されており、半導体構造部が半導体層および半導体層の表面に形成された絶縁層を有して成る。

(もっと読む)

半導体装置

【目的】高耐圧NMOSFETなどのレベルシフト素子から素子分離溝越しに隣接した高電位浮遊領域への高電位配線を、高耐圧NMOSFETの耐圧低下や層間絶縁膜の破壊および素子分離溝の分離耐圧劣化を招くことなく、形成できる半導体装置を提供する。

【解決手段】高電位配線9の直下にnドレインバッファ層10と接してp-拡散層11とこれに接するp+拡散層12を形成することで、高電位配線9が横切る絶縁膜44aの電界強度を低下できる。絶縁膜44aの電界強度を低下させることで、高耐圧NMOSFET20の耐圧低下や層間絶縁膜5の破壊および素子分離溝(トレンチ4a)の分離耐圧劣化を防止できる。

(もっと読む)

半導体装置およびその製造方法

【課題】深い凹部によって構成される凹凸を有して無くても、耐圧を向上させられるようにする。

【解決手段】活性層3のうち半導体素子の下方における埋込絶縁膜4と隣接する位置に、円形状の中心領域10aを囲むようにリング状のp型領域10およびn型領域11を交互に繰り返し形成する。これにより、カソード電極8に対して高電圧を印加すると共にアノード電極9および支持基板2をGNDにした場合、n型領域11の間に配置されるp型領域10のうち埋込絶縁膜4に隣接する位置に電荷が誘起され、n型領域11のうち埋込絶縁膜4と隣接する位置には電荷が誘起されないようにできる。このため、擬似的なフィールドプレートを構成することが可能となり、耐圧を向上させられる。

(もっと読む)

半導体装置

【課題】1個の柱を用いてインバータを構成することにより、高集積なCMOSインバータ回路からなる半導体装置を提供する。

【解決手段】第1のシリコンと、該第1のシリコンとは極性が異なる第2のシリコンと、前記第1のシリコンと前記第2のシリコンとの間に配置され、基板に対して垂直方向に延びている第1の絶縁物とからなる1本の柱と、前記第1のシリコンの上下のそれぞれに配置され、前記第1のシリコンとは極性が異なる第1の高濃度不純物を含むシリコン層と、前記第2のシリコンの上下のそれぞれに配置され、前記第2のシリコンとは極性が異なる第2の高濃度不純物を含むシリコン層と、前記第1のシリコンと前記第2のシリコンと前記第1の絶縁物とを取り囲む第2の絶縁物と、前記第2の絶縁物を取り囲む導電体とを含む半導体装置により、上記課題を解決する。

(もっと読む)

81 - 100 / 404

[ Back to top ]