Fターム[5F110FF12]の内容

Fターム[5F110FF12]に分類される特許

61 - 80 / 413

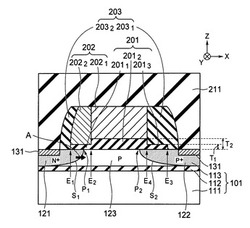

半導体装置

【課題】トンネルトランジスタにおいて、その寄生容量を低減したゲート電極を提供する。

【解決手段】ゲート絶縁膜201を介して形成されたゲート電極202を挟むように形成された、第1導電型のソース領域121及び前記第1導電型とは逆導電型の第2導電型のドレイン領域122と、基板101内において前記ソース領域121と前記ドレイン領域122との間に形成された、第2導電型のチャネル領域123とを備える。そして、前記ゲート絶縁膜201は、前記ソース領域上に位置し、チャネル幅方向に平行な第1のエッジE1と、前記チャネル領域上又は前記ソース領域上に位置し、チャネル幅方向に平行な第2のエッジE2とを有し、第1の膜厚を有する第1の絶縁膜部分を有する。さらに、前記ゲート絶縁膜201は、前記第1の絶縁膜部分に対して前記ドレイン領域側に位置し、前記第1の膜厚よりも厚い第2の膜厚を有する第2の絶縁膜部分を有する。

(もっと読む)

半導体装置、モジュール及び電子機器

【課題】本発明は、アクティブマトリクス型の表示装置において、配線の断面積を増大させることなく、相性の悪い2つの膜(ITO膜とアルミニウム膜)からなる配線や電極等を接続し、且つ、大画面化しても低消費電力を実現することを課題とする。

【解決手段】本発明は、上層と、上層よりも広い幅を有する下層とからなる2層構造とする。TiまたはMoからなる第1導電層を設け、その上に電気抵抗値の低いアルミニウム単体(純アルミニウム)からなる第2導電層を設ける。上層の端面から突出させた下層部分と、ITOとを接合させる。

(もっと読む)

窒化ガリウム系半導体装置および半導体装置の製造方法

【課題】窒化ガリウム系半導体のドライエッチングに、塩素系ガスを用いたICP−RIEを用いると、誘電結合型プラズマは、温度が高いので、エッチングされた面に凹凸ができ、半導体にダメージを与え、塩素が残留する。

【解決手段】窒化ガリウム系半導体からなる第1の半導体層を形成する第1半導体層形成工程と、第1の半導体層の一部を、臭素系ガスを用いて、マイクロ波プラズマプロセスでドライエッチングして、リセス部を形成するリセス部形成工程と、を備え、窒化ガリウム系半導体装置を製造する半導体装置の製造方法を提供する。

(もっと読む)

半導体装置

【課題】正確にメインセルに流れる電流を検出することができると共に、高い電圧が用いられる場合でもその影響を受け難い半導体装置を提供する。

【解決手段】メインセルとセンスセルとをトレンチ分離構造1dによって絶縁分離する。これにより、メインセルのコレクタに対して100V以上の高電圧が印加されても、それに起因するノイズが電流検出用の出力端子に誘起されないようにできる。また、センスセルのエミッタ電位がセンス抵抗Rsに流れる電流によって上昇しても、メインセルのエミッタと電気的に完全に分離されているため、寄生トランジスタが動作することもない。勿論、抵抗層14から発生させられたノイズが電流検出用の出力端子に誘起されることも抑制できる。したがって、正確にメインセルに流れる電流を検出することができると共に、高い電圧が用いられる場合でもその影響を受け難い半導体装置とすることが可能となる。

(もっと読む)

電気光学装置及び電子機器

【課題】液晶装置等の電気光学装置において、サンプリング用トランジスターの高速化とプッシュダウン現象の抑制を両立させ、高品位な表示を行う。

【解決手段】電気光学装置は、データ線(6)に画像信号線(60)から供給される画像信号をサンプリングするサンプリング用トランジスター(71)を備える。サンプリング用トランジスターのゲート絶縁膜(73)は、ゲート電極(71G)の第1ソースドレイン領域(74S)側の縁部(71Ges)に重なる部分及びゲート電極の第2ソースドレイン領域(74D)側の縁部(71Ged)に重なる部分の各々の膜厚が、ゲート電極の中央部(71Gc)に重なる部分の膜厚よりも厚くなるように形成されている。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】オフ電流が低減できる半導体装置及び半導体装置を提供する。

【解決手段】絶縁表面上に形成され、ソース領域、ドレイン領域、及びチャネル形成領域を含む単結晶半導体層と、単結晶半導体層を覆うゲート絶縁膜と、ゲート絶縁膜を介して、チャネル形成領域に重畳するゲート電極と、ソース領域に接続されるソース電極と、ドレイン領域に接続されるドレイン電極と、を有し、ソース領域及びドレイン領域のうち、少なくともドレイン領域は、チャネル形成領域に隣接する第1の不純物領域と、第1の不純物領域に隣接する第2の不純物領域と、を含み、第1の不純物領域の深さ方向の不純物濃度分布の極大は、第2の不純物領域の深さ方向の不純物濃度分布の極大よりも絶縁表面側にあり、ドレイン電極は、ドレイン領域に含まれる第2の不純物領域の一部と接続する半導体装置を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】電子及び正孔の移動度を向上させたSOI構造のCMOSの提供

【解決手段】Si基板1上にシリコン窒化膜2及びシリコン酸化膜3を介して貼り合わせられ、島状に絶縁分離されたGe層8(第2の半導体層)が設けられ、このGe層8に高濃度のソースドレイン領域(14、15)が形成されたPチャネルのMISFETと、Si基板1上にシリコン窒化膜2及び一部に空孔5を有するシリコン酸化膜3を介して、空孔5直上の歪みSi層7を挟み、左右にSiGe層6を有する構造からなるエピタキシャル半導体層(第1の半導体層)が島状に絶縁分離されて設けられ、歪みSi層7には概略チャネル領域が形成され、SiGe層6には概略高濃度及び低濃度のソースドレイン領域(10、11、12,13)が形成されたNチャネルのMISFETとから構成したCMOS。

(もっと読む)

半導体装置、表示装置、電子機器

【課題】作製工程を増やすことなく、凹凸形状の画素電極を作製することを目的とする。

【解決手段】凸部は、フォトマスクを用いて作製すると再現性の高いものが得られるため、画素TFT1203の作製工程にしたがって作製すればよい。画素TFT1203の作製と同様に積層される半導体層、ゲート絶縁膜および導電膜を積層して凸部を形成する。こうして形成された凸部および同一工程で形成された画素TFT、駆動回路に含まれるTFTを覆うように層間絶縁膜を形成する。凹凸を有する層間絶縁膜が形成されたら、その上に画素電極を形成する。画素電極の表面も絶縁膜の凹凸の影響を受け表面が凹凸化する。

(もっと読む)

半導体装置及びその製造方法

【課題】電子及び正孔の移動度を向上させたSOI構造のCMOSの提供

【解決手段】Si基板1上にシリコン窒化膜2及びシリコン酸化膜3を介して、歪みSi層6を挟み、左右にSiGe層5を有する構造からなる第1のエピタキシャル半導体層及び歪みGe層8を挟み、左右にSiGe層7を有する構造からなる第2のエピタキシャル半導体層が島状に絶縁分離されて設けられ、歪みSi層6には概略チャネル領域が形成され、SiGe層5には概略高濃度及び低濃度のソースドレイン領域(10、11、12,13)が形成された包囲型ゲート電極構造のNチャネルのMISFETと、歪みGe層8には概略チャネル領域が形成され、SiGe層7には概略高濃度のソースドレイン領域(14、15)が形成された包囲型ゲート電極構造のPチャネルのMISFETとから構成したCMOS。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】

製造プロセスのステップ数を少なくでき、素子の構造が簡単でコストを抑制することが可能な薄膜トランジスタを提供する。

【解決手段】本発明の薄膜トランジスタ100は、主面を有する基材110と、前記基材110の前記主面に対する積層方向に配設される遮光層111と、前記積層方向からみて、前記遮光層111に含まれるように設けられる有機半導体層150と、前記有機半導体層150と接触するように設けられ、互いに対向しチャネル領域を形成するソース電極120及びドレイン電極130と、前記積層方向からみて、前記有機半導体層150の外周において前記ソース電極120と前記ドレイン電極130と重畳しない溝部165が設けられたゲート絶縁層160と、前記積層方向からみて前記有機半導体層150を含むように、前記ゲート絶縁層160上及び前記溝部165に設けられるゲート電極140と、からなることを特徴とする。

(もっと読む)

横型素子を有する半導体装置

【課題】高速スイッチング動作を行う場合でも、アバランシェブレークダウンを抑制でき、スイッチング損失低減や素子破壊を抑制することが可能な構成とする。

【解決手段】横型FWD7などの横型素子において、SRFP21の全抵抗Rの抵抗値を90kΩ〜90MΩ、好ましくは270kΩ〜27MΩ、より好ましくは900kΩ〜9MΩとすることにより、2ndピーク時のアノード電流IAなどの電流が大きくなることを抑制できる。これにより、高速スイッチング動作を行う場合でもアバランシェブレークダウンを抑制でき、横型FWD7のスイッチング損失低減や素子破壊を抑制することが可能となる。

(もっと読む)

半導体装置

【課題】従来に比してオン電圧性能に優れた横型IGBT、および順方向電圧特性に優れた横型FWDを同一基板上に構成可能とする半導体装置を提供する。

【解決手段】半導体基板上において、横型IGBTと、横型FWDとが、絶縁体であるトレンチ絶縁仕切り部を挟むように横方向に隣接配置されて成る半導体装置であって、横型IGBTは、平面視した場合に、エミッタ領域と当該横型IGBTのドリフト領域との境界面の幅がコレクタ領域と当該横型IGBTのドリフト領域との境界面の幅より狭くなるよう形成されており、横型FWDは、平面視した場合に、カソード領域と当該横型FWDのドリフト領域との境界面の幅がアノード領域と当該横型FWDのドリフト領域との境界面の幅より狭くなるよう形成されていることを特徴とする、半導体装置。

(もっと読む)

薄膜トランジスタアレイパネル

【課題】薄膜トランジスタアレイパネルにおいて、酸化シリコン膜の厚さを減少させる。

【解決手段】本発明の実施形態に係る薄膜トランジスタアレイパネルは、絶縁基板と、絶縁基板上に配置され、ゲート電極を含むゲート線と、ゲート線上に配置され、窒化シリコンを含む第1ゲート絶縁膜と、第1ゲート絶縁膜上に配置され、酸化シリコンを含む第2ゲート絶縁膜と、第2ゲート絶縁膜上に配置される酸化物半導体と、酸化物半導体上に配置され、ソース電極を含むデータ線と、酸化物半導体上に配置され、ソース電極と対向するドレイン電極と、ドレイン電極と接続される画素電極と、を含み、第2ゲート絶縁膜の厚さは200Å以上500Å未満であることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】従来のゲートラスト法の問題点を解決し、さらなる微細化に対応できるゲート構造を実現する。

【解決手段】半導体領域101上から、ダミーゲート構造を除去してリセス107aを形成した後、リセス107aの底部の半導体領域101の表面上に界面層108を形成する。次に、界面層108上及びリセス107aの側壁上に高誘電率絶縁膜109を形成すした後、リセス107a内部の高誘電率絶縁膜109上に、ゲート電極の少なくとも一部となる金属含有膜110を形成する。界面層108上に形成されている部分の高誘電率絶縁膜109の厚さは、リセス107aの側壁上に形成されている部分の高誘電率絶縁膜109の厚さよりも厚い。

(もっと読む)

半導体装置及びその作製方法

【課題】従来では、LDD構造を備えたTFTやGOLD構造を備えたTFTを形成しようとすると、その製造工程が複雑なものとなり工程数が増加してしまう問題があった。

【解決手段】第2のドーピング工程によって低濃度不純物領域24、25を形成した後、第4のエッチング工程を行うことによって、第3の電極18cに重なる低濃度不純物領域の幅と、第3の電極に重ならない低濃度不純物領域の幅とを自由に調節できる。こうして、第3の電極18cと重なっている領域は、電界集中の緩和が達成されてホットキャリアによる防止ができるとともに、第3の電極18cと重なっていない領域は、オフ電流値を抑えることができる。

(もっと読む)

薄膜トランジスタ基板の製造方法

【課題】基板の反りを防止可能な構造を備えたことにより長期的な強度および特性の確保が可能な薄膜トランジスタ基板の製造方法を提供する。

【解決手段】基板3上に成膜されたゲート絶縁膜7と、ゲート絶縁膜7上にパターン形成された半導体薄膜9とを備えた薄膜トランジスタ基板1において、ゲート絶縁膜7における半導体薄膜9の外側となる位置には、溝パターン101が設けられている。ゲート絶縁膜7は、窒化シリコン膜7aとその上部の酸化シリコン膜7bとの積層構造からなり、溝パターン101は、窒化シリコン膜7aに形成されている。基板3はガラス材料からなる。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタを用いて、高速動作が可能で、信頼性も高い半導体装置を歩留まりよく作製する。

【解決手段】絶縁膜上にマスクを形成し、該マスクを微細化する。微細化されたマスクを用いて凸部を有する絶縁層を形成し、これを用いて、微細なチャネル長(L)を有するトランジスタを形成する。また、トランジスタを作製する際に、微細化された凸部の上面と重なるゲート絶縁膜の表面に平坦化処理を行う。これにより、トランジスタの高速化を達成しつつ、信頼性を向上させることが可能となる。また、絶縁膜を凸部を有する形状とすることで、自己整合的にソース電極及びドレイン電極を形成することができ、製造工程の簡略化、また生産性を向上させることが可能となる。

(もっと読む)

半導体装置

【課題】接続配線に起因する耐圧低下を防止できる半導体装置の耐圧特性をさらに向上させることができる半導体装置の提供。

【解決手段】半導体層の第1素子領域に配置されており、第1主電極と第2主電極を有する第1種類の第1半導体素子と、半導体層の第2素子領域に配置されており、第3主電極と第4主電極を有する第2種類の第2半導体素子とを備え、第1素子領域と第2素子領域は、電流が流れる方向に対して直交する方向に隣接し、かつ、第1素子領域と第2素子領域を含む素子領域全体で一巡する形に形成され、半導体層を平面視したときに、第1素子領域の曲率は、第2素子領域の曲率よりも小さい。

(もっと読む)

横型半導体装置

【課題】高い耐圧性能と長期信頼性を両立可能な半導体装置を提供する。

【解決手段】半導体基板の一主表面上においてドリフト領域を挟むように第1電極部と第2電極部とが各々分離形成され、ドリフト領域上部には酸化膜層が形成され、ドリフト領域、第1電極部、第2電極部、および酸化膜層が層間絶縁膜層により覆われた横型半導体装置であって、第1導電型半導体と第2導電型半導体とを交互にドリフト領域におけるキャリアのドリフト方向へ直列接続して成る連続接合半導体層が酸化膜層と層間絶縁膜層との境界部に設けられ、連続接合半導体層の一方端部は、第2電極部と並列に電源電位線に接続されていることを特徴とする、横型半導体装置である。

(もっと読む)

半導体基板の貼り合わせ方法、半導体装置の製造方法

【課題】デバイス形成用半導体基板と保持用半導体基板とを貼り合わせるに当たり、両半導体基板の間に挟みこまれたパーティクル等の微粒子が、貼り合わせ面の積層間膨れや剥がれ、またはボイド欠陥を誘起することを防止する。

【解決手段】デバイス形成用半導体基板1にシリコン酸化膜4を形成する。また、保持用半導体基板2にシリコン酸化膜6を形成し、該シリコン酸化膜6上に有機溶剤に有機バインダーを加えた液体等からなる半導体ウエハ用液状絶縁材料の塗布膜7を形成する。次に、デバイス形成用半導体基板1と保持用半導体基板2とをシリコン酸化膜4とシリコン酸化膜6上の塗布膜7とを介して貼り合わせる。

(もっと読む)

61 - 80 / 413

[ Back to top ]