Fターム[5F110FF12]の内容

Fターム[5F110FF12]に分類される特許

41 - 60 / 413

半導体装置、及び半導体装置の作製方法

【課題】微細化及び高集積化を達成した酸化物半導体を用いた半導体装置、及び半導体装置の作製工程において、安定した電気的特性を付与し、高信頼性化する。また、上記半導体装置の作製工程において、不良を抑制し、歩留まりよく作製する技術を提供する。

【解決手段】酸化物半導体層を含むトランジスタを有する半導体装置において、酸化物半導体膜を、絶縁層に設けられたトレンチに設ける。トレンチは下端コーナ部及び曲率半径が20nm以上60nm以下の曲面状の上端コーナ部を含み、酸化物半導体膜は、トレンチの底面、下端コーナ部、上端コーナ部、及び内壁面に接して設けられる。酸化物半導体膜は、少なくとも上端コーナ部において表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜である。

(もっと読む)

半導体装置および当該半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置を提供すること。また、安定した電気的特性が付与された、信頼性の高い半導体装置を提供すること。

【解決手段】絶縁層に凸状構造体を形成し、該凸状構造体に接して酸化物半導体層のチャネル形成領域を設けることで、チャネル形成領域を3次元方向(基板垂直方向)に延長させる。これによって、トランジスタの微細化を達成しつつ、実効的なチャネル長を延長させることができる。また、凸状構造体の上面と側面とが交わる上端コーナー部に曲面を形成し、酸化物半導体層が当該曲面に垂直なc軸を有する結晶を含むように形成する。これによって、酸化物半導体層の可視光や紫外光の照射による電気的特性の変化を抑制することができる。

(もっと読む)

半導体装置

【課題】微細化及び高集積化を達成した酸化物半導体を用いた半導体装置において、安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタ(半導体装置)において、酸化物半導体膜を、絶縁層に設けられたトレンチ(溝)に設ける。トレンチは曲率半径が20nm以上60nm以下の曲面状の下端コーナ部を含み、酸化物半導体膜は、トレンチの底面、下端コーナ部、及び内壁面に接して設けられる。酸化物半導体膜は、少なくとも下端コーナ部において表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜である。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】半導体素子、例えばFETのソース領域にショットキー電極を形成し、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフまたはエンハンスメントモード動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上に配設され、内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、該窒化物半導体層30にオミック接合されたドレイン電極50と、該ドレイン電極50と離間して配設され、該窒化物半導体層30にショットキー接合されたソース電極60と、該ドレイン電極50と該ソース電極60との間の窒化物半導体層30上及び該ソース電極60の少なくとも一部上にかけて形成された誘電層40と、該ドレイン電極50と離間して誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上に形成されたゲート電極70とを含む。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】高耐圧及び高電流の動作が可能な半導体素子及びその製造方法を提案する。

【解決手段】内部に2次元電子ガス(2DEG)チャンネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50の方向に突出した多数のパターン化された突起61を備え、内部に窒化物半導体層30にオーミック接合されるオーミックパターン65を含むソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上に、且つ、パターン化された突起61を含んでソース電極60上の少なくとも一部に亘って形成された誘電層40と、一部が、誘電層40を間に置いてソース電極60のパターン化された突起61部分及びドレイン方向のエッジ部分の上部に形成されたゲート電極70と、を含んでなる。

(もっと読む)

半導体装置

【課題】半導体装置において、高電圧の配線層とその下方を横切るように配置された抵抗層との間の絶縁膜の耐圧を確保し、この配線層と抵抗層との間で破壊が起きるのを抑制することを目的とする。

【解決手段】第1半導体領域10に接続され第2半導体領域11上を通過するように第3配線層22が配置されている。第3配線層22と第2半導体領域11との間に配置される絶縁膜14内には、一端が第3配線層22に接続されると共に、他端が第1半導体領域11よりも電位の低い制御端子12に接続され、且つ第3配線層22とSOI層2との間において第3配線層22を少なくとも1回以上横切る構成で抵抗層25が配置されている。この抵抗層25は、第3配線層22を横切る部位の上面が他の部位よりも下方位置となるように段差状に形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】包囲型ゲート電極及び空孔付きの歪みSOI構造のMISFETの提供

【解決手段】

半導体基板1上に第1の絶縁膜2が設けられ、第1の絶縁膜2上に第2の絶縁膜3が選択的に設けられ、第2の絶縁膜3上に選択的に一対の第1の半導体層6が設けられ、第1の半導体層6にそれぞれ1側面を接し、空孔5上に一対の第2の半導体層8が設けられ、第2の半導体層8間に2側面を接し、残りの周囲にゲート絶縁膜14を介してゲート電極15に包囲された、歪み構造の第3の半導体層7が設けられ、第1及び第2の半導体層(6、8)には概略ソースドレイン領域(10、11、12、13)が設けられ、第3の半導体層7には概略チャネル領域が設けられ、ソースドレイン領域(10、13)及び包囲型ゲート電極15には配線体(19、20、22、23)が接続されているMISFET。

(もっと読む)

微細構造物の製造方法、該微細構造物の製造方法により製造される微細構造物、及び該微細構造物を有する電界効果型半導体素子

【課題】10nm程度の溝を有する微細構造物を安価で簡便かつ高精度に作製可能な微細構造物の製造方法、該微細構造物の製造方法により製造される微細構造物、及び該微細構造物を有する電界効果型半導体素子を提供すること。

【解決手段】本発明の微細構造物の製造方法は、トップダウン形成法により、基板上に少なくとも2つの凸状の形状からなる第1の構造体を形成する第1の構造体形成工程と、ボトムアップ形成法により、前記第1の構造体が形成された基板上に形成材料を堆積させ、隣接する前記第1の構造体の中間位置に凹状の溝を有する第2の構造体を形成する第2の構造体形成工程と、を含むことを特徴とする。

(もっと読む)

半導体装置

【課題】長期に亘って信頼性の高い横型MISFETを有する半導体装置を提供する。

【解決手段】本発明に係る半導体装置1は、半導体基板11上に形成された半導体層13と、半導体層13に溝状に形成され、その内壁が絶縁膜31で被覆され、絶縁膜31の内部にゲート電極32が埋設されたトレンチ溝30と、半導体層13上に、トレンチ溝30と少なくとも一部が対向配置する位置に形成されたゲート配線51と、ゲート配線51を挟むように半導体層13上に形成されたソース電極52、及びドレイン電極53とを具備する。半導体層13におけるオン動作時の電流経路は、ソース電極52とドレイン電極53の間の半導体層13の表面領域を実質的に経由せず、上記トレンチ溝30の側面近傍を経由する。

(もっと読む)

薄膜トランジスタ及びその製造方法並びに画像表示装置

【課題】薄膜トランジスタにおいて、ゲート絶縁膜に直接ストライプ状に凹部を形成することで隔壁形成プロセスを省き、前記凹部をガイドとして塗布法により精度よく半導体溶液を所望の場所に形成し、トランジスタ素子分離を行うことのできる薄膜トランジスタの構造を提供する。また、その構造を用いた薄膜トランジスタの製造方法、及びそれを用いたが画像表示装置を提供すること。

【解決手段】基板と、前記基板上に形成されたゲート電極と、前記基板上及び前記ゲート電極上のゲート絶縁体層と、前記ゲート絶縁体層に形成された凹部と、前記絶縁体層の凹部内に形成される半導体層と、前記半導体層上の中央部に設けられる保護膜と、前記半導体層の両端部で接続されるソース電極とドレイン電極と、を有する薄膜トランジスタにおいて、前記ゲート絶縁体層の凹部がストライプ状に形成されていることを特徴とする薄膜トランジスタとする。

(もっと読む)

薄膜トランジスタとその製造方法、および当該薄膜トランジスタを用いた画像表示装置

【課題】隔壁形成プロセスを省き、かつ、塗布法により半導体溶液を所望の場所に形成し、トランジスタ素子分離を行うことのできる薄膜トランジスタを提供する。

【解決手段】基板上に形成された梯子状の凸部を有するゲートバス電極と、ゲートバス電極の表面形状に沿うように当該ゲートバス電極上および基板上に形成されたゲート電極と、ゲート電極の凹凸に沿うようにゲート電極上および基板上に形成されたゲート絶縁体層と、ゲート絶縁体層の凹部内に形成された半導体層と、半導体層の中央に形成された保護膜と、半導体層の両端部で接続されたソース電極とドレイン電極とを備える。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】窒化物半導体を用いたノーマリーオフ動作の電界効果型トランジスタにおいて、閾値電圧が制御でき、十分な素子特性が得られるようにする。

【解決手段】c軸方向に結晶成長された窒化物半導体から構成されて主表面が極性面とされた第1領域121,第1領域121より厚く形成された第2領域122,および、第1領域121と第2領域122との間に形成されて主表面が半極性面とされた第3領域123を備える半導体層101を備える。また、窒化物半導体装置は、第1領域121における半導体層101の上に形成されたドレイン電極102と、第2領域122における半導体層101の上に形成されたソース電極103と、第3領域123における半導体層101の上に形成されたゲート電極104とを備える。

(もっと読む)

窒化物半導体装置及びその製造方法

【課題】低オン抵抗、高耐圧及び高信頼性を達成する。

【解決手段】窒化物半導体装置110は、第1半導体層3、第2半導体層4、第1電極10、第2電極7、第3電極8、第1絶縁膜6及び第2絶縁膜5を備える。第1半導体層3は、窒化物半導体を含む。第2半導体層4は、第1半導体層3上に設けられ、孔部4aを有する。第2半導体層4は、第1半導体層3よりも広い禁制帯幅を有する窒化物半導体を含む。第1電極10は、孔部4a内に設けられる。第1電極10の一方側に第2電極7、他方側に第3電極8が設けられ、それぞれ第2半導体層4と電気的に接続される。第1絶縁膜6は、酸素を含有する膜であって、第1電極10と孔部4aの内壁とのあいだ、及び第1電極10と第2電極7とのあいだに設けられ、第3電極8と離間して設けられる。第2絶縁膜5は、窒素を含有する膜であって、第1電極10と第3電極8とのあいだで第2半導体層4に接して設けられる。

(もっと読む)

半導体装置

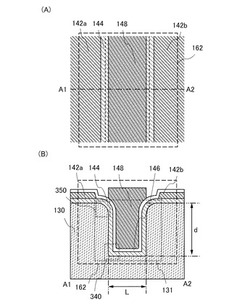

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置の提供。

【解決手段】酸化物半導体材料を用いたトランジスタ162と、酸化物半導体以外の半導体材料を用いたトランジスタ160を組み合わせて用いることにより、書き込み回数にも制限が無く、長期間にわたる情報の保持ができる、新たな構造の半導体装置を実現することができる。さらに、酸化物半導体以外の半導体材料を用いたトランジスタと酸化物半導体材料を用いたトランジスタとを接続する接続電極130bを、当該接続電極と接続する酸化物半導体以外の半導体材料を用いたトランジスタの電極129より小さくすることにより、新たな構造の半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させることができる。

(もっと読む)

半導体記憶装置およびその作製方法

【課題】半導体記憶装置におけるデータ保持のためのリフレッシュ動作の回数を低減し、消費電力の小さい半導体記憶装置を提供する。また、三次元の形状を適用することで、集積度を高めても短チャネル効果の影響が低減され、かつ従来に比べてフォトリソグラフィ工程数の増加を抑えた半導体記憶装置を提供する。

【解決手段】溝部の設けられた絶縁膜103と、溝部を挟んで離間した一対の電極116と、溝部の側面および底面と接し、溝部の深さよりも厚さの薄い、一対の電極116と接する酸化物半導体膜106と、酸化物半導体膜106を覆うゲート絶縁膜112と、ゲート絶縁膜112を介して酸化物半導体膜106と重畳して設けられたゲート電極112と、を有するトランジスタ150と、キャパシタ160と、を有する半導体記憶装置である。

(もっと読む)

半導体装置

【課題】半導体基板上へのVFETと他の種類の素子との混載が可能でありながら、半導体基板上に積層される半導体層の表面に大きな段差を有しない半導体装置を提供する。

【解決手段】P型シリコン基板2上には、酸化シリコンからなるボックス層3、N+型横方向導電層4およびN−型表面層5が積層されている。ボックス層3上には、N−型表面層5の表面からボックス層3に至る深さを有する、平面視環状のディープトレンチ6が形成されている。ディープトレンチ6およびボックス層3に取り囲まれるトランジスタ形成領域8は、その周囲から分離されている。このトランジスタ形成領域8において、N−型表面層5の表層部には、ソース領域14およびドレイン領域16が形成されている。またディープトレンチ6の側面に沿って、ドレイン領域16とN+型横方向導電層4とに接続されたN+型縦方向導電層17が形成されている。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】表示装置に含まれるTFTのゲート電極と、ソース電極及びドレイン電極との間の絶縁耐圧が低くなる場合がある。

【解決手段】表示装置であって、基板上に形成されるゲート電極と、前記ゲート電極上に、前記ゲート電極を覆うように形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成された半導体層と、前記半導体層上に形成されたソース配線と、前記半導体層上に形成されたドレイン配線と、を有し、前記半導体層は、前記ゲート電極の上方に形成されたチャネル層と、前記チャネル層の両側に、それぞれ前記ソース配線またはドレイン配線を介して分離して形成されたエッチング防止層と、を有する、ことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート動作に関与する結晶表面における表面電荷蓄積を大幅に低減し、ピンチオフ特性が得られる、高性能のInN系FETを提供すること。

【解決手段】チャネル層としてInN系半導体を含む電界効果トランジスタである半導体装置であって、InN系半導体でなるチャネル層2の表面(c面)に、段差を形成して窒化物半導体の六方晶結晶のa面もしくはm面でなる側壁面2aを形成し、この側壁面2aにゲート電極6が配置され、ゲート電極6を挟むようにソース電極3とドレイン電極4がc面上に形成されている。

(もっと読む)

薄膜トランジスターの製造方法

【課題】例えば製造工程数の増加を招くことなく、複数の半導体層に水素化処理を確実に行う。

【解決手段】薄膜トランジスターの製造方法は、基板(10)上に、複数の半導体層(110)を同一層として形成する工程と、複数の半導体層を覆うようにシリコン酸化膜(130)を形成する工程と、シリコン酸化膜上に複数の半導体層を覆うようにシリコン窒化膜(140)を形成する工程と、シリコン窒化膜上に複数の半導体層を覆うように導電膜(121)を形成する工程と、導電膜及びシリコン窒化膜をエッチングにより一括でパターニングすることで、導電膜の一部からなるゲート電極(120)を形成するとともに、このエッチングの際、シリコン酸化膜の上層をオーバーエッチングする工程と、オーバーエッチングする工程の後に、半導体層にオーバーエッチングされたシリコン酸化膜を介して水素化処理を行う工程と、を有する。

(もっと読む)

半導体装置およびその作製方法

【課題】従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタのオン状態とオフ状態が切り換わるのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。

【解決手段】酸化物半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。ソース電極とドレイン電極との距離を狭くしてもゲート電極用のトレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

41 - 60 / 413

[ Back to top ]