Fターム[5F110FF23]の内容

Fターム[5F110FF23]に分類される特許

201 - 220 / 2,062

高分子化合物、化合物およびその用途

【課題】光電変換素子に含まれる有機層に用いた場合に、光電変換素子の光電変換効率が高くなる高分子化合物を提供することを目的とする。

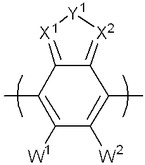

【解決手段】式(1)で表される構造単位を有する高分子化合物。

(1)

〔式中、X1及びX2は、同一又は相異なり、窒素原子又は=CH−を表す。Y1は、硫黄原子、酸素原子、セレン原子、−N(R1)−又は−CR2=CR3−を表す。R1、R2及びR3は、同一又は相異なり、水素原子又は置換基を表す。W1は、シアノ基、フッ素原子を有する1価の有機基又はハロゲン原子を表す。W2は、シアノ基、フッ素原子を有する1価の有機基、ハロゲン原子又は水素原子を表す。〕

(もっと読む)

半導体装置およびその製造方法

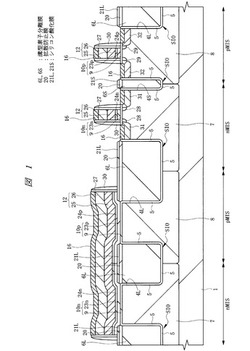

【課題】溝型の素子間分離部により囲まれた活性領域に形成される電界効果トランジスタにおいて、所望する動作特性を得ることのできる技術を提供する。

【解決手段】素子分離部SIOを、溝型素子分離膜6L,6Sと、溝型素子分離膜6L,6Sの上面に形成されたシリコン膜またはシリコン酸化膜からなる厚さ10〜20nmの拡散防止膜20と、拡散防止膜20の上面に形成された厚さ0.5〜2nmのシリコン酸化膜21L,21Sとから構成し、拡散防止膜20の組成をSiOx(0≦x<2)とし、溝型素子分離膜6L,6Sおよびシリコン酸化膜21L,21Sの組成をSiO2とする。

(もっと読む)

金属酸化物半導体粒子分散組成物

【課題】電気的特性に優れる金属酸化物半導体薄膜を低温でも形成することが可能な金属酸化物半導体粒子分散組成物を提供する。更に、本発明は、該金属酸化物半導体粒子分散組成物を用いた金属酸化物半導体薄膜、透明導電膜及び薄膜トランジスタを提供する。

【解決手段】金属酸化物半導体粒子と分散媒を含有する金属酸化物半導体粒子分散組成物であって、前記金属酸化物半導体粒子は、平均粒子径が1〜50nmであり、かつ、平均粒子径/平均結晶子径が1〜3である金属酸化物半導体粒子分散組成物。

(もっと読む)

電荷注入特性が高い有機薄膜トランジスタ

【課題】トランジスタ特性が優れ、しかも大面積化が容易なボトムゲート・ボトムコンタクト構造の有機薄膜トランジスタ、及びその製造方法を提供すること。

【解決手段】第1導電層及び第2導電層からなるソース・ドレイン電極を有するボトムゲート・ボトムコンタクト構造の有機薄膜トランジスタであって、該第1導電層は、塗布法を用いて形成されたものであり、該第1導電層の端部は該第2導電層の端部と比較して電極ブロックの内側に位置している有機薄膜トランジスタ。

(もっと読む)

薄膜トランジスターの製造方法、及び電気光学装置

【課題】所期の特性が得られ高品位な表示を得ることができる薄膜トランジスターの製造方法、及び電気光学装置を提供する。

【解決手段】薄膜トランジスターとしてのTFT素子の製造方法は、第1基板12上に半導体膜38を形成する工程と、半導体膜38上にゲート絶縁膜53を形成する工程と、ゲート絶縁膜53上にゲート電極35aを形成する工程と、ゲート絶縁膜53及びゲート電極35aを覆って、半導体膜38に注入する不純物72の量を調整するための、ゲート絶縁膜53とエッチングの選択比が異なる調整膜73を形成する工程と、調整膜73を介して半導体膜38に不純物72を注入する工程と、半導体膜38にアニール処理を施す工程と、を有する。

(もっと読む)

電気光学装置、投射型表示装置、電気光学装置の製造方法

【課題】画素電極表面でのヒロックの発生や、平坦化絶縁膜において凹部を埋める部分での空洞の発生を防止することのできる電気光学装置、該電気光学装置を用いた投射型表示装置、および当該電気光学装置の製造方法を提供すること。

【課題手段】電気光学装置100の素子基板10において、反射性の画素電極9aの上層側に設けられた平坦化絶縁膜17は、画素電極9a上に積層された層がドープトシリコン酸化膜170からなる。ドープトシリコン酸化膜170の熱膨張係数は、画素電極9aを構成するアルミニウム膜の熱膨張係数との差が小さい。このため、加熱した状態で平坦化絶縁膜17を成膜しても、画素電極9aおよび平坦化絶縁膜17に大きな熱応力が発生しないので、画素電極9aの表面にヒロック等の欠陥が発生しにくい。また、ドープトシリコン酸化膜170は、段差被覆性に優れている。

(もっと読む)

半導体薄膜、薄膜トランジスタ及びその製造方法

【課題】耐還元性に優れた半導体薄膜及びその製造方法、チャネル層上に酸素透過性膜等のバッファー層を設けなくても安定したTFT特性が得られる薄膜トランジスタ及びその製造方法を提供する。

【解決手段】1種以上のアモルファス金属酸化物を含有し、前記金属酸化物の少なくとも一部の金属原子にOH基が結合している半導体薄膜。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】 水分に起因するTFT特性の変化を抑制した薄膜トランジスタおよびその製造方法を提供する。

【解決手段】 本発明の薄膜トランジスタは、基板上に、少なくともゲート電極、ゲート絶縁膜、活性層、ソース電極、およびドレイン電極が設けられ、活性層上にソース電極およびドレイン電極が設けられたものである。活性層は、アモルファス酸化物半導体により構成されており、ゲート絶縁膜内に存在する第1の水分量が活性層に存在する第2の水分量よりも少ない。

(もっと読む)

埋め込み配線を備える基板、その製造方法、これを利用する半導体装置およびその製造方法

【課題】 低抵抗の埋め込み配線を備える基板の製造方法を提供する。

【解決手段】 始めに半導体用基板100の第1面S1上に導電層120を形成する。次に、導電層120をパターニングして第1方向に延長する線形の導電層パターン122を形成する。導電層120をパターニングするとき露出する半導体用基板100をエッチングして導電層パターン120の下部に第1方向に延長する線形の半導体パターン104を形成する。次に導電層パターン120および半導体パターン104上に絶縁層150を形成する。半導体用基板100の第1面S1側の絶縁層150が支持基板160と当接するように支持基板160上に配置する。次に半導体用基板100のイオン注入層102側の絶縁層150が露出するように半導体用基板100を除去する。これにより、導電層パターン120は、半導体パターン104の埋め込み配線として利用することができる。

(もっと読む)

パワー絶縁ゲート型電界効果トランジスタ

【課題】酸化物半導体を用いたパワーMISFETを提供する。

【解決手段】半導体層101を挟んでゲート電極102aとソース電極103a、ドレイン電極103bを形成し、半導体層のうちゲート電極102aとドレイン電極103bとの間にこれらが重ならない領域を設ける。この領域の長さを0.5μm乃至5μmとする。このようなパワーMISFETのドレイン電極とソース電極の間に100V以上の電源と負荷を直列に接続し、ゲート電極102aに制御用の信号を入力して使用する。

(もっと読む)

半導体装置

【課題】コンタクトホールの位置合わせが容易で、コンタクト抵抗の低いフィン型の電界効果型トランジスタを有する半導体装置に提供する。

【解決手段】フィン型の電界効果型トランジスタであって、ソース/ドレイン領域503の少なくともその幅が最も大きい部分では半導体領域502の幅よりも大きく、かつソース/ドレイン領域503の最上部側から基体側に向かって連続的に幅が大きくなっている傾斜部510を有し、該傾斜部表面にシリサイド膜504が形成されていることを特徴とする半導体装置とする。

(もっと読む)

埋め込みゲートを有する半導体装置及びその製造方法

【課題】埋め込みゲートトランジスタのSCEに対する免疫性を向上させると同時に、分岐点での重なりを増加させる方法及び構造の提供。

【解決手段】基板102は第1活性領域104と第2活性領域106とを有し、浅溝分離(STI)領域108によって分離される。バッファ層112は応力緩和層として機能しハードマスク層114が形成される。基板102の表面に分離領域108を部分的に網羅するように凹部118を設ける。ゲート誘電体120が凹部118に形成された後第一ドーパントインプラント122により、ドープ済みチャンネル領域124が形成される。インプラントはハードマスク114を貫通しないので、凹部118の下に形成されたドープ済みチャンネル領域124中のドーパント濃度は最も高くなる。ドープ済みチャンネル領域124はトランジスタのオン・オフを切り替える閾値電圧を変調する。

(もっと読む)

コアシェル半導体微粒子

【課題】塗布等の湿式プロセスによる半導体デバイスの製造において用いることができ、良好な電気特性を有し、安価に製造することができるコアシェル型微粒子を提供する。

【解決手段】コア粒子と、前記コア粒子の表面の少なくとも一部を覆うシェルからなり、前記コア粒子は、バンドギャップが3eV以上である少なくとも1種の金属酸化物(A)からなり、前記シェルは、少なくとも1種の金属酸化物(B)からなる0.01〜1μmのコアシェル型粒子。

(もっと読む)

表示装置

【課題】画素電極上に金属膜を形成して積層構造とする際に、1つのレジストマスクを用

いて、画素電極及び金属膜を形成することを課題とする。

【解決手段】画素電極となる導電膜と金属膜を積層させる。金属膜上に半透部を有する露

光マスクを用いて、膜厚の厚い領域と該領域よりも膜厚が薄い領域とを有するレジストパ

ターンを形成する。レジストパターンを用いて画素電極と、画素電極上の一部に接する金

属膜を形成する。以上により、1つのレジストマスクを用いて、画素電極及び金属膜を形

成することが可能となる。

(もっと読む)

縮合芳香族化合物、有機半導体材料及び有機トランジスタ

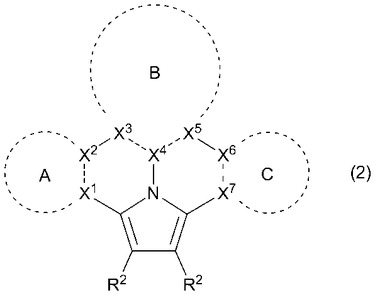

【課題】再配向エネルギーが十分に小さい有機化合物の提供。

【解決手段】式

[式中、A環、B環及びC環は、各々独立して、芳香環を表す。X1、X2、X3、X4、X5、X6及びX7は、各々独立して、炭素原子又は窒素原子を表す。]で表される縮合芳香族化合物、又は式(2)で表される縮合芳香族化合物から水素原子を2個除いた2価の基を繰り返し単位として有する高分子化合物。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、書き込みワード線に電気的に接続する容量素子またはノイズ除去回路を設けることで、駆動回路等からメモリセルに入力されうる制御信号とは異なる短パルスやノイズ等の信号を低減または除去することができる。これにより、メモリセルが有するトランジスタが瞬間的にオンすることでメモリセルに書き込まれたデータが消失してしまう誤動作を防ぐことが可能である。

(もっと読む)

半導体記憶装置

【課題】メモリデータを外部回路を用いずに、コピーを行う半導体記憶装置を提供することを課題とする。

【解決手段】複数のメモリセルの第一端子が共通接続されたビット線と、ビット線に接続され、読み出し時にビット線を特定の電位にプリチャージするプリチャージ回路と、メモリセルから読み出したデータ、もしくはメモリセルへの書き込みデータを一時的に保持する容量素子を有するデータ保持回路と、データ保持回路で保持しているデータの反転データをビット線に出力する反転データ出力回路とを有し、反転データ出力回路は、データ保持回路で保持しているデータの反転データの出力を制御する手段を有する構成とする。

(もっと読む)

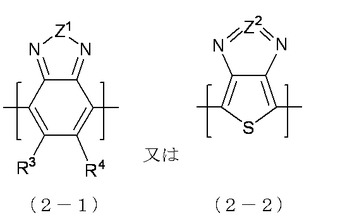

高分子化合物、有機半導体材料及び有機トランジスタ

【課題】有機トランジスタの活性層(有機半導体層)に用いた場合に、有機トランジスタの電界効果移動度が高くなる高分子化合物を提供する。

【解決手段】下記式(1)

(1)で表される構造単位と、下記式で表される構造単位とを含む高分子化合物。 (もっと読む)

(もっと読む)

半導体装置

【課題】本発明は、SOIにおいて適したゲッタリング方法を適用して得られる半導体装置を提供する。

【解決手段】埋め込み酸化膜と、埋め込み酸化膜上に表面シリコン層を有するSOI構造を有する半導体装置において、埋め込み酸化膜上に、表面シリコン層を活性層として有するトランジスタと、素子分離絶縁膜を有し、素子分離絶縁膜上に容量が形成されており、素子分離絶縁膜に希ガス元素又は金属元素が含まれていることを特徴とする半導体装置とする。

(もっと読む)

記憶装置、半導体装置

【課題】長い期間においてデータの保持が可能な記憶装置を提供する。

【解決手段】記憶素子と、上記記憶素子における電荷の供給、保持、放出を制御するためのスイッチング素子として機能するトランジスタとを有する。上記トランジスタは、通常のゲート電極の他に、閾値電圧を制御するための第2のゲート電極が備えられており、また、活性層に酸化物半導体を含むためにオフ電流が極めて低い。上記記憶装置では、絶縁膜に囲まれたフローティングゲートに高電圧で電荷を注入するのではなく、オフ電流の極めて低いトランジスタを介して記憶素子の電荷量を制御することで、データの記憶を行う。

(もっと読む)

201 - 220 / 2,062

[ Back to top ]