Fターム[5F110FF23]の内容

Fターム[5F110FF23]に分類される特許

161 - 180 / 2,062

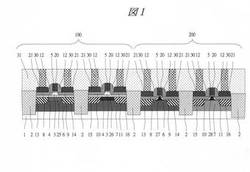

半導体装置

【課題】低電圧領域として使用されるSOI型MISFETと、高電圧領域として使用されるバルク型MISFETとが共存する半導体装置であっても半導体装置全体を縮小でき、更にプロセスが複雑化することなく作製できる半導体装置と製造方法を提供する。

【解決手段】単結晶半導体基板1、単結晶半導体基板から薄い埋め込み絶縁膜4で分離された薄い単結晶半導体薄膜(SOI層)3を持つSOI基板を用い、SOI型MISFET100およびバルク型MISFET200のウエル拡散層領域6と、ドレイン領域9、11、14、16と、ゲート絶縁膜5と、ゲート電極20とを同一工程にて形成する。バルク型MISFETとSOI型MISFETとを同一基板上に形成できるので、基板の占有面積を縮小できる。SOI型MISFETとバルク型MISFETとの作製工程の共通化により簡易プロセスを実現することができる。

(もっと読む)

半導体装置

【課題】酸化物半導体膜を用いたトランジスタに安定した電気特性を付与し、信頼性の高い半導体装置を作製する。

【解決手段】n型酸化物半導体膜中にp型酸化物半導体材料を含ませることで酸化物半導体膜中に意図せずに生じるキャリアを低減することができる。これは、n型酸化物半導体膜中の意図せずに生じた電子が、p型酸化物半導体材料中に生じたホールと再結合することにより、消滅するためである。従って、酸化物半導体膜中に意図せずに生じるキャリアを低減することができる。

(もっと読む)

半導体装置

【課題】トンネルトランジスタにおいて、その寄生容量を低減したゲート電極を提供する。

【解決手段】ゲート絶縁膜201を介して形成されたゲート電極202を挟むように形成された、第1導電型のソース領域121及び前記第1導電型とは逆導電型の第2導電型のドレイン領域122と、基板101内において前記ソース領域121と前記ドレイン領域122との間に形成された、第2導電型のチャネル領域123とを備える。そして、前記ゲート絶縁膜201は、前記ソース領域上に位置し、チャネル幅方向に平行な第1のエッジE1と、前記チャネル領域上又は前記ソース領域上に位置し、チャネル幅方向に平行な第2のエッジE2とを有し、第1の膜厚を有する第1の絶縁膜部分を有する。さらに、前記ゲート絶縁膜201は、前記第1の絶縁膜部分に対して前記ドレイン領域側に位置し、前記第1の膜厚よりも厚い第2の膜厚を有する第2の絶縁膜部分を有する。

(もっと読む)

半導体装置の製造方法

【課題】低電圧領域として使用されるSOI型MISFETと、高電圧領域として使用されるバルク型MISFETとが共存する半導体装置であっても半導体装置全体を縮小でき、更にプロセスが複雑化することなく作製できる半導体装置と製造方法を提供する。

【解決手段】単結晶半導体基板1、単結晶半導体基板から薄い埋め込み絶縁膜4で分離された薄い単結晶半導体薄膜(SOI層)3を持つSOI基板を用い、SOI型MISFET100およびバルク型MISFET200のウエル拡散層領域6と、ドレイン領域9、11、14、16と、ゲート絶縁膜5と、ゲート電極20とを同一工程にて形成する。バルク型MISFETとSOI型MISFETとを同一基板上に形成できるので、基板の占有面積を縮小できる。SOI型MISFETとバルク型MISFETとの作製工程の共通化により簡易プロセスを実現することができる。

(もっと読む)

有機電子デバイス用組成物、有機電子デバイスの作製方法、有機電子デバイス及び電界効果トランジスタ

【課題】 電荷輸送性や移動度が高く、安定性に優れた有機半導体層、及びOn/Off比が高い有機電子デバイスを得ること。また、この有機電子デバイスを低コストに製造すること。

【解決手段】 特定構造の有機半導体材料と特定の有機化合物とを含有する有機電子デバイス用組成物を用いる。具体的には、アヌレン構造を有する有機化合物、及び芳香環基とアルキル基がエステル結合、カルボン酸アミド結合、カルボニル結合又はフェニルエステル結合している有機化合物を含有することを特徴とする有機電子デバイス用組成物を用いる。

(もっと読む)

一時記憶回路、記憶装置、信号処理回路

【課題】トランジスタの数を少なくした構成の記憶素子を用いた一時記憶回路を提供する。

【解決手段】一時記憶回路は複数の記憶素子を有し、複数の記憶素子それぞれは、第1のトランジスタと、第2のトランジスタとを有し、第1のトランジスタはチャネルが酸化物半導体層に形成され、ゲートに入力される制御信号によってオン状態を選択された第1のトランジスタを介して、データに対応する信号電位を第2のトランジスタのゲートに入力し、ゲートに入力される制御信号によって第1のトランジスタをオフ状態とすることによって、第2のトランジスタのゲートに当該信号電位を保持し、第2のトランジスタのソース及びドレインの一方を第1の電位としたとき、第2のトランジスタのソースとドレイン間の状態を検出することによってデータを読み出す。

(もっと読む)

半導体装置

【課題】バンド間トンネリングが横方向に起こる構造を有し、バンド間トンネリングが起こる領域が大きいトンネルトランジスタを備える半導体装置を提供する。

【解決手段】第1上面S1と、第1上面S1よりも高さの低い第2上面S2と、第1上面と第2上面との間に存在する段差側面S3と、を有する段差が形成された基板。さらに、基板の段差側面S3と第2上面S2とに連続して形成されたゲート絶縁膜と、基板の段差側面S3に形成されたゲート絶縁膜に接するよう、第2上面S2上にゲート絶縁膜131を介して形成されたゲート電極132とを備える。さらに、基板内において、第1上面の下方に形成された第1導電型のソース領域121と、第2上面の下方に形成された第2導電型のドレイン領域122と、段差側面S3とソース領域122との間に形成された第2導電型の側方拡散領域123とを備える。

(もっと読む)

配線又は電極の形成方法、電子デバイス及びその製造方法

【課題】下地にダメージを与えず、また、電極材料のゴミの再付着も防止される配線又は電極の形成方法と、この配線又は電極の形成方法により配線又は電極を形成する電子デバイス及びその製造方法を提供する。

【解決手段】下地2上に第1のレジスト層1を形成し、開口部5を形成し、導電材料層3を成膜する。導電材料層3の全体を覆う第2のレジスト層4を形成し、該開口部5以外の導電材料層3上の第2のレジスト層4を除去することにより、該開口部5の導電材料層3を覆う保護レジスト層4’を形成する。該保護レジスト層4’で覆われていない導電材料層3を除去し、次いで保護レジスト層1,4’を除去することにより、残留した導電材料3よりなる配線又は電極を形成する。

(もっと読む)

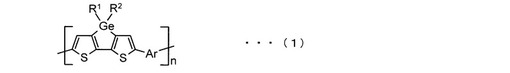

ジチエノゲルモール重合体及びそれを含有した有機半導体デバイス

【課題】耐久性及び半導体特性の安定性に優れた有機半導体材料として有用である熱安定性の高いジチエノゲルモール重合体、及びそれを含有する有機半導体材料より形成される有機半導体デバイスを提供する。

【解決手段】ジチエノゲルモール重合体は、下記化学式(1)

【化1】

(式中、R1及びR2はそれぞれ独立して置換基を有してもよい炭素数1〜20の炭化水素基であり、Arは置換基を有してもよい2価の芳香環と、芳香環数2〜7の置換基を有してもよい2価の多核芳香環と、置換基を有してもよい2価の芳香環及び/又は芳香環数2〜7の置換基を有してもよい2価の多核芳香環を複数連結させた2価のアリーレン基とから選ばれる何れかであり、nは少なくとも2の正数)で示されるものである。有機半導体デバイスは、このジチエノゲルモール重合体を有機半導体層とするものである。

(もっと読む)

半導体装置の駆動方法

【課題】新たな構造の半導体装置、及びその駆動方法を提供することを目的の一とする。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ、該トランジスタと異なる半導体材料を用いた読み出し用のpチャネル型トランジスタ及び容量素子を含む不揮発性のメモリセルを有する半導体装置を提供する。メモリセルへの書き込みは、書き込み用トランジスタをオン状態として、書き込み用トランジスタのソース電極と、容量素子の電極の一方と、読み出し用トランジスタのゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタをオフ状態として、ノードに所定量の電荷を保持させることで行う。また、保持期間において、メモリセルを選択状態とし、且つ、読み出し用トランジスタのソース電極およびドレイン電極を同電位とすることで、ノードに蓄積された電荷を保持する。

(もっと読む)

半導体記憶装置

【課題】さらなるDRAMの大記憶容量化を図る。

【解決手段】半導体記憶装置が、単結晶半導体材料を含む基板の一部を有する駆動回路と、当該駆動回路上に設けられる多層配線層と、当該多層配線層上に設けられるメモリセルアレイ層とを有する。すなわち、当該半導体記憶装置においては、駆動回路と、メモリセルアレイとが重畳して設けられる。したがって、単結晶半導体材料を含む基板に駆動回路及びメモリセルアレイを同一平面に設ける場合と比較して、当該半導体記憶装置の集積度を高めることが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極とボディ領域とを接続したトランジスタを有する半導体装置に関し、動作速度を向上し消費電力を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】第1の素子分離絶縁膜と、第1の素子分離絶縁膜により画定され、第1の素子分離絶縁膜よりも浅いウェルと、ウェル内に形成され、ウェルよりも浅く、ウェルの第1の部分とウェルの第2の部分とを画定する第2の素子分離絶縁膜と、第1の部分上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、第2の部分においてウェルに電気的に接続され、ゲート電極とウェルとを電気的に接続する配線層とを有し、第2の素子分離絶縁膜下の領域のウェルの電気抵抗が、ウェルの他の領域の同じ深さにおける電気抵抗よりも低くなっている。

(もっと読む)

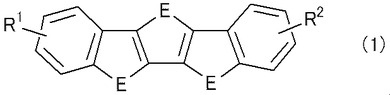

置換ベンゾカルコゲノアセン化合物

【課題】有機半導体活性層の薄膜を与え得る新規な化合物が求められている。

【解決手段】式(1)

(式中、Eはそれぞれ独立に、硫黄またはセレン原子を表す。

R1及びR2は、それぞれ独立に、水素原子、分岐状のアルキル基を有するアリール基、又は、分岐状のアルキル基を有するヘテロアリール基を表す。前記の分岐状のアルキル基を有するアリール基の合計炭素数は9〜30であり、前記の分岐状のアルキル基を有するアリール基は、置換基を有していてもよい。前記の分岐状のアルキル基を有するヘテロアリール基の合計炭素数は7〜30であり、前記の分岐状のアルキル基を有するヘテロアリール基は、置換基を有していてもよい。

R1及びR2の少なくとも一方は、前記の分岐状のアルキル基を有するアリール基、又は、前記の分岐状のアルキル基を有するヘテロアリール基である。)

で表される置換ベンゾカルコゲノアセン化合物。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】基板上に第1の酸化絶縁膜を形成し、該第1の酸化絶縁膜上に第1の酸化物半導体膜を形成した後、加熱処理を行い、第1の酸化物半導体膜に含まれる水素を脱離させつつ、第1の酸化絶縁膜に含まれる酸素の一部を第1の酸化物半導体膜に拡散させ、水素濃度及び酸素欠陥を低減させた第2の酸化物半導体膜を形成する。次に、第2の酸化物半導体膜を選択的にエッチングして、第3の酸化物半導体膜を形成した後、第2の酸化絶縁膜を形成して、当該第2の酸化絶縁膜を選択的にエッチングして、第3の酸化物半導体膜の端部を覆う保護膜を形成する。この後、第3の酸化物半導体膜及び保護膜上に一対の電極、ゲート絶縁膜、及びゲート電極を形成する。

(もっと読む)

SOI基板の作製方法

【課題】照射された水素イオンの単結晶半導体基板からの脱離を抑制する。

【解決手段】半導体基板中に炭素イオンを照射し、当該炭素イオンが照射された半導体基板中に、水素イオンを照射することにより、当該半導体基板中に脆化領域を形成し、当該半導体基板の表面及びベース基板の表面を対向させ、接触させることにより、当該半導体基板及び当該ベース基板を貼り合わせ、貼り合わせた当該半導体基板及び当該ベース基板を加熱し、当該脆化領域において分離させることにより、当該ベース基板上に半導体層を形成するSOI基板の作製に関する。

(もっと読む)

電界効果型トランジスタ、表示素子、画像表示装置、及びシステム

【課題】新規なp型酸化物半導体を活性層に用いた電界効果型トランジスタなどの提供。

【解決手段】ゲート電圧を印加するためのゲート電極と、電流を取り出すためのソース電極及びドレイン電極と、前記ソース電極及び前記ドレイン電極との間に形成されたp型酸化物半導体からなる活性層と、前記ゲート電極と前記活性層との間に形成されたゲート絶縁層とを有し、前記p型酸化物半導体が、一般式ABO3(Aは、Sr及びBaの少なくともいずれかを含む。Bは少なくともBiを含む。)で表され、かつ擬ペロブスカイト構造である電界効果型トランジスタである。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタのスイッチング速度を高速化した半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、絶縁層の一部上に形成された半導体層10と、半導体層10の側面10aに形成され、第1のゲート絶縁膜21、第1のゲート電極22、並びにソース及びドレインとなる2つの第1の不純物層23,24を有する第1のトランジスタ20と、半導体層10の側面10bに形成され、第2のゲート絶縁膜31、第2のゲート電極32、並びにソース及びドレインとなる2つの第2の不純物層33,34を有する第2のトランジスタ30とを具備する。

(もっと読む)

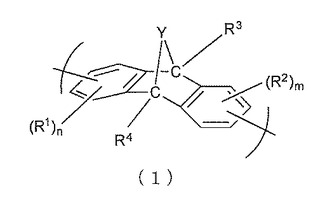

有機トランジスタの製造方法

【課題】電界効果移動度が高い有機トランジスタを製造する方法を提供すること。

【解決手段】式

[式中、R1及びR2は、それぞれ独立に、置換基を表す。R3及びR4は、それぞれ独立に、水素原子又は置換基を表す。n及びmは、それぞれ独立に、0〜3の整数を表す。Yは、2価の基を表す。R1が複数個ある場合、及びR2が複数個ある場合、それらは同一でも相異なってもよい。]で表される構造単位を含む化合物を含有する有機膜を形成する工程と、Yで表される2価の基の少なくとも一部を脱離させて、有機半導体層を製造する工程とを、有する、ゲート電極、ソース電極、ドレイン電極及び有機半導体層を有する有機トランジスタの製造方法。

(もっと読む)

半導体装置

【課題】半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させる。

【解決手段】半導体装置は、半導体基板に設けられた第1のトランジスタと、第1のトランジスタ上に設けられた第2のトランジスタとを有する。また、第2のトランジスタの半導体層は、半導体層の上側で配線と接し、下側で第1のトランジスタのゲート電極と接する。このような構造とすることにより、配線及び第1のトランジスタのゲート電極を、第2のトランジスタのソース電極及びドレイン電極として機能させることができる。これにより、半導体装置の占有面積を低減することができる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体膜をチャネル形成領域に用いたトランジスタにおいて、短チャネル効果による電気特性の変動を抑制し、微細化した半導体装置を提供する。また、オン電流を向上させた半導体装置を提供する。

【解決手段】非晶質領域である一対の第2の酸化物半導体領域と、一対の第2の酸化物半導体領域に挟まれた第1の酸化物半導体領域と、を有する酸化物半導体膜と、ゲート絶縁膜と、ゲート絶縁膜を介して第1の酸化物半導体領域上に設けられるゲート電極と、を有する半導体装置において、第2の酸化物半導体領域には、窒素、リン、又は砒素など15族元素のいずれか一以上の元素が添加されている。

(もっと読む)

161 - 180 / 2,062

[ Back to top ]