Fターム[5F110FF23]の内容

Fターム[5F110FF23]に分類される特許

101 - 120 / 2,062

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】下地絶縁膜上に形成される酸化物半導体膜と、当該酸化物半導体膜とゲート絶縁膜を介して重畳するゲート電極と、酸化物半導体膜に接し、ソース電極及びドレイン電極として機能する一対の電極とを備えるトランジスタであり、下地絶縁膜は、酸化物半導体膜と一部接する第1の酸化絶縁膜と、当該第1の酸化絶縁膜の周囲に設けられる第2の酸化絶縁膜とを有し、トランジスタのチャネル幅方向と交差する酸化物半導体膜の端部は、第2の酸化絶縁膜上に位置するものである。

(もっと読む)

半導体装置およびその製造方法

【課題】シリコンエピタキシャル層の支えの喪失を防止した、局所SOI構造の形成方法の提供。

【解決手段】SiGe混晶層31SG1〜31SG4とシリコンエピタキシャル層31ES1,31ES2,31ES3および31ES4が積層された構造において、

それぞれ、Nウェル31NW及びPウェル31PWがSiGe混晶層31SG1〜31SG4側に突き出る構造を形成し、SiGe混晶層31SG1〜31SG4をエッチングにより除去する際に、支えとなるようにする。

(もっと読む)

半導体装置およびその製造方法

【課題】第1のトランジスタと第2のトランジスタが、ぞれぞれのドレイン領域とソース領域を共有して同一の半導体基板上に形成される構成の半導体装置の製造において、それぞれのトランジスタのソース領域およびドレイン領域の直下に埋め込み絶縁膜を効率的に形成できる製造方法を提供する。

【解決手段】半導体基板上にそれぞれのトランジスタのソース領域およびドレイン領域に対応してトレンチを形成し、前記トレンチをSiGe混晶層と半導体層を順次形成することにより充填し、さらに第1のトランジスタのソース領域および第2のトランジスタのドレイン領域直下のSiGe混晶層を、素子分離溝を介して選択エッチングにより除去し、第1のトランジスタのドレイン領域および第2のトランジスタのソース領域として共有される拡散領域直下のSiGe混晶層を、前記拡散領域に形成した孔を介して選択エッチングし、除去する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。または

、良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】絶縁層と、絶縁層中に埋め込まれたソース電極、およびドレイン電極と、絶

縁層表面、ソース電極表面、およびドレイン電極表面、の一部と接する酸化物半導体層と

、酸化物半導体層を覆うゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有し、絶縁

層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根(RMS)

粗さが1nm以下であり、絶縁層表面の一部とソース電極表面との高低差、および絶縁層

表面の一部とドレイン電極表面との高低差は、5nm以上の半導体装置である。

(もっと読む)

半導体組成物

【課題】高い電界効果移動度、良好なフィルム形成特性、および複合システムにおける高性能のための適切な形態を示す半導体組成物を提供する。

【解決手段】ボトムゲート型のボトムコンタクト型TFT10は、ゲート電極18およびゲート誘電体層14と接触した基板16を含む。ゲート電極18は、ここでは基板16の頂上に記載されているが、ゲート電極は基板内のくぼみとして位置することもできる。ゲート誘電体層14は、ゲート電極18とソース電極20、ドレイン電極22、および半導体層12とを分離することが重要である。半導体組成物から形成される半導体層12は、ソース電極20とドレイン電極22との間に延びる。この半導体組成物は、ポリマー結合剤および小分子半導体を含む。半導体層中の小分子半導体は、100ナノメートル未満の結晶サイズを有する。組成物から形成されたデバイスは、高い移動度および優れた安定性を示す。

(もっと読む)

有機導電デバイスの製造方法および有機導電デバイス

【課題】 螺旋状ポリアセチレンを用いた、導電チャンネルとなる導電路を安定して形成できる有機導電デバイスの製造方法を提供する。

【解決手段】 螺旋状ポリアセチレン分子と溶媒を含有する溶液を複数の電極間に配置する工程と、前記溶液に電界を印加して前記螺旋状ポリアセチレン分子からなる導電路を形成する工程を有する有機導電デバイスの製造方法。前記溶液に電界を印加する方法は、前記溶液を複数の電極間に配置した後、前記複数の電極間に電界を印加する方法、または前記複数の電極間に電界を印加した後、前記複数の電極間に前記溶液を配置する方法のいずれかである。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】素子面積の増大を抑制しつつ、駆動電流の高いON/OFF比と安定した特性を実現できる半導体装置及びその製造方法を提供する。

【解決手段】絶縁層と、絶縁層上に形成された半導体層と、半導体層に形成された部分空乏型のトランジスター10とを備え、トランジスター10は、半導体層上に絶縁膜を介して形成されたゲート電極14と、ゲート電極14両側下の半導体層に形成されたソース15又はドレイン16と、ボディーの下部に設けられた不純物層17,18とを有し、不純物層17,18は、ボディー領域の下部の両側端部に形成され、ソース15、ドレイン16とは接しない。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】酸化物半導体膜と接して形成される絶縁膜へのインジウムの拡散を抑え、また、酸化物半導体膜を用いたトランジスタにおいて、酸化物半導体膜と接する絶縁膜との界面特性を良好にし、安定した電気的特性を有し、信頼性の高い半導体装置を提供する。

【解決手段】インジウムを含む酸化物半導体膜において、表面のインジウム濃度を低減させることによって、酸化物半導体膜の上に接して形成される絶縁膜へのインジウムの拡散を防ぐ。また、さらに酸化物半導体膜表面のインジウム濃度を低減させることによって、表面にインジウムを実質的に含まない層を形成することができ、この層を絶縁膜の一部とすることにより、酸化物半導体膜と、該酸化物半導体膜と接する絶縁膜との界面特性を良好にする。

(もっと読む)

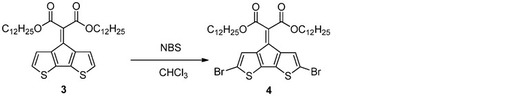

高分子化合物及びそれを用いた有機トランジスタ

【課題】有機トランジスタの活性層の構成材料として優れた電界効果移動度を発揮することができる高分子化合物を提供すること。

【解決手段】下式で表される第1構造単位とチオフェン環、又は、少なくとも1つのチオフェン環を含む縮合環を表し、且つ、前記第1構造単位とは異なる構造を有する第2構造単位とを含む高分子化合物。 (もっと読む)

(もっと読む)

半導体装置及びその作製方法

【課題】多層配線を形成する際における配線の加工に要する工程を簡便にすることを課題

とする。また、開口径の比較的大きいコンタクトホールに液滴吐出技術やナノインプリン

ト技術を用いた場合、開口の形状に沿った配線となり、開口の部分は他の箇所より凹む形

状となりやすかった。

【解決手段】高強度、且つ、繰り返し周波数の高いパルスのレーザ光を透光性を有する絶

縁膜に照射して貫通した開口を形成する。大きな接触面積を有する1つの開口を形成する

のではなく、微小な接触面積を有する開口を複数設け、部分的な凹みを低減して配線の太

さを均一にし、且つ、接触抵抗も確保する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】歩留まりに優れた半導体装置を提供する。

【解決手段】ゲート電極140は素子形成領域104に形成されている。サイドウォール層160は、ゲート電極140の側壁を覆っている。拡散領域170は素子形成領域104に位置する基板100に形成され、トランジスタ110のソース及びドレインとなる。絶縁層200は、素子形成領域104上、及びゲート電極140上に形成されている。コンタクト210は絶縁層200に形成され、拡散領域170に接続している。ゲート電極140のうちコンタクト210と隣に位置する部分は、サイドウォール層160より低く形成されている。絶縁層200は、ゲート電極140のうちコンタクト210と隣に位置する部分上かつ、サイドウォール層160同士の間に形成されている間隙に埋設される。

(もっと読む)

表示装置、液晶表示装置及びプロジェクター

【課題】高開口率な半導体装置を提供する。

【解決手段】絶縁表面上に第1配線と、第1配線上に第1絶縁膜と、第1絶縁膜上に半導体膜と、半導体膜上に第2絶縁膜と、第2絶縁膜上に第2配線と、第1配線と接続するゲート電極と、第2配線及びゲート電極上に第3絶縁膜と、第3絶縁膜上に半導体膜と接続する第3の配線とを有する半導体装置。

(もっと読む)

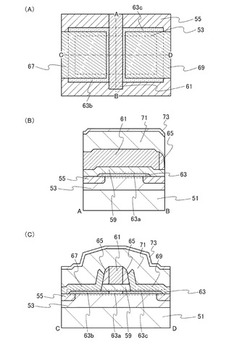

ワイヤチャンネルを有する電界効果トランジスタ及びその製造方法

【課題】ワイヤチャンネルを有する電界効果トランジスタ及びその製造方法を提供する。

【解決手段】半導体基板100と、半導体基板100上に形成されたソース/ドレイン

領域142と、ソース/ドレイン領域142と電気的に連結され、2列及び少なくとも2

行で配列された複数個のワイヤチャンネル112e、114eと、複数個のワイヤチャン

ネル112e、114eをそれぞれ取り囲むゲート絶縁膜142aと、それぞれの複数個

のワイヤチャンネル112e、114e及びゲート絶縁膜142aを取り囲むゲート電極

と、を備える。

(もっと読む)

配線構造、表示装置、および半導体装置

【課題】Cu合金層と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに半導体層との密着性に優れており、且つ電気抵抗率が低減された配線構造を提供すること。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記Cu合金層は、基板側から順に、合金成分としてMnと、X(Xは、Ag、Au、C、W、Ca、Mg、Al、SnおよびNiよりなる群から選択される少なくとも一種)を含有する第一層と、純Cu、またはCuを主成分とするCu合金であって前記第一層よりも電気抵抗率の低いCu合金からなる第二層、とを含む積層構造である。

(もっと読む)

スパッタリングターゲット、酸化物半導体薄膜及びそれらの製造方法

【課題】スパッタリング法を用いて酸化物半導体膜を成膜する際に発生する異常放電を抑制し、酸化物半導体膜を安定かつ再現性よく得ることができるスパッタリングターゲットを提供する。

【解決手段】In、Ga、及びAlの割合が下記式(1)及び(2)の原子比となるように原料化合物を混合後、成形体とする工程、及び、前記成形体を、800℃から焼結温度までの温度範囲を0.1℃/分〜2℃/分の昇温速度で昇温した後、1450℃〜1650℃に10〜50時間保持することにより焼結する工程を含むことを特徴とする焼結体の製造方法。

Ga/(In+Ga+Al)=0.01〜0.08 (1)

Al/(In+Ga+Al)=0.0001〜0.03 (2)

(もっと読む)

半導体装置

【課題】安定したボディ固定動作と共に、高集積化、低寄生容量化や配線容量の低減化を図ることができる、SOI基板上に形成される半導体装置を得る。

【解決手段】ソース領域1,ドレイン領域2及びゲート電極3で形成されるMOSトランジスタにおいて、ゲート一端領域及びゲート他端領域に部分分離領域11a及び11bが形成され、部分分離領域11aに隣接してタップ領域21aが形成され、部分分離領域11bに隣接してタップ領域21bが形成される。部分分離領域11a,11b、タップ領域21a,21b及び活性領域1,2の周辺領域は全て完全分離領域10が形成される。

(もっと読む)

フィン型電界効果トランジスタ

【課題】フィン型電界効果トランジスタはその動作原理から、低消費電力化を図るためには、動作時のバルク領域は完全空乏化される必要があった。結果として、プロセスばらつきがバルク領域のばらつきを生み、消費電力にばらつきを与えるという問題が生じていた。

【解決手段】本発明のフィン型電界効果トランジスタは、ゲート絶縁膜を介してチャネル領域に電界を印加するためのゲート電極を備えるフィン型電界効果トランジスタにおいて、バルク領域に所定の電位を印加するためのバルク電極を、ゲート電極と別に備えられている。このような構造にすることで、フィンの幅を空乏層程度に保つことを必要せず、基板電位を変化させることでデバイスの特性を変化させる、基板バイアス効果によって消費電力を削減することが可能となる。

(もっと読む)

非晶質酸化物薄膜トランジスタ及びその製造方法、その薄膜トランジスタを含むディスプレイパネル

【課題】本発明の実施例は非晶質酸化物薄膜トランジスタ及びその製造方法、ディスプレイパネルを開示する。

【解決手段】前記非晶質酸化物薄膜トランジスタは、ゲート電極、ゲート絶縁層、半導体活性層、ソース電極及びドレイン電極を含む。前記半導体活性層はチャネル層とオーミック接触層を含み、前記チャネル層は前記オーミック接触層に比べ酸素含有量が高い。また、前記チャネル層は前記ゲート絶縁層と接し、前記オーミック接触層は二つの独立したオーミック接触領域に分けられ、かつ前記二つの独立したオーミック接触領域はそれぞれ前記ソース電極、ドレイン電極と接する。

(もっと読む)

電気光学装置の製造方法

【課題】テトラエトキシシラン等のシラン系有機材料を用いたプラズマCVD法によりシリケートガラスを形成した場合でも、シリケートガラスから半導体層へのフッ素の侵入を防止することのできる電気光学装置の製造方法を提供すること。

【解決手段】液晶装置の製造方法において、ゲート電極3cの形成工程、低濃度不純物導入工程、および高濃度不純物導入工程を行った後、シランガス等のシラン系無機原料を用いたCVD法により第1絶縁膜411を形成する。次に、第1アニール工程において第1絶縁膜411をアニールした後、テトラエトキシシラン等のシラン系有機原料を用いたプラズマCVD法によりシリケートガラスからなる第2絶縁膜412を形成する。

(もっと読む)

三層積層型エラストマースタンプ及びそれを用いた有機薄膜形成方法並びに有機デバイス

【課題】 μCP法やコンタクトキャスト法等のエラストマースタンプを使用した印刷プロセスにおいて、インクに使用される溶剤の多様化と加熱機構を付加することによる生産性の高い薄膜形成プロセス及びその仕様に耐えうるエラストマースタンプを提供する。

【解決手段】 耐溶剤性に優れたフッ素系エラストマーからなる中間層と、該中間層とは異なるエラストマーからなる上層及び下層とから構成された3層構造を有し、前記上層及び下層の少なくとも一方は、インクと接触する層であって、剥離性表面を有するシリコーン系エラストマーからなることを特徴とする3層積層型のエラストマースタンプ。

(もっと読む)

101 - 120 / 2,062

[ Back to top ]