Fターム[5F110FF23]の内容

Fターム[5F110FF23]に分類される特許

81 - 100 / 2,062

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、配線数を削減することによって高集積化が図られた半導体装置を提供することを目的とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、書き込み用のワード線と読み出し用のワード線を共通化し、かつ書き込み用のビット線と読み出し用のビット線を共通化することにより配線数を削減し、更にソース線を削減することにより単位面積あたりの記憶容量を増加させる。

(もっと読む)

記憶回路、電子機器

【課題】新たな構成の不揮発性の記憶回路を提供する。

【解決手段】第1の記憶回路と、第2の記憶回路と、第1のスイッチと、第2のスイッチと、位相反転回路と、を有し、第1の記憶回路は、酸化物半導体膜により形成された第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、容量素子と、を有する。酸化物半導体膜により形成された第1のトランジスタと、容量素子と、を用い不揮発性の記憶回路を構成する。また、記憶回路に接続する電源線、及び信号線を少なくし、当該記憶回路に用いるトランジスタ数を減少させることで、回路規模の小さい不揮発性の記憶回路を実現することができる。

(もっと読む)

半導体装置及びその駆動方法

【課題】消費電力を低減することが可能な新たな構造の半導体装置及びその駆動方法を提供する。

【解決手段】メモリセルは、容量素子と、第1のトランジスタと、第1のトランジスタよりオフ電流の小さな第2のトランジスタとを有する。第1のトランジスタは、第2のトランジスタよりもスイッチング速度が速い。第1のトランジスタと第2のトランジスタと容量素子とは直列に電気的に接続されている。容量素子への電荷の蓄積、及び容量素子からの電荷の放出は、第1のトランジスタと第2のトランジスタの両方を介して行われる。こうして、半導体装置の消費電力を少なく、且つ情報の書き込み及び読み出し速度を高速化することができる。

(もっと読む)

仮想ボディ・コンタクト型トライゲート

【課題】FETデバイスにおける閾値電圧をより良く制御できるデバイスの提供。

【解決手段】基板101と、基板101の上のSiGe層103と、SiGe層上の半導体層105と、基板、SiGe層及び半導体層に隣接した絶縁層109aと、絶縁層に隣接した一対の第1のゲート構造体111と、絶縁層上の第2のゲート構造体113とを含む電界効果トランジスタ(FET)と、FETを形成する方法である。絶縁層は、SiGe層の側面、並びに半導体層の上面、半導体層の下面及び導体層の側面に隣接していることが好ましい。SiGe層は、炭素を含むことが好ましい。一対の第1のゲート構造体が、第2のゲート構造体に対して実質的に横断方向にあることが好ましい。さらに、第1のゲート構造体の対は、絶縁層によりカプセル封入されることが好ましい。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位切り替え回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

記憶装置、及び半導体装置

【課題】高速動作を実現できる記憶装置、或いは、リフレッシュ動作の頻度が低減できる記憶装置を提供する。

【解決手段】セルアレイ101の内部において、メモリセル100に接続された配線に、駆動回路102から電位の供給が行われる。さらに、駆動回路102上にセルアレイ101が設けられており、セルアレイ101が有する複数の各メモリセル100は、スイッチング素子と、スイッチング素子により電荷の供給、保持、放出が制御される容量素子とを有する。そして、スイッチング素子として用いられるトランジスタは、シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体を、チャネル形成領域に含んでいる。

(もっと読む)

電気光学装置の製造方法

【課題】層間絶縁膜のコンタクトホールの内部にコンタクト用導電膜および埋め込み膜を設けた場合でも、コンタクトホールの外部で画素電極とコンタクト用導電膜とを確実に導通させることができる電気光学装置の製造方法を提供すること。

【解決手段】電気光学装置100を製造するにあたって、層間絶縁膜45上にコンタクトホール45aの底部45eおよび内壁45fに重なるコンタクト用導電膜90をITO膜により形成した後、コンタクトホール45aの内部を埋める埋め込み膜48をシリコン酸化膜により形成し、その後、埋め込み膜48に対して反応性イオンエッチングを行い、コンタクト用導電膜90を露出させる。また、コンタクトホール45aの内部には埋め込み膜48を残す。その際、埋め込み膜48とコンタクト用導電膜90とのエッチング選択比を利用して埋め込み膜48を選択的に除去してコンタクト用導電膜90を露出させる。

(もっと読む)

半導体装置

【課題】半導体装置を小型化する。また、メモリセルを有する半導体装置の駆動回路の面積を縮小する。

【解決手段】少なくとも第1の半導体素子を有する素子形成層と、素子形成層上に設けられた第1の配線と、第1の配線上に設けられた層間膜と、層間膜を介して第1の配線と重畳する第2の配線と、を有し、第1の配線と、層間膜と、第2の配線と、は、第2の半導体素子を構成し、第1の配線と、第2の配線と、は、同電位が供給される配線である半導体装置である。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ162、トランジスタ162と異なる半導体材料を用いた読み出し用トランジスタ160及び容量素子164を含む不揮発性のメモリセルにおいて、メモリセルへの書き込みは、書き込み用トランジスタ162をオン状態とすることにより、書き込み用トランジスタ162のソース電極(またはドレイン電極)と、容量素子164の電極の一方と、読み出し用トランジスタ160のゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタ162をオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。また、読み出し用トランジスタ160として、pチャネル型トランジスタを用いて、読み出し電位を正の電位とする。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、容量素子と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、信号線及びワード線に接続された第2のトランジスタと、ワード線、に接続された容量素子とを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方と、容量素子の電極の一方とが接続された、半導体装置。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】新規な非シリコン系半導体薄膜を用いた薄膜トランジスタを提供する。

【解決手段】ガリウムが酸化インジウムに固溶していて、原子比Ga/(Ga+In)が0.001〜0.12であり、全金属原子に対するインジウムとガリウムの含有率が80原子%以上であり、In2O3のビックスバイト構造を有する酸化物薄膜を用いることを特徴とする薄膜トランジスタ。

(もっと読む)

半導体装置およびその駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のチャネル形成領域と、第1のゲート電極と、第1のソース領域およびドレイン領域と、を有する第1のトランジスタと、少なくとも第1のソース領域またはドレイン領域の一部と重畳するように設けられた、酸化物半導体材料からなる第2のチャネル形成領域と、第2のソース電極と、第1のゲート電極に電気的に接続される第2のドレイン電極と、第2のゲート電極と、を有する第2のトランジスタと、第1のトランジスタと第2のトランジスタとの間の絶縁層と、を含むメモリセルを有し、第2のトランジスタをオフ状態とすべき期間において、少なくとも第1のソース領域またはドレイン領域に正の電位が与えられるときに第2のゲート電極に負の電位が与えられる半導体装置。

(もっと読む)

半導体装置の製造方法、及び電気光学装置の製造方法

【課題】信頼性の高いLDD構造のTFTを形成することが可能な半導体装置の製造方法、及び電気光学装置の製造方法を提供する。

【解決手段】第1領域155のPMOSTFTと、第2領域156のLDDを備えるNMOSTFTと、第3領域157のLDDを備えるNMOSTFTとを製造する製造方法は、厚みの異なる2種類の多階調レジスト211,212を形成し、多階調レジスト211,212をマスクとして不純物の注入とアッシングとを繰り返し、セルフアラインでLDDを形成する工程を有する。

(もっと読む)

酸化物半導体素子、酸化物半導体素子の製造方法、酸化物半導体素子を含む表示装置、及び酸化物半導体素子を含む表示装置の製造方法

【課題】酸化物半導体素子、酸化物半導体素子の製造方法、酸化物半導体素子を含む表示装置、及び酸化物半導体素子を含む表示装置の製造方法を提供すること。

【解決手段】酸化物半導体素子は、基板上に配置されるゲート電極と、リセス構造を含むゲート絶縁層と、ゲート絶縁層の一側上に配置されるソース電極と、ゲート絶縁層の他側上に配置されるドレーン電極と、ゲート絶縁層、ソース電極、及びドレーン電極上に配置されるアクティブパターンとを含むようにすることができる。リセス構造はゲート電極の上部に位置するようにすることができ、アクティブパターンはリセス構造を埋め立てるようにすることができる。酸化物半導体素子がリセス構造を有するゲート絶縁層を具備することによって、電荷移動度、閾値電圧分布、動作電流などの多様な電気的特性を向上させることができる。

(もっと読む)

高分子化合物及びそれを用いた有機半導体素子

【課題】高いキャリア移動度を有する高分子化合物を提供すること。

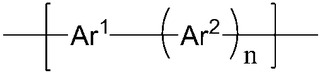

【解決手段】式(1)で表される構造単位を有する高分子化合物であって、

(1)

〔式中、Ar1は、置換基を有していてもよいアリーレン基又は置換基を有していてもよいヘテロアリーレン基を表す。Ar2は、置換基を有していてもよいアリーレン基又は置換基を有していてもよいヘテロアリーレン基を表す。nは、0〜3の整数を表す。Ar2が複数個ある場合、それらは同一であっても相異なってもよい。〕2個の高分子化合物の主鎖間のキャリア伝導性と高分子化合物の主鎖内のキャリア伝導性の両方が大きく、高いキャリア移動度を有する高分子化合物。

(もっと読む)

半導体装置

【課題】短チャネル効果を抑制させつつ微細化を行い、低消費電力化した半導体装置を提供する。

【解決手段】溝部および該溝部を挟んで形成された一対の低抵抗領域を有する半導体基板と、半導体基板上の第1のゲート絶縁膜と、第1のゲート絶縁膜を介し、溝部と重畳するゲート電極と、ゲート電極を覆って設けられた第2のゲート絶縁膜と、第2のゲート絶縁膜上の、溝部を挟んで設けられた一対の電極と、一対の電極と接する半導体膜と、を有し、一対の低抵抗領域の一方と、一対の電極の一方が電気的に接続されている積層されたトランジスタを形成し、一方はn型半導体からなるトランジスタであり、他方はp型半導体からなるトランジスタにより形成させることによって、相補型MOS回路を形成する。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】省電力化かつ高速での書き込み処理が可能なメモリの多値化に適した半導体装置およびベリファイ処理を提供する。

【解決手段】半導体装置に用いるメモリセルを、酸化物半導体を用いたトランジスタと酸化物半導体以外の材料を用いたトランジスタをそれぞれ有する構成とし、書き込み回路を用いてデータバッファのデータをメモリセルに書き込む前に、予め各々のメモリセルの有するしきい値ばらつきを調べ、データバッファのデータに対して当該しきい値ばらつきを補正したデータが各々のメモリセルに書き込む。

(もっと読む)

薄膜トランジスタ

【課題】高移動度の薄膜トランジスタ、その製造方法及びその製造に用いるスパッタリングターゲットを提供する。

【解決手段】元素In,Ga及びZnを下記領域1、2又は3の原子比の範囲で含む酸化物を活性層とし、電界効果移動度が25cm2/Vs以上である薄膜トランジスタ。

領域1

0.58≦In/(In+Ga+Zn)≦0.68

0.15<Ga/(In+Ga+Zn)≦0.29

領域2

0.45≦In/(In+Ga+Zn)<0.58

0.09≦Ga/(In+Ga+Zn)<0.20

領域3

0.45≦In/(In+Ga+Zn)<0.58

0.20≦Ga/(In+Ga+Zn)≦0.27

(もっと読む)

印刷可能半導体素子を製造して組み立てるための方法及びデバイス

【課題】印刷可能半導体素子を製造するとともに、印刷可能半導体素子を基板表面上に組み立てるための方法及びデバイス、及び伸張形態で良好な性能が得られる伸縮可能な半導体構造及び伸縮可能な電子デバイスを提供する。

【解決手段】予め歪みが加えられた拡張状態の弾性基板が与えられる。印刷可能な半導体構造の内面の少なくとも一部を、予め歪みが加えられた拡張状態の弾性基板の外面に対して結合される。半導体構造の内面を湾曲させることにより弾性基板を少なくとも部分的に緩和状態へと弛緩させる。湾曲した内面を有する半導体構造が弾性基板から他の基板、好ましくはフレキシブル基板へと転写される。

(もっと読む)

高分子化合物及びそれを用いた有機光電変換素子

【課題】長波長の光の吸光度が大きい高分子化合物を提供する。

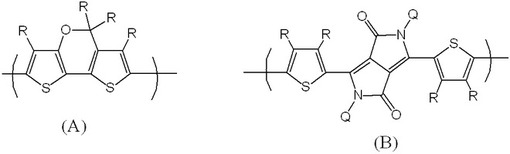

【解決手段】式(A)で表される繰り返し単位と式(B)で表される繰り返し単位とを含む高分子化合物。

〔式(A)及び式(B)中、Q及びRは、同一又は相異なり、水素原子、フッ素原子、フッ素化されていてもよいアルキル基、フッ素化されていてもよいアルコキシ基、アリール基、ヘテロアリール基等で表される基を表す。複数個あるQは、同一でも相異なっていてもよい。複数個あるRは、同一でも相異なっていてもよい。〕

(もっと読む)

81 - 100 / 2,062

[ Back to top ]