Fターム[5F110FF23]の内容

Fターム[5F110FF23]に分類される特許

21 - 40 / 2,062

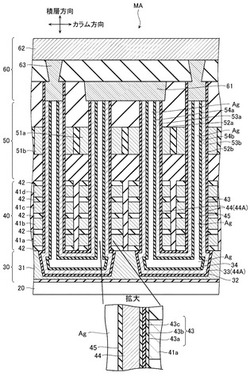

不揮発性半導体記憶装置、及びその製造方法

【課題】チャネル移動度を向上させた不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板20上に設けられたメモリトランジスタ40と選択トランジスタ50を有する。メモリトランジスタ40は、導電層41a〜41d、メモリゲート絶縁層43、柱状半導体層44、及び酸化層45を有する。導電層41は、メモリトランジスタ40のゲートとして機能する。メモリゲート絶縁層43は、導電層の側面に接する。半導体層44は、導電層と共にメモリゲート絶縁層43を一方の側面で挟み、半導体基板20に対して垂直方向に延び、メモリトランジスタ40のボディとして機能する。酸化層45は、半導体層44の他方の側面に接する。半導体層44は、シリコンゲルマニウムにて構成される。酸化層45は、酸化シリコンにて構成される。

(もっと読む)

半導体装置及びその製造方法

【課題】プロセス条件の見直しを最小限に抑制しつつ電気的特性を向上させることができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、半導体構造11の上面領域に形成された島状の絶縁膜20と、絶縁膜20の上面領域に配列された複数の凸状絶縁部23と、これら凸状絶縁部23と絶縁膜20とを被覆する層間絶縁膜26とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチ分離構造の上面の周縁部にディボットが形成されても、このディボットに起因するゲート絶縁膜の破壊を防止することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、トレンチ分離構造20Bと、トレンチ分離構造20Bで区画される活性領域上に形成されたゲート絶縁膜30と、ゲート絶縁膜30の上面からトレンチ分離構造20Bの上面まで延在するゲート電極層31と、ゲート電極層31の両側に形成された第1及び第2の不純物拡散領域13D,13Sとを備える。ゲート電極層31は、ゲート絶縁膜30と第1の不純物拡散領域13Dとの間の領域に貫通孔31hを有し、貫通孔31hは、トレンチ分離構造20Bの上面の周縁部の直上に形成されている。

(もっと読む)

液晶パネル用基板、液晶パネル、電子機器及び投射型表示装置

【課題】半導体を基板とする液晶パネルは、ウェル領域があるため、漏れ光がトランジスタ部分のみでなくそこから離れた半導体基板を通過しただけで光リーク電流が流れることがある。この光リーク電流が、ガラス基板上にスイッチング素子としてのTFTを配置した液晶パネルに比べて多くなるという欠点がある。

【解決手段】反射電極となる画素電極(14)と、画素電極への電圧印加を制御するスイッチング素子とを有する画素単位が基板上にマトリックス状に配置されてなる液晶パネル用基板において、両素電極とスイッチング素子の端子電極を構成する導電層(6a)との間に、両者を接続するためのコンタクトホールを形成し、このコンタクトホールの形成箇所を囲む開口を有し、隣接する複数の画素電極の間の領域には開口を有さない遮光層を、画素電極と導電層との間に設けることにより、画素電極どうしの隙間から漏込む光による弊害を防ぐ。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】チャネル領域にシリコンを含まない材料を用いる半導体装置であって、微細化に伴いゲート絶縁層が薄膜化されても、ゲートリーク電流が抑制された半導体装置を提供する。

【解決手段】ゲート絶縁層として熱酸化シリコン層を用いる。熱酸化シリコン層を用いることで、CVD法やスパッタリング法で形成された酸化シリコン層を用いる場合よりゲートリーク電流を抑制することができる。ゲート絶縁層に熱酸化シリコン層を用いるために、チャネル領域を含む半導体層を形成する基板とは別にシリコン基板を用意し、シリコン基板上に熱酸化シリコン層を形成する。そして熱酸化シリコン層を、チャネル領域を含む半導体層に貼り合わる。このようにして、半導体層の上に熱酸化シリコン層を形成し、熱酸化シリコン層をゲート絶縁層として用いたトランジスタを形成する。

(もっと読む)

半導体装置

【課題】液晶の配向不良を抑制するために画素電極を平坦化し、開口率を下げずに十分な

容量を得られる容量素子を有する半導体装置を実現することを課題とする。

【解決手段】薄膜トランジスタ上の遮光膜、前記遮光膜上の容量絶縁膜、前記容量絶縁膜

上に導電層、前記導電層と電気的に接続するように画素電極を有する半導体装置であり、

前記遮光膜、前記容量絶縁膜および前記導電層から保持容量素子を形成することにより、

容量素子として機能する領域の面積を増やすことができる。

(もっと読む)

有機薄膜トランジスタ

【課題】電界効果移動度が高く、オフ電流が小さい有機薄膜トランジスタを提供することである。

【解決手段】有機半導体層の内部のうち、ソース電極の真上又は真下に位置する部分を第1の部分とし、ドレイン電極の真上又は真下に位置する部分を第2の部分とし、第1の部分と第2の部分とは異なる部分を第3の部分とした場合に、ドーピング領域が、第3の部分、第1の部分と第3の部分、又は第2の部分と第3の部分に存在する有機薄膜トランジスタである。

(もっと読む)

有機電界効果型トランジスタ

【課題】カーボンナノチューブを含有する活性層を有する有機電界効果型トランジスタにおいて、熱プロセス、経時変化、外部環境に対して、移動度、Von、ヒステリシスの性能を安定化すること。

【解決手段】ゲート電極、ゲート絶縁層、カーボンナノチューブを含有する活性層、該活性層に対して前記ゲート絶縁層と反対側に形成された架橋構造を持つポリシロキサンを含む第2絶縁層、ソース電極およびドレイン電極を有する有機電界効果型トランジスタ。

(もっと読む)

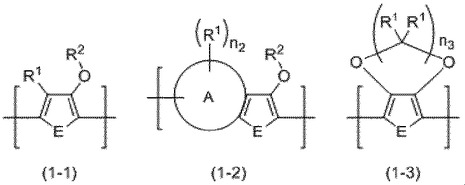

高分子化合物及びそれを用いた有機トランジスタ

【課題】電界効果移動度が高い有機トランジスタ作製に有用な高分子化合物を提供する。

【解決手段】式(1−1)〜式(1−3)で表される構造単位からなる群から選ばれる少なくとも1種の構造単位と、アリーレン基または2価の芳香族複素環基からなる構造単位とを含む高分子化合物とする。

式中、R1は、水素原子、アルキル基、アルコキシ基、アルキルチオ基、アリール基、1価の芳香族複素環基またはハロゲン原子を表す。R2は、炭素数が2以上のアルキル基を表す。Eは、−O−、−S−、−Se−または−N(Ra)−を表す。Raは、水素原子、アルキル基、アリール基または1価の芳香族複素環基を表す。環Aは、芳香環または複素環を表す。n2は0以上の整数を表し、n3は1〜3の整数を表す。]

(もっと読む)

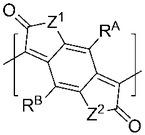

高分子化合物、該高分子化合物を含む薄膜及び組成物

【課題】両極性の有機トランジスタを簡便に製造しうる、p型とn型の両極性を示す高分子化合物を提供すること。

【解決手段】式

【化0】

(1)

〔式中、Z1は、−O−、−S−、−N(R1)−、−N(COR2)−又は−N(CO2R3)−を表す。Z2は、−S−、−N(R1)−、−N(COR2)−又は−N(CO2R3)−を表す。R1、R2及びR3は、それぞれ独立に、水素原子アルキル基、アリール基又はヘテロアリール基を表す。RA及びRBは、それぞれ独立に、水素原子、アルキル基、アルコキシ基、アルキルチオ基、アリール基、ヘテロアリール基、ハロゲン原子又はシアノ基を表す。〕

で表される構成単位を含む高分子化合物。

(もっと読む)

有機半導体単結晶形成方法及び有機半導体デバイス

【課題】基板上の任意の位置に任意の向きの有機半導体単結晶を形成する。

【解決手段】親液性であって、結晶成長の方向を規制する形状(長方形など)を有する領域内に置かれた有機半導体に対して溶媒蒸気アニールを行うことにより、当該領域内に所定の方向に整列した有機半導体単結晶を成長させる。

(もっと読む)

半導体装置

【課題】半導体チップが薄くなっても、応力による特性変化の少ない半導体装置を提供する。

【解決手段】SOI活性層のオリフラ方向の面方位を<100>、半導体支持基板の面方位を<110>とし、SOI活性層にはPチャネルMOSトランジスタ、半導体支持基板にはNチャネルMOSトランジスタを形成することで、NチャネルMOSトランジスタとPチャネルMOSトランジスタのどちらもピエゾ抵抗効果の角度度依存を持たないように配置することが可能となり、結果としてペアトランジスタ間のシフト量がそろい、半導体装置の特性が安定することとなる。

(もっと読む)

半導体装置

【課題】新規な不揮発性のラッチ回路及びそれを用いた半導体装置を提供する。

【解決手段】第1の素子の出力は第2の素子の入力に電気的に接続され、第2の素子の出

力は第2のトランジスタを介して第1の素子の入力に電気的に接続されるループ構造を有

するラッチ回路であって、チャネル形成領域を構成する半導体材料として酸化物半導体を

用いたトランジスタをスイッチング素子として用い、またこのトランジスタのソース電極

又はドレイン電極に電気的に接続された容量を有することで、ラッチ回路のデータを保持

することができる。これにより不揮発性のラッチ回路を構成することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】通電領域表面の周辺の強電界の影響がナノワイヤに及び難くして、ホットキャリアの生成やオフリーク電流を低減する。半導体装置を高性能化する。

【解決手段】基板の表面よりも深い位置に配置され互いに対向する2つの側壁を有する導電膜と、導電膜の2つの側壁の側方に形成され互いに同じ導電型の半導体領域である第1及び第2の通電領域と、導電膜を貫通して2つの半導体領域どうしを接続し第1及び第2の通電領域の導電型とは逆導電型の半導体領域であるナノワイヤと、導電膜と前記ナノワイヤとの境界部に形成された絶縁膜と、を有することを特徴とする半導体装置。

(もっと読む)

電界効果素子

【課題】高移動度、高オン・オフ比の電界効果素子を提供する。

【解決手段】絶縁膜層、前記絶縁膜層上に積層されたチャネル層、及び電極としてゲート電極、ソース電極及びドレイン電極の3つを有する電界効果素子であって、前記チャネル層は表面粗さ0.2nm以上1.3nm以下であり、前記チャネル層はIn,Ga,Sn及びZnから選択される1以上の元素を含有する非晶質酸化物半導体からなる電界効果素子。

(もっと読む)

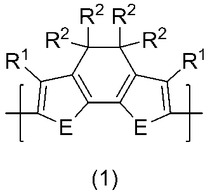

高分子化合物及びそれを用いた有機トランジスタ

【課題】有機トランジスタの活性層に用いた場合に、電界効果移動度が十分に高くなる高分子化合物を提供する。

【解決手段】式

〔式中、Eは、−O−、−S−又は−Se−を表す。R1は、水素原子、アルキル基、アルコキシ基、アルキルチオ基、アリール基、ヘテロアリール基又はハロゲン原子を表す。R2は、水素原子、アルキル基、アリール基、ヘテロアリール基又はハロゲン原子を表すか、2個のR2が連結して環を形成する。〕で表される構造単位と、式(1)で表される構造単位とは異なる式−Ar1−で表される構造単位とを含む高分子化合物である(式中、Ar1は、2価の芳香族基、−CR3=CR3−で表される基又は−C≡C−で表される基を表す)。

(もっと読む)

微結晶シリコン膜形成方法、微結晶シリコン膜成膜装置および表示装置

【課題】微結晶シリコン膜の移動度を高める。

【解決手段】高密度プラズマを用いて少なくとも(220)の結晶方位配列に成長させるように微結晶シリコン膜を形成する第1の工程を有し、第1の工程時、微結晶シリコン膜の結晶方位配列(111)に対する結晶方位配列(220)への成長比率が高くなるように、被処理体近傍の温度を300〜350℃の範囲内に設定し、総流量に対する水素ガスの流量比を高めた成膜ガスを供給する。これにより、ダングリングボンドの少ない微結晶シリコン膜20を形成して、移動度を高めることができる。

(もっと読む)

半導体装置

【課題】不揮発性を有し、書き込み回数に制限のない新たな構造の半導体装置を提供する。

【解決手段】複数の記憶素子が直列に接続され、複数の記憶素子の一は、第1〜第3のゲート電極、第1〜第3のソース電極、および第1〜第3のドレイン電極を有する第1〜第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含んで構成され、第1のゲート電極と、第2のソース電極または第2のドレイン電極の一方とは、電気的に接続され、第1の配線と、第1のソース電極と、第3のソース電極とは、電気的に接続され、第2の配線と、第1のドレイン電極と、第3のドレイン電極とは、電気的に接続され、第3の配線と、第2のソース電極または第2のドレイン電極の他方とは、電気的に接続され、第4の配線と、第2のゲート電極とは、電気的に接続され、第5の配線と、第3のゲート電極とは電気的に接続された半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】仕事関数の異なる複数の電極層を有し、ゲート抵抗が低く、作製が容易なゲート電極を備える半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、基板と、前記基板上に形成されたゲート絶縁膜とを備える。さらに、前記装置は、前記ゲート絶縁膜の上面に形成され、第1の仕事関数を有する第1の電極層と、前記ゲート絶縁膜の上面と前記第1の電極層の上面に連続して形成され、前記第1の仕事関数と異なる第2の仕事関数を有する第2の電極層と、を有するゲート電極と、前記ゲート電極の側面に形成された側壁絶縁膜とを備える。さらに、前記装置では、前記第1の電極層の上面の高さは、前記側壁絶縁膜の上面の高さよりも低い。

(もっと読む)

発光装置

【課題】開口率の向上された発光装置である。

【解決手段】薄膜トランジスタと、容量と、発光素子と、発光素子へ電流を供給することができる機能を有する配線とを、プラスチック基板上に有する発光装置であって、配線は、容量の上に設けられ、容量は、配線の少なくとも一部と重なる領域を有する。発光素子は、陰極と、陽極と、陰極と陽極との間に設けられたEL材料とを有し、容量は、第2の領域と、第2の領域上に第1の絶縁膜を介して設けられる第3の領域とを有する。第1の絶縁膜は、薄膜トランジスタのゲート絶縁膜となり、さらに容量の絶縁膜となることができる。

(もっと読む)

21 - 40 / 2,062

[ Back to top ]