Fターム[5F110FF23]の内容

Fターム[5F110FF23]に分類される特許

141 - 160 / 2,062

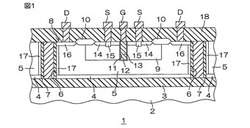

半導体装置

【課題】半導体基板上へのVFETと他の種類の素子との混載が可能でありながら、半導体基板上に積層される半導体層の表面に大きな段差を有しない半導体装置を提供する。

【解決手段】P型シリコン基板2上には、酸化シリコンからなるボックス層3、N+型横方向導電層4およびN−型表面層5が積層されている。ボックス層3上には、N−型表面層5の表面からボックス層3に至る深さを有する、平面視環状のディープトレンチ6が形成されている。ディープトレンチ6およびボックス層3に取り囲まれるトランジスタ形成領域8は、その周囲から分離されている。このトランジスタ形成領域8において、N−型表面層5の表層部には、ソース領域14およびドレイン領域16が形成されている。またディープトレンチ6の側面に沿って、ドレイン領域16とN+型横方向導電層4とに接続されたN+型縦方向導電層17が形成されている。

(もっと読む)

液晶表示装置

【課題】動作性能および信頼性の高い液晶表示装置を提供する。

【解決手段】トランジスタ上に第1の絶縁膜を有し、第1の絶縁膜上に第1及び第2の配線を有し、第1及び第2の配線上に第2の絶縁膜を有し、第2の絶縁膜上に電極を有し、電極上に第3の絶縁膜を有し、第3の絶縁膜上に画素電極を有し、画素電極は、電極と重なる第1の領域と、電極と重ならない第2の領域と、を有し、画素電極は、第1の配線に電気的に接続されており、第1の配線は、トランジスタのソース又はドレインの一方と電気的に接続されており、電極は、画素部の外側において前記第2の配線と電気的に接続されている。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】トランジスタのチャネル部が形成される領域にU字状の縦長溝を形成し、見かけ上のチャネル長に対してチャネル長を長くする方法は、溝を掘るためにフォトリソグラフィ工程を余分に行う必要があり、コストや歩留まりの観点で問題があった。

【解決手段】ゲート電極または絶縁表面を有する構造物を利用し、三次元形状のチャネル領域を形成することにより、チャネル長が、上面から見たチャネル長に対して3倍以上、好ましくは5倍以上、さらに好ましくは10倍以上の長さとする。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置の小型化を実現する。

【解決手段】 第1の絶縁膜上に、島状の半導体層及び前記半導体層を囲む第2の絶縁膜を形成し、前記半導体層の上面と平面的に重なるようにして導電膜からなる抵抗素子(例えばポリシリコン抵抗素子)を配置する。

(もっと読む)

半導体装置

【課題】オン抵抗が低く、かつ、容易に素子分離もできる半導体装置を提供する。

【解決手段】第1絶縁膜2の上の第1導電型の第1半導体層3の表面を含む上部に設けられた第2導電型の第1半導体領域7と、第1半導体領域7の上部に設けられた第1導電型の第2半導体領域8と、側面が第1半導体層3と第1半導体領域7と第2半導体領域8に接する第1トレンチ4と、第1トレンチ4の側面に沿って設けられたゲート絶縁膜5と、第1トレンチ4内に埋め込まれたゲート電極6と、第1半導体領域7と第1トレンチ4から離れて第1半導体層3の上部に設けられた第1導電型の第3半導体領域9と、側面が第3半導体領域9に接し第3半導体領域9に対して第1半導体領域7の反対側に配置された第2トレンチ15と、第2トレンチ15の側面に沿って設けられた素子分離絶縁膜10と、第2トレンチ15内に埋め込まれたポリシリコン埋め込み領域11とを有する。

(もっと読む)

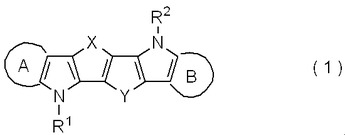

含ピロールヘテロアセン化合物、該化合物の製造方法、該化合物を含む薄膜及び該薄膜を含む有機半導体デバイス

【課題】有機半導体活性層の薄膜を与え得る新規な化合物が求められている。

【解決手段】式(1)

(式中、X及びYは、硫黄原子、酸素原子、セレン原子、テルル原子又はSO2を表す。環構造A及び環構造Bは、芳香族炭化水素環又は芳香族複素環を表す。該芳香族複素環は単一の環構造である。

R1およびR2は、水素原子、炭素数1〜30のアルキル基、炭素数1〜30のアルコキシ基、炭素数2〜30のアルケニル基、炭素数2〜30のアルキニル基、炭素数1〜30のアルキルチオ基、炭素数6〜20のアリール基、炭素数4〜20のヘテロアリール基を表す。)

で表される含ピロールヘテロアセン化合物。

(もっと読む)

半導体装置の作製方法

【課題】本発明は、薄膜トランジスタのソース領域やドレイン領域へのコンタクトを確実

にした半導体装置を提供するものである。

【解決手段】本発明における半導体装置において、半導体層上の絶縁膜およびゲイト電極

上に形成された第1の層間絶縁膜と、前記第1の層間絶縁膜の上に形成された第2の層間

絶縁膜と、前記第2の層間絶縁膜、前記第1の層間絶縁膜、および前記絶縁膜に設けられ

たコンタクトホールとを有する。前記第1の絶縁層の膜厚は、前記積層の絶縁膜の合計膜

厚の1/3以下に形成する。

(もっと読む)

有機電子素子用電極、有機トランジスタ素子、インクジェットインク

【課題】接触抵抗を低減した有機電子素子用電極、及びこれを利用した有機トランジスタ素子を提供することを課題とする。

【解決手段】カーボンナノホーンを含んで構成された有機電子素子用電極、及び当該電極を、ソース電極18、及びドレイン電極20として適用した有機トランジスタ素子。

(もっと読む)

半導体装置

【課題】しきい値を電気的に調整可能な半導体装置を提供する。

【解決手段】半導体装置10では、チャネル領域14は対向する第1、第2の面14a、14bを有している。第1、第2不純物領域15、16が、チャネル領域14の両側に配設されている。第1ゲート電極18は、第1ゲート絶縁膜19を介して第1の面14aに、第1ゲート電圧Vg1が印加されると生じる第1反転層23の一側が第1不純物領域15に接触し、他側が第2不純物領域16から離間するように配設されている。第2ゲート電極20は、第2ゲート絶縁膜21を介して第2の面14bに、第2ゲート電圧Vg2が印加されると生じる第2反転層24の一側が第2不純物領域16に接触し、他側が第1不純物領域15から離間するように配設されている。第1、第2ゲート電圧Vg1、Vg2に応じて、第1、第2反転層23、24が接触し、第1、第2不純物領域15、16間が導通する。

(もっと読む)

液晶表示装置

【課題】動作性能および信頼性の高い液晶表示装置を提供する。

【解決手段】第1のチャネル形成領域713と、第1のソース領域及び第1のドレイン領域と、ゲート絶縁膜と、第1のゲート電極とを備えた第1のTFTと、第2のチャネル形成領域714と、第2のソース領域及び第2のドレイン領域と、ゲート絶縁膜と、第2のゲート電極とを備えた第2のTFTと、第1のTFT及び第2のTFT上に設けられた第1の絶縁膜664と、第1のソース領域及び第1のドレイン領域の一方と接続されたソース配線668と、第1のソース領域及び第1のドレイン領域の他方と接続し、且つ第2のゲート電極に接続された第1のドレイン配線と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の一方に接続された第2のドレイン配線672と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の他方に接続された電流供給線と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ボディ浮遊効果を抑制することが可能な半導体装置及びその製造方法を提供する。

【解決手段】シリコン基板1と、シリコン基板1上に形成された埋め込み絶縁層2と、埋め込み絶縁層2上に形成された半導体層3とを備えるSOI構造の半導体装置であって、半導体層3は、第1導電型のボディ領域4、第2導電型のソース領域5及び第2導電型のドレイン領域6を有し、ソース領域5とドレイン領域6との間のボディ領域4上にゲート酸化膜7を介してゲート電極8が形成され、ソース領域5は、第2導電型のエクステンション層52と、エクステンション層52と側面で接するシリサイド層51を備え、シリサイド層51とボディ領域4との境界部分に生じる空乏層の領域に結晶欠陥領域12が形成されている。

(もっと読む)

二価結合を有する小分子チオフェン化合物を備える装置

【課題】溶液処理可能であり及び/又は周囲環境条件でよい安定性を示す小分子チオフェン化合物を備える装置を提供する。

【解決手段】多くの電極と接触している半導体層を備える電子装置であって、前記半導体層は、少なくとも1個の二価結合、及び、複数のチオフェン単位から成る小分子チオフェン化合物を含む。小分子チオフェン化合物は、化合物が、特定数(平均値でない)のチオフェン単位を持ち、少なくとも約90質量%、又は少なくとも約98質量%の純度を有する。

(もっと読む)

半導体装置の作製方法

【課題】側壁スペーサを形成することなく、且つ、工程数を増やすことなく、自己整合的にLDD領域を少なくとも一つ備えたTFTを提供する。また、同一基板上に、工程数を増やすことなく、様々なTFT、例えば、チャネル形成領域の片側にLDD領域を有するTFTと、チャネル形成領域の両側にLDD領域を有するTFTとを形成する作製方法を提供する。

【解決手段】回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルをゲート電極形成用のフォトリソグラフィ工程に適用して膜厚の厚い領域と、該領域より膜厚の薄い領域を片側側部に有する非対称のレジストパターンを形成し、段差を有するゲート電極を形成し、ゲート電極の膜厚の薄い領域を通過させて前記半導体層に不純物元素を注入して、自己整合的にLDD領域を形成する。

(もっと読む)

プリント不揮発性メモリ

【課題】低コストで高スループットなプリント技術を使用した不揮発性メモリセルを提供する。

【解決手段】同一水平レベルにおいて所定の距離で離間している第1及び第2の半導体アイランドであって、第1の半導体アイランド2が制御ゲートを構成し、第2の半導体アイランド3がソース端子及びドレイン端子を構成する、当該第1及び第2の半導体アイランドと、第1の半導体アイランド2の少なくとも一部の上のゲート誘電体層4と、第2半導体アイランドの少なくとも一部の上のトンネリング誘電体層5と、ゲート誘電体層4とトンネリング誘電体層5の少なくとも一部の上のフローティングゲート7と、制御ゲート2並びにソース端子及びドレイン端子に電気的に接触する金属層と、を備える。一つの効果的な実施形態では、不揮発性メモリセルを、「全プリント」加工技術を使用して製造することができる。

(もっと読む)

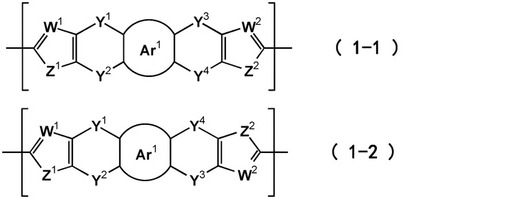

多環縮環化合物、多環縮環重合体及びこれらを含む有機薄膜

【課題】高い電荷輸送性を発揮し得る構造を有するとともに、溶媒への溶解性にも優れる多環縮環重合体を提供すること。

【解決手段】式(1)で表される構造単位を有する多環縮環重合体。 (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】寄生バイポーラトランジスタのゲインを低下することにより、誤動作や動作特性の変動が少ない半導体装置及びその製造方法を得る。

【解決手段】シリコン層3の上面上には、シリコン酸化膜6が部分的に形成されている。シリコン酸化膜6上には、ポリシリコンから成るゲート電極7が部分的に形成されている。ゲート電極7の下方に存在する部分のシリコン酸化膜6は、ゲート絶縁膜として機能する。ゲート電極7の側面には、シリコン酸化膜8を挟んで、シリコン窒化膜9が形成されている。シリコン酸化膜8及びシリコン窒化膜9は、シリコン酸化膜6上に形成されている。ゲート長方向に関するシリコン酸化膜8の幅W1は、シリコン酸化膜6の膜厚T1よりも大きい。

(もっと読む)

分子操作用素子

【課題】分子膜における分子の位置の操作が、より効率的に行えるようにする。

【解決手段】基板101の上に各々絶縁分離して形成された電極131,132と、基板101の上に電極131,132を覆って形成された絶縁層104と、絶縁層104の上に形成された分子膜110とを少なくとも備える。分子膜110は、例えば、二分子膜および単分子膜などである。本実施の形態では、電極131,132の各々が、基板101の上に形成された絶縁層102により絶縁分離されている。

(もっと読む)

含窒素縮合環化合物、含窒素縮合環重合体、有機薄膜及び有機薄膜素子

【課題】優れた電子輸送性を有する有機n型半導体として利用可能であり、有機溶媒への溶解性にも優れる含窒素縮合環化合物を提供すること。

【解決手段】式(1−1)又は式(1−2)で表される構造単位を有する含窒素縮合環化合物。 (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】埋め込み絶縁層により活性層と支持基板とが電気的に絶縁された半導体基板において、支持基板の電位を活性層の表面から取り出すための基板コンタクトの低抵抗化を図ることができる半導体装置およびその製造方法を提供すること。

【解決手段】活性層16に素子領域4およびコンタクト領域5が形成された厚膜SOI基板2において、CMOSトランジスタ7のB/L層29およびL/I層37、npnバイポーラトランジスタ8のコレクタ層49と同一層に、n型基板コンタクト12の貫通コンタクト58を取り囲むn型コンタクト埋め込み層57を形成する。

(もっと読む)

電子装置およびその製造方法

【課題】グラフェンシートを使い、大電流をオンオフできる電子装置を提供する。

【解決手段】電子装置は基板と、前記基板上にゲート絶縁膜を介して形成されたグラフェンシートと、前記グラフェンシートの一端に形成されたソース電極と、前記グラフェンシートの他端に形成されたドレイン電極と、前記グラフェンシートに前記ソース領域とドレイン領域との間でゲート電圧を印加するゲート電極と、前記グラフェンシートに前記ソース電極とドレイン電極の間において、前記ソース電極からドレイン電極へのキャリアの流れを横切って形成された、複数の開口部よりなる開口部列と、を備え、前記各々の開口部では前記グラフェンシートから4個以上の炭素原子が除去されており、前記各々の開口部は、他の炭素原子に結合していない結合手を有する炭素原子を二個以上含む少なくとも5個の炭素原子からなるジグザグ形状の端部により画成されている。

(もっと読む)

141 - 160 / 2,062

[ Back to top ]